File

advertisement

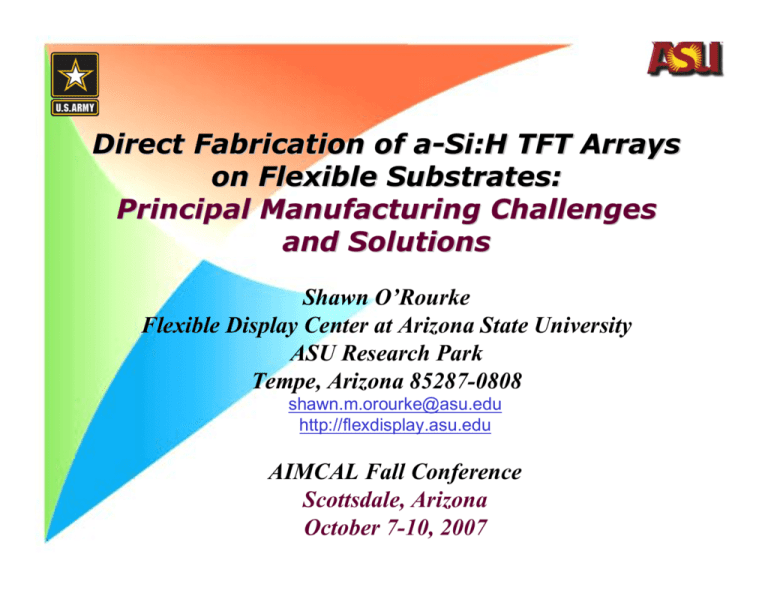

Direct Fabrication of a-Si:H TFT Arrays on Flexible Substrates: Principal Manufacturing Challenges and Solutions Shawn O’Rourke Flexible Display Center at Arizona State University ASU Research Park Tempe, Arizona 85287-0808 shawn.m.orourke@asu.edu http://flexdisplay.asu.edu AIMCAL Fall Conference Scottsdale, Arizona October 7-10, 2007 FDC Outline • FDC Vision, Partnership Model and Technology Focus • Infrastructure Challenges and Solutions 9 Substrate Systems 9 Manufacturing Protocols • TFT Fabrication Challenges and Solutions 9 Baseline low temperature a-Si:H process 9 Managing flexible substrate system limitations and liabilities • Conclusions FDC Flexible Display Center at Arizona State University Est. February 10, 2004 VISION: A National Asset Bringing Together Bestin-Class Partners to Create and Deliver Manufacturable Flexible Display Technology for Military, Security, Commercial and Space Applications Strategic Global Partnership U.S. Army Labs r te Ma Fr on Ba tpl ck an e p Te lan & ch e ls ia s et o ls g To or urin f ct fa nu Ma Flexible Display Center Electronic Materials R& Un Lab D: iv e s & rs it i es FDC System Integrators Princeton NC A&T North Texas UT-Dallas FDC FDC Technology Focus: High Information Content Flexible Displays New capability through Strategically-selected Options Proven in Glass-based Commercial Products Reflective Bi-stable “zero power” Emissive Efficient low power Electrophoretic Ink Phosphorescent OLED Cholesteric Liquid Crystal FDC Outline • FDC Vision, Partnership Model and Technology Focus • Infrastructure Challenges and Solutions 9 Substrate Systems 9 Manufacturing Protocols • TFT Fabrication Challenges and Solutions 9 Baseline low temperature a-Si:H process 9 Managing flexible substrate system limitations and liabilities • Conclusions FDC Flexible Substrate Systems: Infrastructure Challenges and Paths • Flexible substrate system supply infrastructure : Supply chain is underdeveloped and market opportunity unclear for wouldbe suppliers : Requirements incompletely specified ; Work with substrate suppliers to create well-defined and verified specifications • Manufacturing infrastructure : Roll-to-roll toolsets immature ; Adapt existing plate-to-plate toolset infrastructure 8 Free-standing flexible substrates 8 Substrate fixturing / framing 9 Substrate temporary bonding – debonding 9 Substrate coat - release 9 Layer Transfer AKT (US) PECVD plate process tool GEN VII 2.1 x 2.4m substrates FDC Flexible Substrate Systems: Down-selects and Challenges No manufacturing-ready “drop-in” replacements for glass HS-PEN • Process T limit • Dimensional stability • Permeable to O2/H2O: barrier layer(s) HS-PEN Stainless Steel • Limited flexibility • Electrical isolation • Surface roughness: planarization layer SS FDC Manufacturing Protocol Options Bond - Debond Coat – Laser Release Layer Transfer FDC SEC ITRI IBM Philips Thales-LCD PVI Seiko-Epson Sacrificial poly-Si on Carrier Substrate bonded with Temporary Adhesive to Carrier TFT Fabrication 100 – 180 °C Spin-coated Polyimide on Carrier TFT Fabrication 300 – 350 °C TFT Fabrication 280 °C Temporary Substrate bonded with Water-soluble Adhesive Laser Release: Ablation Triggered Debond: Thermal Solvent Light (non-laser) Laser Release: Interfacial Melting Bond to Flexible Substrate then release Temporary FDC Temporary Bonding – Debonding: Manufacturing Challenges • Temporary bonding with semiconductor-grade adhesive 9 9 9 9 Compatible with Si-based TFT devices Low total thickness variation (TTV) Defect (particle/bubble) free TFT and EO process toolset and flow compatible • Automated de-bonding 9 Triggered release (thermal, radiation, chemical) 9 Residue-free 9 Substrate and TFT damage-free Requires integrated substrate/barrier/adhesive/toolset solution FDC Temporary Bonding Pitfalls HS-PEN on Si Blisters form at defect (bubble, particles) sites Exacerbated by adhesive out-gassing at temperature and in vacuum SS on Si “Teacup” failure due to CTE mismatch between flexible substrate and carrier Adhesive mechanical elasticity crucial FDC Critical Enabler: Substrate Bond/De-Bond • Pilot Line Tools • Novel Materials • Manufacturable Processes Bonded substrate After TFT Fab Semiconductor-grade Adhesive Custom Solutions Perfect bond integrity through entire fab Debonded substrate “Triggered” Release No TFT degradation No residue FDC Outline • FDC Vision, Partnership Model and Technology Focus • Infrastructure Challenges and Solutions 9 Substrate Systems 9 Manufacturing Protocols • TFT Fabrication Challenges and Solutions 9 Baseline low temperature a-Si:H process 9 Managing flexible substrate system limitations and liabilities • Conclusions FDC Classic Cyclical Development Program TFT Autoprober FDC Custom Test TFT Performance & Array Yield Integration, Assembly, TFT Array Test Automated Simulation, E-Test Design, Layout, Verification Design Rules for high manufacturing yield Pilot Line Fabrication Fabricated array 4” QVGA Maskset FDC Low Temperature a-Si:H TFT Process Challenges and Approach Glass-based TFTs 300-380 °C. Process Temperatures a-Si:H : higher SiH2/SiH ratio Î higher Vt and lower µsat TFTs on Flex 180 °C. Max Process Temperature Identified New Process Lower Windows: quality Achieved active device equivalent or better materials performance n+ a-Si:H contacts : unactivated dopants Î higher ρ : Unstable interface Î contact barrier a-SiNx:H gate dielectric : higher charge trap density Î greater ∆Vt (stability degradation) and greater hysteresis FDC FDC a-Si:H TFT Performance: Rivals that for Commercial Manufacturers Forward Sweep Reverse Sweep Hysteresis W/L = 96 µm / 9 µm SEC1 Parameter FDC Max. Process Temperature 180 °C 130 °C 370 °C Saturation Mobility (cm2/V-s) 0.9 0.5 0.5 ON/OFF Ratio 2 x 109 1 x 108 4 x 107 Drive Current (µA) 30 1.2 4.0 Threshold Voltage 1.2 V 4.5 V 0.7 V Hysteresis 1.1 V - - 1 P. Shin, USDC Flexible Displays Conference (2007). FDC FDC Technology Solutions: Managing Plastic Substrate Distortion • Thermal cycles Î material run-in Î 400 9 heat stabilize 100 0 -100 E0615-002, X E0616-002-4, X E0616-002-6, X -200 E0615-002, Y E0616-002-4, Y E0616-002-6, Y 400 5 mil X-Distortion Modified Process 300 Original PEN 5 mil Y-Distortion 8 mil X-Distortion 200 Improved PEN 8 mil Y-Distortion 100 0 -100 ITO Align 6 Align 5 Align 4 Align 3 -200 Align 2 • Unique GEN II photolith tool will enable fabrication of larger displays 200 Align 1 Enables Direct Fabrication of 4-in. diagonal displays Distortion (ppm) 9 forgiving design rules 9 modified lower stress processes 9 modified substrate material system Distortion (ppm) • Elastic strain under deposited film stress Î material run-out Î Baseline Process 300 FDC Reduced Run-out Process with DTF Planarized PEN: No distortion compensation Upper right pixel Upper left pixel 3.8-in. QVGA TFT Array Lower left pixel Lower right pixel FDC Flexible QVGA 180 °C a-Si:H AM-EPD on HS-PEN Substrate HS-PEN TFT Array Test 0.19% point defects: 142 shorts, 2 opens 3.8-in. QVGA EPD Display Module Integrated FDC Technology: DTF HS-PEN Substrate System Low T a-Si:H TFT process E Ink Frontplane and Drive 1Q 2007 FDC FDC GEN II Photo-Patterning Cell Qualified 2007 EVG FDC Photoresist Coater World’s First high uniformity mist coater with unprecedented material utilization efficiency Azores 5200 gT Stepper World’s First photolithography tool with flexible substrate distortion compensation FDC FDC Technology Solutions: Manufacturable SS Substrate System 3.8-in. QVGA EPD on SS AFM Micrograph As-received SS Type 430 SS Substrate Low CTE (10.4) Planarized SS Honeywell Low T Planarization Layer National Starch Custom Temporary Adhesive Novel Carrier CTE Matched-to-Substrate Thermo-Mechanical Properties of Sub-system Components are Critical FDC Flexible QVGA 180 °C a-Si:H AM-EPD on SS Substrate SS TFT Array Test 0.48% point defects: 345 shorts, 24 opens 3.8-in. QVGA EPD Display Module Integrated FDC Technology: SS Substrate System USDC-funded NS Temporary Adhesive Honeywell EM Planarization Material Low T a-Si:H TFT process E Ink Frontplane and Drive 1Q 2007 FDC FDC Differentiator: Technology Transition First Product-level Technology Demonstrator 2Q 2007: Ultra-Rugged Personal Digital Assistant • • • • Bluetooth Removable memory Single-hand operation with touch-screen Battery power Product Design Ultra-rugged FDC 3.8” QVGA EPD Display Module Lightweight Ultra-low power No light signature Delivered Demo Sunlight-to-starlight readable FDC Conclusions • The FDC has created the partnership framework, innovation capability and physical infrastructure to enable rapid development and integration of flexible display technology • Critical path in flexible TFT backplane technology development 9 Flexible substrate system technology and supply chain under development 9 Manufacturable bond-debond technology development 9 Baseline low temperature a-Si:H process developed on 6” Pilot Line producing quality transistor arrays with reasonable yields 9 Managing plastic substrate distortion and SS CTE and roughness to produce reasonable quality technology demonstrators 9 GEN II Pilot Line on track for 2007 a-Si:H process qualification (~80% at this time) FDC Acknowledgements • ASU and The Flexible Display Center gratefully acknowledge the substantial financial support of the U.S. Army through Cooperative Agreement W911NF-04-2-0005 9 Dr. David A. Morton, ARL, Cooperative Agreement Manager 9 Mr. Henry Girolamo, U.S. Army NSC, Associate PM Integration 9 Dr. Eric Forsythe, ARL, Associate PM Technology • FDC Principal Members: EV Group, UDC, USDC • FDC Associate Members: E Ink, Kent Displays, Honeywell, Hewlett-Packard, Ito America, Abbie Gregg, Inc., Surface Science Integration, Litrex, DuPont Teijin Films, EITI • FDC Technology User Members: General Dynamics, Raytheon, L-3 Communications FDC Key Technical Contributors • ASU Pilot Line Operations Team ¾ Shawn M. O’Rourke, Curt Moyer, Barry P. O’Brien, Scott K. Ageno, Douglas E. Loy, Ed Bawolek, Dirk Bottesch, Jeff Dailey, Ke Long, Michael Marrs, Nick Munizza, Steve Rednour, Rob Blanchard, Jovan Trujillo, Hanna Heikkinen • ASU Display Engineering Team ¾ Jann Kaminski, David Allee, Sameer Venugopal, Rita Cordova • Flex EPD Project Team ¾ ¾ ¾ ¾ Dr. Michael McCreary, Holly Gates and Guy Danner at E Ink Andrew Girson, Marc Carlson, Mark Price and Dan Rowland at InHand Darwin Keith-Lucas at Artisent Andy Taylor, Henry Girolamo and Dennis Magnifico at NSRDEC FDC Key Technical Contributors • FDC Member Teams: Processes and Manufacturing 9 Dr. Keith Rollins, Bill MacDonald, and colleagues at DuPont Teijin Films for collaboration on display-quality plastic substrates 9 Dr. Steven Dwyer, Dr. Thorsten Matthias and colleagues at EVG for collaboration on bond-debond technology 9 Eric Thran at Ito America for collaboration on TAB bonding and display assembly 9 Prof. Sigurd Wagner, Prof. Jim Sturm and colleagues at Princeton University for collaboration on a-Si TFT processes and device evaluation 9 Dr. Pete Smith and colleagues at Honeywell Electronic Materials for collaboration on SS planarization 9 Bob Pinnel and colleagues/members at USDC for funding and managing technology development projects that contribute to the FDC mission FDC Thank You!