High Speed Interface Applications: Presentation

advertisement

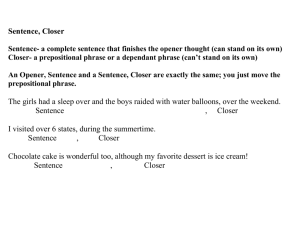

High Speed Interface for Various Applications <Contents> I. Overview II. Interface Basics III. Applications IV. Closer Look V. Conclusion 2011. 4.27 LG Electronics / Kirt Hong Great Company Great People 1. Overview • Why High Speed Interface? • Evolution of Interface Standard 1. Overview Why High Speed Interface? • Current system performance is hampered by Inter-Component Interface rather than Intra-Chip Technology. 1) Chip-to-Chip Interface 2) Board-to-Board Interface 3) Box-to-Box Interface 4) Memory Interface 1) 4) 2) 4) HDD 3) 3) 1. Overview Why High Speed Interface? • Bigger display and higher resolution drastically increase the pixel data to be transmitted over cables. 640 480 VGA 1280 720 HD 1920 1080 3840 FHD 2160 X3 4K x 2K X2.25 X4 If LVDS, lane count (10-bit, 120Hz) is 12 lanes Too Many!! 24 lanes 96 lanes 1 lane = 2 lines 1. Overview Evolution of Interface Standard PATA first appeared in Compaq PC (1986) First SATA introduced (2003) Market starts to adopt USB (1998) PCIe replaced PCI & AGP (2004) DP introduced (2006) eDP released (2008) 1995 2000 2005 2010 LVDS introduced (1994) DVI introduced (1999) LCD panel uses Mini-LVDS (2001) Vx1 HS released (2008) iDP approved (2010) DVI evolved to HDMI (2002) MIPI alliance formed (2003) Qualcomm developed MDDI (2004) CE interface Mobile Interface PC Interface 1. Overview Lane Speed (Gbps) Data Rate Comparison between Various Interface Standards WiGig Wired External I/F Wired Internal I/F Wireless External I/F 6 DP 5 DiiVA WirelessHD Vx1 HS 4 HDMI iDP 3 2 WHDI HS LVDS UWB 1 WiFi Application Great Company Great People 2. Interface Basics • “Am I wide enough?” • “How do I look?” • “Where is my Clock?” • “What’s the matter?” • “Let’s make it faster!” 2. Interface Basics “Am I wide enough?” Parallel vs. Serial Familiar and quickly implemented Much higher speed Fast reaction time No skew : Longer distance No Link layer required Clock embedded in data Source synchronous clock required Reduction of signal line counts Skew between data lines Heavy Link layer Data Data TX Clock Data Data RX Clock Data TX Clock Clock Data w/ Clock RX Clock 2. Interface Basics “How do I look?” Network Topologies Point-to-Point Multi-drop Multipoint Single TX & Single RX Single TX & Multiple RX Multiple TX & Multiple RX HDMI, DisplayPort M-LVDS, B-LVDS M-LVDS, B-LVDS TX TX RX3 TX1 RX3 RX RX1 RX2 RX1 RX2 TX2 TX3 2. Interface Basics Explicit Clock “Where is my Clock?” vs. Embedded Clock Intuitive Implicit Setup/Hold window check Eye diagram check Clock Skew to data Free from skew problem Easy Physical layer design Routing flexibility Ex) LVDS Extra encoding required (ex, 8b10b) Clock Recovery circuit required Ex) DisplayPort Clock Data Data + Clock 2. Interface Basics “What’s the matter?” Speed Limiting Factors Capacitive Loading from pad and lead frame Reflection from Transmission Line Discontinuity Attenuation from Dielectric Loss Crosstalk caused by adjacent signal line Timing Skew between parallel signals Simultaneous Switching Noise (SSN) Inter-Symbol Interference (ISI) 2. Interface Basics “Let’s make it faster!” To Increase the Data Rate Differential signaling Pre-emphasis and Equalization Before Equalization After Equalization Point-to-Point Topology rather than Multi-drop Topology Capacitive Coupling control Great Company Great People 3. Applications • Digital TV • Mobile • PC • Wireless 3. Applications Digital TV External Interface : HDMI, DP, DIIVA Internal Interface : HS-LVDS, iDP, V-by-One HS Panel Interface : Mini-LVDS, EPI Panel DIC Panel Interface It may be one-chip External Interface CE Main SoC Internal Interface Internal Interface FRC / 3D TCON 3. Applications Mobile MIPI Interface RF DigRF DSI BB Display Driver DSI Camera Driver CSI Display LLI WLAN UniPort CSI AP CIS SLIMbus Speaker UFS Mass Storage SPMI UniPort (UniPro + D-PHY/M-PHY) PMU DSI (Display Serial Interface) CSI (Camera Serial Interface) SPMI (System Power Management Interface) SLIMbus (Serial Low-power Inter-chip Media Bus) LLI (Low Latency Interface) / BIF (Battery Interface) BIF Mic. Ear Piece FM Radio Battery BlueTooth GPS 3. Applications PC FSB (Front Side Bus) AGP (Accelerated Graphics Port) SATA (Serial Advanced Technology Attachment) PCI (Peripheral Component Interconnect) PCIe (PCI Express) Graphics AGP PCIe SATA HDD CPU FSB Memory Control (Northbridge) DDR2 DDR3 DRAM PCIe I/O Control (Southbridge) Local I/O USB USB port PCIe PCI Mobile Ducking Gigabit Ethernet Add-on Card PCI slots 3. Applications Wireless How They Are Connected Network Monitor How to travel Laptop Mobile TV P2P STB PDA Printer Tablet Photo Frame PC Wired PLC MoCA Game NAS Tablet Cellphone BDP Camera PLC (Power Line Communication) MoCA (Multimedia over Coax Alliance) NAS (Network Attached Storage) Wireless Great Company Great People 4. Closer Look • Box-to-Box Interface • Chip-to-Chip Interface • Memory Interface • Wireless Interface • Optical Link Interface 4. Closer Look Box-to-Box Interface HDMI • • • • • Initial release in 2002; Currently HDMI 1.4 released in 2009 Industry de facto standard for Consumer Electronics Networking feature added (LiquidHD) Companion Interface Standard introduced (MHL, SPMT) Needs royalty / licensing fee Network CE TV Mobile TV1 Home Theater TV2 HDMI (High-Definition Multimedia Interface), MHL (Mobile High-definition Link), SPMT (Serial Port Memory Technology) 4. Closer Look Box-to-Box Interface DisplayPort (DP) • • • • • Initial released by VESA in 2006; currently DP 1.2 in 2010 Intended for both External and Internal interfaces Open standard; royalty-free Several Derivatives : eDP, iDP, tDP PC & Monitor application External Interface CE Internal Interface Monitor Graphics TCON VESA (Video Electronics Standards Association), eDP (Embedded DP), iDP (Internal DP), tDP (TCON DP) Panel 4. Closer Look Box-to-Box Interface DIIVA (also known as DIVA) • Initial released by DIIVA Consortium in 2009 • Originally designed for Home Entertainment Networking : Unification of 3 packet types (Video, Data, Power Control) • Flexible connection (Daisy Chain or Switch configuration) • Operating over standard Ethernet cable • Under promotion DIIVA Daisy Chain CAT6A DIIVA (Digital Interactive Interface for Video and Audio), DIVA (Digital Interface for Video and Audio) DIIVA Switch 4. Closer Look Comparison HDMI DisplayPort DIIVA First Release 2002 2006 2009 Current version HDMI 1.4 DP 1.2 DIIVA 1.0a Controlling Authority HDMI LLC VESA DIIVA Promoter Content Protection HDCP DPCP / HDCP HDCP / DTCP-IP Bit rate / pair Up to 3.4Gbps 1.62/2.7/5.4Gbps 4.5Gbps Max. total capacity 10.2Gbps 21.6Gbps 13.5Gbps No. of clock ch. 1 0 0 No. of video ch. 3 1/2/4 3 AUX channel DDC AUX Hybrid Link Channel coding TMDS 8b/10b 8b/10b Major Application TV Monitor Home Networking Ethernet 100Mbps 720Mbps Gigabit USB No Yes Yes Remarks Bidirectional Power Over DIIVA Great Company Great People 4. Closer Look • Box-to-Box Interface • Chip-to-Chip Interface • Memory Interface • Wireless Interface • Optical Link Interface 4. Closer Look Chip-to-Chip Interface Categorization of Internal Interface • TCON Interface : LVDS, HS-LVDS, iDP, V-by-One HS • Panel Interface : Mini-LVDS, EPI, MIPI, MDDI Large Panel Small Panel Driver ICs Driver ICs Panel Interface TCON Interface Graphics TCON Panel Interface TCON 4. Closer Look Chip-to-Chip Interface LVDS • • • • Introduced by ANSI/TIA/EIA-644 in 1994 Low voltage swing (350mV) and DC-balancing Data Rate : 7X the original pixel clock Various LVDS Technologies : LVPECL, CML, MLVDS, BLVDS, HS-LVDS LVPECL Power Consumption CML LVDS 100M 1G 3G 5G Data Rate (bps) 10G LVDS (Low-Voltage Differential Signaling) LVPECL (Low-Voltage Positive-Emitter-Coupled Logic) CML (Current Mode Logic) MLVDS (Multipoint LVDS) BLVDS (Bus LVDS) HS-LVDS (High Speed LVDS) 4. Closer Look Chip-to-Chip Interface iDP (Internal DisplayPort) • • • • Initial released by VESA in 2010 Open standard led by LG Display and STM Targeted for interconnecting TV/Monitor SoC and TCON Only video data transfer by leveraging the DP technology LVDS Interface iDP Interface Fixed Rate (3.24Gbps) FRC TCON 48 lanes for FHD 240Hz TCON FRC 8 lanes for FHD 240Hz 4. Closer Look Chip-to-Chip Interface V-by-One HS • • • • Authority to control standard belongs to THine Removed Link Logic by Variable bit rate Used for LCD TCON interface Needs no royalty / licensing fee LVDS Interface V-by-One HS Interface Variable Rate (~3.75Gbps) FRC TCON 48 lanes for FHD 240Hz TCON FRC 8 lanes for FHD 240Hz 4. Closer Look TCON Interface Comparison LVDS iDP V-by-One HS First Release 1994 2010 (V1.0) 2008 (V1.0) Current version - V1.0 2010 (V1.3) Controlling Authority ANSI/TIA/EIA-644 VESA THine Bit rate / pair ~ 1.12Gbps 3.24Gbps 0.6Gbps ~ 3.75Gbps Explicit clock Yes No No No. of data ch. 4~6 1 ~ 16 lanes/bank 1,2,4,8,16,32 … AUX channel No HPD HTPDN, LOCKN Scrambling No Yes Yes Channel coding No 8b/10b 8b/10b Major Application FRC & TCON I/F TCON I/F TCON I/f Lane count for FHD2401) 48 8 8 Lane count for Cinema2402) 48 93) 8 1) 1920 x 1080 resolution 2) 2560 x 1080 resolution 3) With reduced Black period or higher data rate than 3.24Gbs, this could be 8-lane. 4. Closer Look Chip-to-Chip Interface Mini-LVDS • Released by Texas Instrument Inc. • Internal interface between Flat Panel TCON and Column Drivers • Retains the benefits of the LVDS interface Video Data TCON Row Driver Column Driver 4. Closer Look Chip-to-Chip Interface Next Mini-LVDS • • • • Point-to-Point connection between TCON and Panel High Speed up to 1.8Gbps/pair No data skew and better EMI margin Requires fewer lines than Mini-LVDS Mini-LVDS Interface Next Interface (Data 6-pair & Clock 1-pair) *2 = 28 pins TCON Panel FHD (10b) 120Hz Data 6-pair = 12 pins TCON Panel FHD (10b) 120Hz 4. Closer Look Chip-to-Chip Interface MDDI • Developed by Qualcomm & approved by VESA in 2004 • High-speed, bidirectional data transfer up to 3.2Gbps • Multiple data types simultaneously in both directions (e.g., Video, Audio, Control data, Keyboard, Pointing device) Initial Concept at Qualcomm 2000 2001 1st Proto Development 2002 2nd Proto Development 2003 VESA MDDI SIG created MDDI Spec. freeze VESA MDDI WG created MDDI becomes a VESA standard 2004 MDDI (Mobile Display Digital Interface), SIG (Special Interest Group), WG (Working Group) 4. Closer Look Chip-to-Chip Interface MIPI • MIPI alliance founded in 2003 by ARM, Nokia, STM, and TI • Open standard to define/promote for interfaces inside mobile devices Interface Standard CSI MIPI Working Group (WG) D-PHY Camera WG PHY Layer WG DigRF DDB DigRFSM DSI DPI DBI WG PLF WG Display WG SPM WG HSI WG Test & Debug WG LML WG UniProSM WG SPMI HSI SLIMbus Interface Standard System Trace Protocol Spec. Processor I/F Emulation MIPI (Mobile Industry Processor Interface), HSI (High-speed Synchronous Interface), LML (Low-speed Multipoint Link), CML (Current Mode Logic), PLF (Peripheral and interconnect Low-level Framework), SPM (System Power Management) 4. Closer Look Controlling Authority PHY spec. Data Link Count Panel Interface Comparison MDDI MIPI VESA MIPI organization One comprehensive spec. Separately defined spec. One PHY architecture : Unidirectional with reverse data flow Type 1 : 1 lane Type 2 : 2 lanes Type 3 : 4 lanes Type 4 : 8 lanes Multiple PHY configuration : Unidirectional, Bidirectional, High speed, and Low power No link limit (4 data link recommended) Implementation Preference Diff. Current Mode Driver Diff. Voltage Mode Driver Protocol One Protocol Document with Multiple Packet Definition Separate Protocol Layers (Camera, Display, UniPro) Market Focus CDMA GSM Remarks Longer Silicon History Great Company Great People 4. Closer Look • Box-to-Box Interface • Chip-to-Chip Interface • Memory Interface • Wireless Interface • Optical Link Interface 4. Closer Look Memory Interface DDR • Data Transfer on both clock edges (Rising/Falling) • Started in Graphic cards • Win against Intel’s Rambus • MDDR for mobile application DDR2-800 DRAM Data I/O Prefetch 200MHz Bus 400MHz 400MHz 800MHz DDR3-800 DRAM Data I/O Prefetch 100MHz Bus 400MHz 400MHz DDR SDRAM Freq. (MHz) DDR 100 - 200 DDR2 200 - 533 DDR3 400 - 1600 800MHz DDR3-1600 DRAM Prefetch 200MHz Data I/O Bus 800MHz 800MHz 1600MHz DDR (Double Data Rate), MDDR (Mobile DDR) 4. Closer Look Memory Interface PCIe • Computer expansion card standard, introduced in 2004, replacing the older PCI, PCI-X, and AGP PCIe AGP • Intel • 32-bit (Parallel) • ~2133MB/s PCI-X PCI 1993 • Intel/Dell/IBM/HP • 1~32-bit (Serial) • PCIe 1.0a : 250MB/s • PCIe 2.0 : 500MB/s • PCIe 3.0 : 1GB/s • IBM/HP/Compaq • 64-bit (Parallel) • 1064MB/s • Intel • 32/64-bit (Parallel) • 133~533MB/s 1998 2004 2010 PCIe (Peripheral Component Interconnect Express), AGP (Accelerated Graphics Port) 4. Closer Look Memory Interface USB • Introduced by Intel in 1996 • High-speed, easy connections of peripherals to PCs 5Gbps SuperSpeed USB 3.0 480Mbps Hi-Speed USB 2.0 Earliest version to be widely adopted 1st certified USB 3.0 product announced USB OTG 12Mbps USB 1.1 USB 1.0 1996 1998 2000 2002 2008 2010 USB (Universal Serial Bus), OTG (On-The-Go) 4. Closer Look Memory Interface SATA • Computer bus interface for connecting a host bus adapter to mass storage devices, replacing PATA • Host mode and Device mode supported (“Host Swapping”) • Variants : eSATA, eSATAp Host HDD SATA ODD SATA HDD eSATA Port Multiplier External HDD HDD SATA HDD eSATA Flash Memory HDD SATA (Serial Advanced Technology Attachment), PATA (Parallel ATA), eSATA (External SATA), eSATAp (External SATA with Power), HDD (Hard Disk Drive), ODD (Optical Disk Drive) 4. Closer Look Comparison DDR USB PCIe SATA First version DDR1 USB1.0 PCIe Gen1 SATA1.0 Current version DDR3 USB3.0 PCIe Gen3 SATA3.0 Controlling Authority JEDEC USB organization - SATA-IO Bit rate / pair 1.6Gbps 5.0Gbps @ super speed 8.0Gbps @ Gen3 6.0Gbps @ Rev3 No. of clock ch. 1pair/8data No No No No. of data ch. 16, 32 2 pairs 4 pairs (TX) 4 pairs (RX) 1 pair (TX) 1 pair (RX) Channel coding No 8b/10b 128b/130b 8b/10b Major Application DRAM Interface Universal Graphic card interface @ PC Hard Disk, SSD interface SATA-IO (SATA International Organization) Great Company Great People 4. Closer Look • Box-to-Box Interface • Chip-to-Chip Interface • Memory Interface • Wireless Interface • Optical Link Interface 4. Closer Look Wireless Interface WirelessHD • • • • • First 60 GHz band technology developed by SiBEAM LG announced WirelessHD TV in CES2008 4Gbps data rate (theoretically 25Gbps) in a 7GHz channel Uncompressed, lossless FHD video, audio and data transmission Smart antenna technology for non-line-of-sight (NLOS) transmission Media Box WirelessHD TX TV LRP signal for control WirelessHD RX HRP signal for A/V data LRP (Low Rate PHY), HRP (High Rate PHY) 4. Closer Look Wireless Interface WiGig • Announced in 2010 by Wireless Gigabit Alliance • Operating over the unlicensed 60 GHz band • WiGig tri-band operates in the 2.4, 5 and 60 GHz bands thru liaison w/ WiFi Alliance, delivering 7Gbps data rate WiFi (600Mbps) WiGig (7Gbps) WiGig or WiFi WiGig & WiFi Compatibility WiGig (Wireless Gigabit Alliance) 4. Closer Look Wireless Interface WHDI • • • • 5 GHz band technology LG announced WHDI wireless TV in CES2010 Range of 100+ feet, through walls and obstacles 3Gbps for 1080p in a 40MHz channel or 1.5Gbps for 1080i and 720p in a 20MHz channel Wall Living room Bed room 1 2nd Floor Wall Bed room 2 WHDI 3Gbps Bed room 3 Kitchen 1st Floor WHDI 1.5Gbps WHDI (Wireless Home Digital Interface) 4. Closer Look Wireless Interface UWB • • • • WiMedia 1.1 and 1.5 International standards : ECMA and ISO Highest throughput, low power wireless technology for video & data 3-10GHz UWB spectrum is untapped Better battery life, Small, Low cost, & High density Power Existing Narrow Band Signals UWB Frequency Band 2.4GHz 3.1GHz 5GHz 10.6GHz UWB (Ultra-WideBand) Freq. Great Company Great People 4. Closer Look • Box-to-Box Interface • Chip-to-Chip Interface • Memory Interface • Wireless Interface • Optical Link Interface 4. Closer Look Optical Link Interface Silicon Photonics • • • • Fiber to the silicon chip for high speed communication Luxtera : First commercial optical cable product for 40Gbps (2009.10.) Intel : 50Gbps Silicon Photonics link with Integrated Lasers (2010.7.) ETRI : New device for 100% Ge on Silicon optical receiver (2010.7.) HDMI/DP/DIIVA ( 3~5Gbps ) Optical Optical Cable ( 40~50Gbps ) 4. Closer Look Optical Link Interface Silicon Photonics • • • • Future chip : 1000 Gbps with laser-based communication (Intel) Fiber-optic cabling : large-bandwidth, long-distance, slim and small Difficulty to make optical source using only Silicon (CMOS) Poor cost competitiveness and few applications up to now Incoming electrical data stream Hybrid Laser Modulator Hybrid Laser Modulator Hybrid Laser Modulator Hybrid Laser Modulator Connector 110100111 … Mux Integrated Transmitter Die Fiber Optic Cable Reproduced electrical data stream Photo Det. DeMux Photo Det. 110100111 … Photo Det. Photo Det. Integrated Receiver Die Great Company Great People 5. Conclusion 5. Conclusion Future Trend As Digital TV becomes the Home Entertainment (HE) Network Hub to interconnect and control the CE equipments, External CE Interface should build and manage the HE Network. Current high resolution and high frame rate display will require TCONpanel interface speed to be accelerated with moderate H/W and space, getting high speed serial interface popular. PC interface keep adopting clock-embedded serial interface technology, realizing high speed transfer rate and compact design. 5. Conclusion Implication & Chance The latest High Speed I/F standards create new market demand in the area of Home Entertainment, Display device manufacturing, Mobile device industry, and PC industry. Leading development and forward deployment of I/F IP is MUST for successful business, due to the tough competition between similar I/F standards and uncertainty from market dynamics. The Gigabit Wireless Interface enables seamless interconnection without "spaghetti wires”, and Silicon photonics can be a good candidate of next generation interface over 1Tbps. http://www.lge.com