ECE 463/521 Overview

advertisement

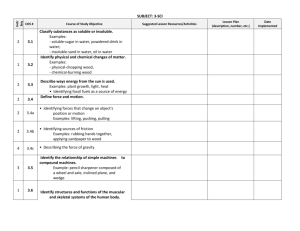

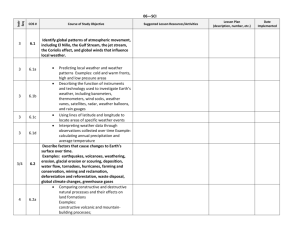

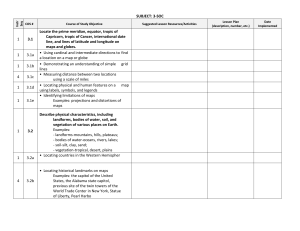

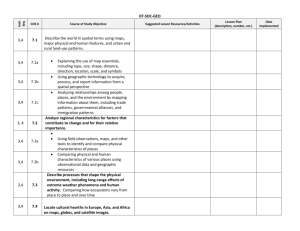

ECE 463/521 Overview Prof. Eric Rotenberg © 2008, Rotenberg ðComputer Architecture & Systems ðComputer Architecture ðProcessor Architecture (CPU, microprocessor) Hard: Correct & Fast CPU Easy: Correct CPU © 2008, Rotenberg 1 Simple Processor Pipeline Register File 1 IF (instr. fetch) ID EX MEM WB (instr. decode) (execute) (memory) (writeback) Memory (DRAM & Disk) © 2008, Rotenberg Invention #1 Pipelining Register File 234561 IF (instr. fetch) ID EX MEM WB (instr. decode) (execute) (memory) (writeback) Memory (DRAM & Disk) © 2008, Rotenberg 2 Problem: Dependent Instructions Register File 234561 IF (instr. fetch) ID EX MEM WB (instr. decode) (execute) (memory) (writeback) Memory (DRAM & Disk) © 2008, Rotenberg Data Bypasses Invention #2 Register File 234561 IF (instr. fetch) ID EX MEM WB (instr. decode) (execute) (memory) (writeback) Flea-Flicker! Memory (DRAM & Disk) © 2008, Rotenberg 3 Problem: Branch Decisions Register File 2 ? 2 1 IF (instr. fetch) ID EX MEM WB (instr. decode) (execute) (memory) (writeback) Memory (DRAM & Disk) © 2008, Rotenberg Invention #3 Branch Prediction Register File 342 ? 2 Branch Predictor 1 IF (instr. fetch) ID EX MEM WB (instr. decode) (execute) (memory) (writeback) Memory (DRAM & Disk) © 2008, Rotenberg 4 Problem: “Memory Wall” Register File Branch Predictor IF (instr. fetch) ID EX MEM WB (instr. decode) (execute) (memory) (writeback) Memory (DRAM & Disk) © 2008, Rotenberg Invention #4 Caches Register File Branch Predictor IF (instr. fetch) ID EX MEM WB (instr. decode) (execute) (memory) (writeback) Instr. Cache Data Cache Memory (DRAM & Disk) © 2008, Rotenberg 5 Caches (cont.) • Locality of reference – Temporal locality: If you access an item, likely to access it again in near future – Spatial locality: If you access an item, likely to access a nearby item in the near future © 2008, Rotenberg Problem: Stalled Instructions Register File Branch Predictor 4 IF (instr. fetch) 3 ID 2 EX 1 MEM WB (instr. decode) (execute) (memory) (writeback) Instr. Cache cache miss Data Cache Memory (DRAM & Disk) © 2008, Rotenberg 6 Out-of-Order Execution Invention #5 Register File Branch Predictor 5674 IF (instr. fetch) 3 ID 2 (instr. decode) 1 EX MEM WB (execute) (memory) (writeback) Dynamic Scheduler Instr. Cache Data Cache cache miss Memory (DRAM & Disk) OOO EXECUTION SUPPORT . R.F R.F .B YP AS SE S © 2008, Rotenberg PA BY L1 Instr. Cache BRANCH PREDICTION S SSEL1 Data Cache © 2008, Rotenberg 7 What is “Computer Architecture”? Application Operating System Compiler Firmware Instr. Set Proc. I/O system Instruction Set Architecture Datapath & Control Digital Design Circuit Design Layout • Coordination of many levels of abstraction • Under a rapidly changing set of forces • Design, Measurement, and Evaluation © 2008, Rotenberg What is Computer Architecture? Computer Architecture = Instruction Set Architecture + Machine Organization -- Capabilities & Performance Characteristics of Principal Functional Units (FUs) – (e.g., Registers, ALUs, Shifters, -- Data Types: Logic Units, ...) Encodings & Representations -- Ways in which these components are -- Instruction Set interconnected -- Information flows between components -- Instruction Formats -- Logic and means by which such information -- Modes of Addressing and Accessing flow is controlled Data and Instructions -- Choreography of FUs to realize the ISA -- Exceptional Conditions © 2008, Rotenberg -- Register Transfer Level (RTL) Description -- Organization of Programmable Storage (Registers, Memory) 8 Role of Architecture • Responsible for hardware specification: – Instruction set design • Also responsible for structuring the overall implementation – Microarchitecture design • Interacts with everyone – Mainly compiler and logic/circuit level designers • Cannot do good job without knowledge of both sides © 2008, Rotenberg Overview of Topics in 463/521 1. Measuring Performance and Cost 2. Caches and Memory Hierarchies 3. Instruction-Set Architecture (ISA) – Defines software/hardware interface 4. Simple Pipelining – – – Data and control (branch) dependences Data bypasses Branch prediction © 2008, Rotenberg 9 Overview of Topics in 463/521 5. Complex Pipelining and Instruction-Level Parallelism (ILP) – – – – Data hazards Dynamic instruction scheduling, register renaming, Tomasulo’s algorithm Precise Interrupts Superscalar, VLIW, and vector processors © 2008, Rotenberg Projects • Three projects – Cache simulator – Branch predictor simulator – Dynamic instruction scheduling pipeline simulator • Programming for projects is harder than anything many of you have encountered before © 2008, Rotenberg 10 Course Grading • Breakdown – 40% projects – 10% homeworks (approx. 4 to 6 homeworks) – 25% Midterm • Covers Performance/Cost, Caches, ISA, and Simple Pipelining (including branch prediction) – 25% Final • Comprehensive • Majority covers Complex Pipelining and ILP © 2008, Rotenberg Course Web Page • Two identical pages – www.courses.ncsu.edu/ece521 – www.courses.ncsu.edu/ece463 • Contains contact info., office hours, syllabus, assignment/project handouts, etc. • Check frequently © 2008, Rotenberg 11