Chapter 5

Boolean Algebra and

Combinational Logic

CHAPTER OBJECTIVES

Upon successful completion of this chapter, you will be able to:

Explain the relationship between the Boolean expression, logic diagram, and truth table

of a logic gate network and be able to derive any one from either of the other two.

Draw logic gate networks in such a way as to cancel out internal inversions automatically

(bubble-to-bubble convention).

Write the sum of products (SOP) or product of sums (POS) forms of a Boolean equation.

Use rules of Boolean algebra to simplify the Boolean expressions derived from logic

diagrams and truth tables.

Apply the Karnaugh map method to reduce Boolean expressions and logic circuits to their

simplest forms.

Use a graphical technique based on DeMorgan equivalent gates to simplify logic diagrams.

Apply analysis tools to convert word problems to Boolean equations for the purposes

of logic circuit design.

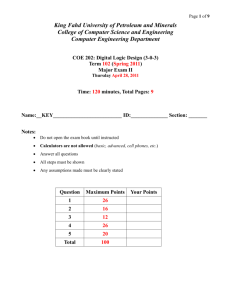

Copyright 2011 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

60001_ch05_Rev03.inddxiv102

60001_FM_rev03.indd

8/10/11 1:14

8/19/11

2:58 PM

PHOTO: © iSOCKPHOTO.COM/KATE_SEPT2004.

he more digital components, or gates, we use

inside of a circuit, the more helpful it might

be to simplify the circuit. You have seen this

in math class before; if you have a choice between

working with a long, complex form of an equation or

a simplified equation, you would probably pick the

simplified version. We can think of digital circuits in

the same way. If we design a big, complicated circuit

and then have to build it, it would sure be nice if

the circuit could be simplified! We can use rules very

similar to algebra to simplify equations, and to simplify circuits.

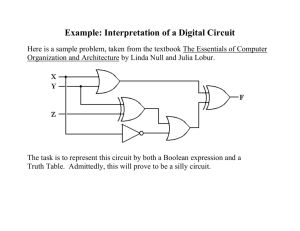

In Chapter 5, we will examine the basics of combinational logic. A combinational logic circuit is one

in which two or more gates are connected together

to combine several Boolean inputs. These circuits can

be represented several ways: as a logic diagram, truth

table, or Boolean expression.

T

A Boolean expression for a network of logic gates is

often not in its simplest form. In such a case, we may

be using more components than would be required for

the job, so it is of benefit to us if we can simplify the

Boolean expression. Several tools are available to us,

such as Boolean algebra and a graphical technique

known as Karnaugh mapping. We can also simplify the

Boolean expression by taking care to draw the logic

diagrams so as to automatically eliminate inverting

functions within the circuit.

One goal in the design of combinational logic circuits is to translate word problems into gate networks

by deriving Boolean expressions for the networks.

Once we have a network’s Boolean expression, we can

apply our tools of simplification and circuit synthesis

to complete our design. We will examine a general

method of analysis that allows us to derive that initial

descriptive equation.

103

Copyright 2011 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

60001_ch05_Rev03.inddxiv103

60001_FM_rev03.indd

8/10/11 1:14

8/19/11

2:58 PM

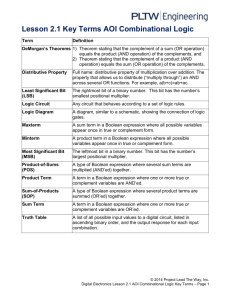

5.1 BOOLEAN EXPRESSIONS, LOGIC DIAGRAMS,

AND TRUTH TABLES

KEY T ERMS

Logic gate network Two or more logic gates connected together.

Logic diagram A diagram, similar to a schematic, showing the connection of

logic gates.

Combinational logic Digital circuitry in which an output is derived from the

combination of inputs, independent of the order in which they are applied.

Combinatorial logic Another name for combinational logic.

Sequential logic Digital circuitry in which the output state of the circuit

depends not only on the states of the inputs, but also on the sequence in which

they reached their present states.

In Chapter 4, we examined the functions of single logic gates. However, most digital circuits require multiple gates. When two or more gates are connected together,

they form a logic gate network. These networks can be described by a truth table,

a logic diagram (i.e., a circuit diagram), or a Boolean expression. Any one of these

can be derived from any other.

A digital circuit built from gates is called a combinational (or combinatorial)

logic circuit. The output of a combinational circuit depends on the combination

of inputs. The inputs can be applied in any sequence and still produce the same

result. For example, an AND gate output will always be HIGH if all inputs are

HIGH, regardless of the order in which they became HIGH. This is in contrast to

sequential logic, in which sequence matters; a sequential logic output may have

a different value with two identical sets of inputs if those inputs were applied in a

different order. We will study sequential logic in a later chapter.

Boolean Expressions from Logic Diagrams

KEY T ERMS

Bubble-to-bubble convention The practice of drawing gates in a logic diagram

so that inverting outputs connect to inverting inputs and noninverting outputs

connect to noninverting inputs.

Order of precedence The sequence in which Boolean functions are performed,

unless otherwise specified by parentheses.

Writing the Boolean expression of a logic gate network is similar to finding the

expression for a single gate. The difference is that in a multiple gate network, the

inputs will usually not consist of single variables, but compound expressions that

represent outputs of previous gates.

These compound expressions are combined according to the same rules as

single

variables. In an OR gate, with inputs x and y, the output will always be x 1

FIGURE 5.1 Boolean Expression

y regardless of whether x and y are single variables (e.g., x 5 A, y 5 B, output 5

from a Logic Gate Network

A 1 B) or compound expressions (e.g., x 5 AB, y 5 AC, output 5 AB 1 AC).

AB

A

Figure 5.1 shows a simple logic gate network, consisting of a single AND

B

Y 5 AB 1 C

and a single OR gate. The AND gate combines inputs A and B to give the

C

output expression AB. The OR combines the AND function and input C to

yield the compound expression AB 1 C.

© CENGAGE LEARNING 2012.

104

Digital Electronics

Copyright 2011 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

60001_ch05_Rev03.inddxiv104

60001_FM_rev03.indd

8/10/11 2:58

8/19/11

1:14 PM

Example 5.1

Derive the Boolean expression of

the logic gate network shown in

Figure 5.2a.

FIGURE 5.2 Example 5.1: Boolean

Expression from a Logic Gate Network

Note . . .

Recall the basic form of

DeMorgan’s rule:

A

B

Y

A?B5A1B

A1B5A?B

C

D

a. Logic gate network

A

AB

B

C

Y 5 AB 1 CD

CD

D

Y 5 AB 1 CD

b. Boolean expression from logic gate network

© CENGAGE LEARNING 2012.

Solution

Figure 5.2b shows the gate

network with the output terms

indicated for each gate. The AND

and NAND functions are combined in an OR function to yield

the output expression:

The Boolean expression in Example 5.1 includes a NAND function. It is possible to draw the NAND in its DeMorgan equivalent form. If we choose the gate

symbols so that outputs with bubbles connect to inputs with bubbles, we will not

have bars over groups of variables, except possibly one bar over the entire function. In a circuit with many inverting functions (NANDs and NORs), this results

in a cleaner notation and often a clearer idea of the function of the circuit. We will

follow this notation, which we will refer to as the bubble-to-bubble convention,

as much as possible. A more detailed treatment of the bubble-to-bubble convention follows in Section 5.5 of this chapter.

Example 5.2

Redraw the circuit in Figure 5.2 to conform to the bubble-to-bubble convention. Write the Boolean expression of the new logic diagram.

Solution

Figure 5.3 shows the new circuit.

The NAND has been converted to

its DeMorgan equivalent so that

its active-HIGH output drives an

active-HIGH input on the OR gate.

The new Boolean expression is

Y 5 AB 1 C 1 D

FIGURE 5.3 Example 5.2: Using

DeMorgan Equivalents to Simplify

the Boolean Expression of a Logic

Gate Network © CENGAGE LEARNING 2012.

A

AB

B

C

Y 5 AB 1 C 1 D

C1D

D

Boolean functions are governed by an order of precedence. Unless otherwise

specified, AND functions are performed first, followed by ORs. This order results

in a form similar to that of algebra, where multiplication is performed before addition, unless otherwise specified.

Figure 5.4 shows two logic diagrams, one whose Boolean expression requires

parentheses and one that does not.

The AND functions in Figure 5.4a are evaluated first, eliminating the need

for parentheses in the output expression. The expression for Figure 5.4b requires

parentheses because the ORs are evaluated first.

Chapter 5: Boolean Algebra and Combinational Logic

105

Copyright 2011 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

60001_ch05_Rev03.inddxiv105

60001_FM_rev03.indd

8/10/11 2:58

8/19/11

1:14 PM

FIGURE 5.4 Order of Precedence of Boolean Operations

AB

A

B

AB 1 AC

AC

C

A 1B

A

B

(A 1 B) (A 1 B 1 C)

C

A1B1C

b. Parentheses required (OR, then AND)

© CENGAGE LEARNING 2012.

a. No parentheses required (AND, then OR)

Example 5.3

Write the Boolean expression for the logic diagrams in Figure 5.5.

FIGURE 5.5 Example 5.3: Order of Precedence

A

B

1

3

C

Y

2

P

Q

1

3

R

S

2

b.

© CENGAGE LEARNING 2012.

a.

Solution

Examine the output of each gate and combine the resultant terms as required.

Figure 5.5a: Gate 1: A ? B

Gate 2: B ? C

Gate 3: Y Gate 1 1 Gate 2 5 A ? B 1 B ? C

Note . . .

In a Boolean expression

with two or more

overbars, bars of equal

length cancel and bars of

unequal length do not.

106

Figure 5.5b: Gate 1: P 1 Q 5 P 1 Q

Gate 2: Q 1 R

Gate 3: S 5 Gate 1 ? Gate 2 5 P 1 Q ? Q 1 R

5 (P 1 Q)(Q 1 R)

Note that when two bubbles touch, they cancel out, as in the doubly inverted

P input or the connection between the outputs of gates 1 and 2 and the inputs

of gate 3 in Figure 5.5b. In the resultant Boolean expression, bars of the same

length cancel; bars of unequal length do not.

Digital Electronics

Copyright 2011 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

60001_ch05_Rev03.inddxiv106

60001_FM_rev03.indd

8/10/11 2:58

8/19/11

1:14 PM

FIGURE 5.6 Logic Gate Networks

Your Turn

5.1

Write the Boolean expression for the logic

diagrams in Figure 5.6, paying attention to the

order of precedence rules.

A

B

Y

C

D

X

Logic Diagrams from Boolean Expressions

OUT

Y

Z

KEY TERMS

Levels of gating The number of gates through which a signal

must pass from input to output of a logic gate network.

Double-rail inputs Boolean input variables that are available

to a circuit in both true and complement form.

Synthesis The process of creating a logic circuit from a description

such as a Boolean equation or truth table.

b.

We can derive a logic diagram from a Boolean expression by applying the

order of precedence rules. We examine an expression to create the first level

of gating from the circuit inputs, then combine the output functions of the

first level in the second level gates, and so forth. Input inverters are often not

counted as a gating level, as we usually assume that each variable is available

in both true (noninverted) and complement (inverted) form. When input variables are available to a circuit in true and complement form, we refer to them

as double-rail inputs.

The first level usually will be AND gates if no parentheses are present; if OR

gates are in the first level, parentheses will usually be necessary. (Not always,

however; parentheses merely tell us which functions to

FIGURE 5.7 Logic Diagram for Y = AC + BD + AD

synthesize first.) Although we will try to eliminate bars over

groups of variables by use of DeMorgan’s theorems and the

AC

A

bubble-to-bubble convention, we should recognize that a

bar over a group of variables is the same as having those

BD

B

variables in parentheses.

Let us examine the Boolean expression Y 5 AC 1 BD 1 C

Y 5 AC 1 BD 1 AD

AD

AD. Order of precedence tells us that we synthesize the

AND AND AND

OR

AND functions first. This yields three 2-input AND gates, D

with outputs AC, BD, and AD, as shown in Figure 5.7a. In

a. ANDs first

the next step, we combine these AND functions in a 3-input

OR gate, as shown in Figure 5.7b.

A

When the expression has OR functions in parentheses, we synthesize the ORs first, as for the expression

Y 5 (A 1 B)(A 1 C 1 D)(B 1 C). Figure 5.8 shows this B

Y 5 AC 1 BD 1 AD

process. In the first step, we synthesize three OR gates for C

the terms (A 1 B), (A 1 C 1 D), and (B 1 C). We then

combine these terms in a 3-input AND gate. Again, this is D

similar to algebra, where multiplication is done before addib. Combine ANDs in an OR gate

tion unless parentheses are present.

Chapter 5: Boolean Algebra and Combinational Logic

© CENGAGE LEARNING 2012.

W

© CENGAGE LEARNING 2012.

a.

107

Copyright 2011 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

60001_ch05_Rev03.inddxiv107

60001_FM_rev03.indd

8/10/11 2:59

8/19/11

1:14 PM

FIGURE

FIGU

GURE

RE 5.8

5.8 Logic Diagram for Y 5 (A + B)(A + C + D)(B

B + C)

(A 1 B)

A

B

(A 1 C 1 D)

C

D

(B 1 C)

Y 5 (A 1 B)(A 1 C 1 D)(B 1 C)

OR

OR

OR

AND

a. ORs first

A

C

D

Y 5 (A 1 B)(A 1 C 1 D)(B 1 C)

b. Combine ORs in an AND gate

© CENGAGE LEARNING 2012.

B

Example 5.4

Synthesize the logic diagrams for the following Boolean expressions:

1. P 5 QRS + ST

2. X 5 (W 1 Z 1 Y)V 1 (W 1 V)Y

FIGURE 5.9 Example 5.4: Logic Diagram for P = QRS + ST

QRS

Q

R

RS

S

S

ST

T

a. Combine inputs (NAND, then AND)

R

P 5 QRS 1 ST

RS

S

S

ST

T

b. First and second level gates combined in an OR

© CENGAGE LEARNING 2012.

QRS

Q

conti

co

continued...

108

Digital Electronics

Copyright 2011 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

60001_ch05_Rev03.inddxiv108

60001_FM_rev03.indd

8/10/11 2:59

8/19/11

1:14 PM

Solution

1. Recall that a bar over two variables acts like parentheses. Thus, the

QRS term is synthesized from a NAND, then an AND, as shown in

Figure 5.9a. Also shown is the second AND term, ST.

Figure 5.9b shows the terms combined in an OR gate.

2. Figure 5.10 shows the synthesis of the second logic diagram in three

stages. Figure 5.10a shows how the circuit inputs are first combined

in two OR gates. We do this first because the ORs are in parentheses.

In Figure 5.10b, each of these functions is combined in an AND gate,

according to the normal order of precedence. The AND outputs are

combined in a final OR function, as shown in Figure 5.10c.

FIGURE 5.10 Example 5.4: Logic Diagram for X = (W + Z + Y)V + (W + V)Y

W1Z1Y

W

Z

Y

W

W1V

V

a. ORs first (parentheses)

W1Z1Y

W

Z

Y

(W 1 Z 1 Y)V

V

Y

(W 1 V)Y

W1V

W

V

b. Combine with ANDs (order of precedence)

W1Z1Y

W

Z

Y

(W 1 Z 1 Y)V

V

X 5 (W 1 Z 1 Y)V 1 (W 1 V )Y

Y

W

V

W1V

(W 1 V)Y

c. Find output (OR)

© CENGAGE LEARNING 2012.

Example 5.5

Use DeMorgan’s theorem to modify the Boolean equation in part 1 of

Example 5.4 so that there is no bar over any group of variables. Redraw

Figure 5.9b to reflect the change.

Solution

P 5 QRS 1 ST 5 Q(R 1 S) 1 ST

continued...

Chapter 5: Boolean Algebra and Combinational Logic

109

Copyright 2011 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

60001_ch05_Rev03.inddxiv109

60001_FM_rev03.indd

8/10/11 2:59

8/19/11

1:14 PM

FIGURE 5.11 Example 5.5: Reworking Figure 5.9b

Q

© CENGAGE LEARNING 2012.

Q(R 1 S)

(R 1 S)

R

S

P 5 Q(R 1 S) 1 ST

S

ST

T

a. Logic diagram of P 5 Q(R 1 S) 1 ST

Q

QR

R

QS

P 5 QR 1 QS 1 ST

S

ST

T

b. Logic diagram of P 5 QR 1 QS 1 ST

Figure 5.11a shows the modified logic diagram. The levels of gating could

be further reduced from three to two (not counting input inverters) by

“multiplying through” the parentheses to yield the expression:

P 5 QR 1 QS 1 ST

Figure 5.11b shows the logic diagram for this form. We will examine this

simplification procedure more formally in Section 5.3.

FIGURE 5.12 Logic Diagram for AB + C

AB

A

B

Truth Tables from Logic Diagrams

or Boolean Expressions

There are two basic ways to find a truth table from a logic diagram. We

can examine the output of each gate in the circuit and develop its truth

table. We then use our knowledge of gate properties to combine these

intermediate truth tables into the final output truth table. Alternatively,

we can develop a Boolean expression for the logic diagram by examining the expression, then filling in the truth table in a single step. The former method is more

thorough and probably easier to understand when you are learning the technique.

The latter method is more efficient, but requires some practice and experience. We

will look at both.

Examine the logic diagram in Figure 5.12. Because there are three binary

inputs, there will be eight ways those inputs can be combined. Thus, we start by

making an 8-line truth table, as in Table 5.1.

The OR gate output will describe the function of the whole circuit. To assess

the OR function, we must first evaluate the AND output. We add a column

to the truth table for the AND gate and look for the lines in the table where

both A AND B equal logic 1 (in this case, the last two rows). For these lines,

we write a 1 in the AB column. Next, we look at the values in column C and

the AB column. If there is a 1 in either column, we write a 1 in the column for

the final output.

AB 1 C

C

© CENGAGE LEARNING 2012.

TABLE 5.1 Truth Table for

Figure 5.12

A

B

C

AB

AB 1 C

0

0

0

0

0

0

0

1

0

1

0

1

0

0

0

0

1

1

0

1

1

0

0

0

0

1

0

1

0

1

1

1

0

1

1

1

1

1

1

1

© CENGAGE LEARNING 2012.

110

Digital Electronics

Copyright 2011 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

60001_ch05_Rev03.inddxiv110

60001_FM_rev03.indd

8/11/11

8/19/11 10:43

1:14 PM

AM

Example 5.6

Derive the truth table for the logic diagram shown in Figure 5.13.

Solution

The Boolean expression for Figure 5.13 is (A 1 B)(A 1 C). We will create a

column for each input variable and for each term in parentheses, and a column for the final output. Table 5.2 shows the result. For the lines where A OR

B is 0, we write a 1 in the

(A 1 B) column. Where A

FIGURE 5.13 Example 5.6: Logic Diagram

OR C is 1, we write a 1 in the

A

A1B

(A 1 C) column. For the

(A1B)(A1C)

B

lines where there is a 1 in

both the (A 1 B) AND (A

C

1 C) columns, we write a 1

A1C

in the final output column. © CENGAGE LEARNING 2012.

TABLE 5.2 Truth Table for Figure 5.13

© CENGAGE LEARNING 2012.

A

B

C

(A 1 B)

(A 1 C)

(A 1 B)(A 1 C)

0

0

0

1

0

0

0

0

1

1

1

1

0

1

0

1

0

0

0

1

1

1

1

1

1

0

0

1

1

1

1

0

1

1

1

1

1

1

0

0

1

0

1

1

1

0

1

0

Another approach to finding a truth table is to analyze

the Boolean expression of a logic diagram. The logic

diagram in Figure 5.14 can be described by the Boolean

expression:

FIGURE 5.14 Logic Diagram

A

B

C

We can examine the Boolean expression to determine

that the final output of the circuit will be HIGH under one

of the following conditions:

ABC

AC

Y5ABC1AC1BD

© CENGAGE LEARNING 2012.

Y

5 ABC1 AC 1 BD

BD

D

A 5 0 AND B 5 1 AND C 5 1

OR,

A 5 0 AND C 5 0

OR,

B 5 0 AND D 5 0

All we have to do is look for these conditions in the truth table and write a 1

in the output column whenever a condition is satisfied. Table 5.3 shows the result

of this analysis with each line indicating which term, or terms, contribute to the

HIGH output.

Chapter 5: Boolean Algebra and Combinational Logic

111

Copyright 2011 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

60001_ch05_Rev03.inddxiv111

60001_FM_rev03.indd

8/10/11 2:59

8/19/11

1:14 PM

TABLE 5.3 Truth Table for Figure 5.14

B

C

D

Y

Terms

0

0

0

0

1

A C, B D

0

0

0

1

1

AC

0

0

1

0

1

BD

0

0

1

1

0

0

1

0

0

1

AC

0

1

0

1

1

AC

0

1

1

0

1

A BC

0

1

1

1

1

A BC

1

0

0

0

1

BD

1

0

0

1

0

1

0

1

0

1

1

0

1

1

0

1

1

0

0

0

1

1

0

1

0

1

1

1

0

0

1

1

1

1

0

FIGURE 5.15 Logic Diagram for Your Turn

Problem 5.2 © CENGAGE LEARNING 2012.

A

Your Turn

A1B

Y

B

BD

© CENGAGE LEARNING 2012.

A

5(A1B)(B1C)

5.2

Find the truth table for the logic

diagram shown in Figure 5.15.

B1C

C

5.2 SUM-OF-PRODUCTS

AND PRODUCT-OF-SUMS FORMS

KEY T ERMS

Minterm A product term in a Boolean expression where all possible variables

appear once in true or complement form [e.g., A B C; A B C].

Product term A term in a Boolean expression where one or more true

or complement variables are ANDed [e.g., A C].

Sum-of-products (SOP) A type of Boolean expression where several product

terms are summed (ORed) together [e.g., A B C 1 A B C 1 A B C].

Bus form A way of drawing a logic diagram so that each true and complement

input variable is available along a continuous conductor called a bus.

Product-of-sums (POS) A type of Boolean expression where several sum terms

are multiplied (ANDed) together [e.g., (A 1 B 1 C)(A 1 B 1 C)(A 1 B 1 C)].

112

Digital Electronics

Copyright 2011 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

60001_ch05_Rev03.inddxiv112

60001_FM_rev03.indd

8/10/11 2:59

8/19/11

1:14 PM

Maxterm A sum term in a Boolean expression where all possible variables appear

once, in true or complement form [e.g., A 1 B 1 C]; [(A 1 B 1 C)].

Sum term A term in a Boolean expression where one or more true

or complement variables are ORed [e.g., A 1 B 1 D].

TABLE 5.4 Truth Table for

Figure 5.16

B

C

Y

0

0

0

1

0

0

1

0

0

1

0

0

0

1

1

1

1

0

0

1

1

0

1

0

1

1

0

0

1

1

1

0

FIGURE 5.17 Logic Diagram for

Y = A B C + A B C + A B C © CENGAGE LEARNING 2012.

© CENGAGE LEARNING 2012.

A

© CENGAGE LEARNING 2012.

Suppose we have an unknown digital circuit, represented by the block in

Figure 5.16. All we know is which terminals are inputs, which are outputs, and

how to connect the power supply (eventually, we will leave power and ground out

of these drawings and assume they are present). Given only that information, we

can find the Boolean expression of the output.

First, we find the truth table by applying all possible input combinations in

binary order and reading the output for each one. Suppose the unknown circuit in

Figure 5.16 yields the truth table shown in Table 5.4.

FIGURE 5.16 Digital Circuit

with Unknown Function

The truth table output is HIGH for three conditions:

1. When A AND B AND C are all LOW, OR

2. When A is LOW AND B AND C are HIGH, OR

3. When A is HIGH AND B AND C are LOW.

Each of those conditions represents a minterm where the output Boolean

expression is HIGH. A minterm is a product term (AND term) that includes

all variables (A, B, C) in true or complement form. The variables in a minterm

are written in complement form (with an inversion bar) if the variable is a 0

in the corresponding line of the truth table, and in true form (no bar) if the

variable is a 1. The minterms are:

1. A B C

2. A B C

3. A B C

Because condition 1 OR condition 2 OR condition 3 produces a HIGH output

from the circuit, the Boolean function Y consists of all three minterms summed

(ORed) together, as follows:

Y5ABC1ABC1ABC

Note . . .

We can derive an SOP

expression from a truth

table as follows:

1. Every line on the truth

table that has a HIGH

output corresponds

to a minterm in the

truth table’s Boolean

expression.

2. Write all truth table

variables for every

minterm in true or

complement form. If a

variable is 0, write it in

complement form (with

a bar over it); if it is

1, write it in true form

(no bar).

3. Combine all minterms

in an OR function.

This expression is in a standard form called sum-of-products (SOP) form.

Figure 5.17 shows the equivalent logic circuit.

Chapter 5: Boolean Algebra and Combinational Logic

113

Copyright 2011 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

60001_ch05_Rev03.inddxiv113

60001_FM_rev03.indd

8/10/11 2:59

8/19/11

1:14 PM

The inputs A, B, and C and their complements are shown in bus form. Each variable is available, in true or complement form, at any point along a conductor. This is

a useful, uncluttered notation for circuits that require several of the input variables

more than once. The inverters are shown with the bubbles on their inputs to indicate

that the complement line is looking for a LOW input to activate it (note that there

is no functional difference in drawing the bubble on the input or the output of an

inverter). The true line (no inverter) is looking for a HIGH. Notice that dots indicate

connections; no connection exists where lines simply cross each other with no dot.

Example 5.7

Multisim Example

Multisim File: 05.01 SOP Circuit 1.ms11

Figure 5.18 shows a sum-of-products (SOP) circuit drawn in Multisim. The

three inputs (A, B, and C) are monitored with logic probes, as are the AND

gate outputs (G1, G2, and G3) and the circuit output (Y). The circuit is shown

with all inputs in the LOW state. Open the file for this example and operate

the switches A, B, and C to go through all possible binary input combinations.

a. Which input states turn on the logic probes for G1, G2, and G3?

b. How does this correspond to the state of the logic probe for output Y?

c. Write the Boolean expression for the SOP circuit in Figure 5.18.

FIGURE 5.18 Example 5.7: SOP Circuit with All Inputs LOW

VCC

1

5V

R1

2

3

4

5

1 4SIP

10 kΩ

Key = A

Key = B

Key = C

A

B

C

GND

011

101

Y

110

G1 G2 G3

© CENGAGE LEARNING 2012.

Solution

a. Figure 5.19A, Figure 5.19B, and Figure 5.19C show the three states

where one of the AND gate outputs is HIGH.

continued...

114

Digital Electronics

Copyright 2011 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

60001_ch05_Rev03.inddxiv114

60001_FM_rev03.indd

8/10/11 2:59

8/19/11

1:14 PM

FIGURE 5.19A Example 5.7: SOP Circuit with AND Gate 1 Active

VCC

1

5V

R1

2

3

4

5

1´4SIP

10 kW

A

Key = A

B

Key = B

C

Key = C

GND

011

101

Y

110

G1 G2 G3

© CENGAGE LEARNING 2012.

FIGURE 5.19B Example 5.7: SOP Circuit with AND Gate 2 Active

VCC

1

5V

R1

2

3

4

5

1´4SIP

10 kW

Key = A

Key = B

Key = C

A

B

C

GND

011

101

Y

110

G1 G2 G3

© CENGAGE LEARNING 2012.

continued...

Chapter 5: Boolean Algebra and Combinational Logic

115

Copyright 2011 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

60001_ch05_Rev03.inddxiv115

60001_FM_rev03.indd

8/10/11 2:59

8/19/11

1:14 PM

FIGURE 5.19C Example 5.7: SOP Circuit with AND Gate 3 Active

VCC

1

5V

R1

2

3

4

5

1 4SIP

10 kΩ

A

Key = A

B

Key = B

C

Key = C

GND

011

101

Y

110

G1 G2 G3

© CENGAGE LEARNING 2012.

Figure 5.19A shows the output of G1 HIGH when ABC 5 011. In Figure 5.19B,

output G2 is HIGH when ABC 5 101. In Figure 5.19C, G3 is HIGH when

ABC 5 110.

b. The logic probe for output Y is ON whenever any of the AND gate

outputs, G1, G2, or G3 are HIGH.

c. The Boolean expression for the circuit is determined by the three

product terms for the AND gates: Y 5 A B C 1 A B C 1 A B C.

Example 5.8

Table 5.5 and Table 5.6 show the truth tables for the Exclusive OR and the

Exclusive NOR functions. Derive the sum-of-products expression for each of

these functions and draw the logic diagram for each one.

TABLE 5.6

A

B

AÅB

0

0

0

1

0

1

1

1

0

1

0

1

© CENGAGE LEARNING 2012.

XOR Truth Table

XOR Truth Table

A

B

AÅB

0

0

0

1

1

0

1

1

0

1

0

1

© CENGAGE LEARNING 2012.

TABLE 5.5

continued...

116

Digital Electronics

Copyright 2011 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

60001_ch05_Rev03.inddxiv116

60001_FM_rev03.indd

8/10/11 2:59

8/19/11

1:14 PM

Solution

XOR: The truth table yields two product terms: A B and A B. Thus, the SOP

form of the XOR function is AÅB 5 A B 1 A B. Figure 5.20 shows the

logic diagram for this equation.

XNOR: The product terms for this function are: A B and A B. The SOP form of

the XNOR function is A Å B 5 A B 1 A B. The logic diagram in Figure

5.21 represents the XNOR function.

FIGURE 5.20 Example 5.8: SOP Form

of XOR Function © CENGAGE LEARNING 2012.

A

FIGURE 5.21 Example 5.8: SOP Form

of XNOR Function © CENGAGE LEARNING 2012.

A

B

B

A 1 B 5 AB 1 AB

A 1 B 5 AB 1 AB

We can also find the Boolean function of a truth table in product-of-sums

(POS) form. The product-of-sums form of a Boolean expression consists of a

number of maxterms (i.e., sum terms, OR terms, containing all variables in true

or complement form) that are ANDed together. To find the POS form of Y, we will

find the SOP expression for Y and apply DeMorgan’s theorems.

Recall DeMorgan’s theorems:

X1Y1Z5XYZ

XYZ5X1Y1Z

When the theorems were introduced, they were presented as two-variable

theorems, but in fact they are valid for any number of variables.

Let’s reexamine Table 5.4. To find the sum-of-products expression for Y, we

wrote a minterm for each line where Y 5 1. To find the SOP expression for Y, we

must write a minterm for each line where Y 5 0. Variables A, B, and C must appear

in each minterm, in true or complement form. A variable is in complement form

(with a bar over the top) if its value is 0 in that minterm, and it is in true form (no

bar) if its value is 1.

We get the following minterms for Y:

ABC

ABC

ABC

ABC

ABC

Thus, the SOP form of Y is:

Y5ABC1ABC1ABC1ABC1ABC

Chapter 5: Boolean Algebra and Combinational Logic

117

Copyright 2011 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

60001_ch05_Rev03.inddxiv117

60001_FM_rev03.indd

8/10/11 2:59

8/19/11

1:14 PM

To get Y in POS form, we must invert both sides of the

above expression and apply DeMorgan’s theorems to the

right-hand side.

FIGURE

FI

IGU

GURE

RE 5.22

55.2

.222 POS Logic Circuit for Table 5.4

© CENGAGE LEARNING 2012.

Y5Y5ABC1ABC1ABC1ABC1ABC

5 (A B C) (A B C) (A B C) (A B C) (A B C)

5 (A 1 B 1 C) (A 1 B 1 C) (A 1 B 1 C) (A 1 B 1 C)

(A 1 B 1 C)

This Boolean expression can be implemented by the logic

circuit in Figure 5.22.

We don’t have to go through the whole process just

outlined every time we want to find the POS form of a function. We can find it directly from the truth table, using the

procedure summarized in the accompanying Note. Use this

procedure to find the POS form of the expression given by

Table 5.4. The terms in this expression are the same as those

derived by DeMorgan’s theorem.

Note . . .

Deriving a POS expression

from a truth table:

1. Every line on the truth

table that has a LOW

output corresponds

to a maxterm in the

truth table’s Boolean

expression.

2. Write all truth table

variables for every maxterm in true or complement form. If a variable

is 1, write it in complement form (with a bar

over it); if it is 0, write

it in true form (no bar).

3. Combine all maxterms

in an AND function.

Note that these steps are

all opposite to those used

to find the SOP form of

the Boolean expression.

Example 5.9

Find the Boolean expression, in both SOP and POS forms, for the logic

function represented by Table 5.7. Draw the logic circuit for each form.

TABLE 5.7

A

Truth Table for Example 5.9 (with Minterms and Maxterms)

B

C

D

Y

Minterms

Maxterms

0

0

0

0

1

ABCD

0

0

0

1

1

ABCD

0

0

1

0

0

0

0

1

1

1

0

1

0

0

0

A1B1C1D

0

1

0

1

0

A1B1C1D

0

1

1

0

0

A1B1C1D

0

1

1

1

0

A1B1C1D

1

0

0

0

1

1

0

0

1

0

1

0

1

0

1

1

0

1

1

0

1

1

0

0

1

ABCD

1

1

0

1

1

ABCD

1

1

1

0

1

ABCD

1

1

1

1

0

A1B1C1D

ABCD

ABCD

A1B1C1D

ABCD

A1B1C1D

A1B1C1D

© CENGAGE LEARNING 2012.

Solution

All minterms (for SOP form) and maxterms (for POS form) are shown in

the last two columns of Table 5.7.

continued...

118

Digital Electronics

Copyright 2011 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

60001_ch05_Rev03.inddxiv118

60001_FM_rev03.indd

8/11/11

8/19/11 10:44

1:14 PM

AM

Boolean Expressions

SOP form:

Y5ABCD1ABCD1ABCD1ABCD1ABCD1ABCD

1ABCD1ABCD

POS form:

Y 5 (A 1 B 1 C 1 D)(A 1 B 1 C 1 D)(A 1 B 1 C 1 D)(A 1 B 1 C 1 D)

(A 1 B 1 C 1 D)(A 1 B 1 C 1 D)(A 1 B 1 C 1 D) (A 1 B 1 C 1 D)

The logic circuits are shown in Figure 5.23 and Figure 5.24.

© CENGAGE LEARNING 2012.

FIGURE 5.23 Example 5.9: SOP Form

© CENGAGE LEARNING 2012.

FIGURE 5.24 Example 5.9: POS Form

Chapter 5: Boolean Algebra and Combinational Logic

119

Copyright 2011 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

60001_ch05_Rev03.inddxiv119

60001_FM_rev03.indd

8/10/11 2:59

8/19/11

1:14 PM

Your Turn

a.

A

B

C

Y

0

0

0

0

0

1

0

1

0

b.

A

B

C

Y

0

0

0

0

1

0

0

0

1

0

0

0

0

1

0

0

1

1

0

0

1

1

0

1

0

0

1

1

0

0

1

1

0

1

1

1

0

1

1

1

1

0

0

1

1

0

1

1

1

1

0

1

1

1

0

© CENGAGE LEARNING 2012.

Find the SOP and POS forms of the Boolean functions

represented by the following truth tables.

© CENGAGE LEARNING 2012.

5.3

5.3 SIMPLIFYING SOP EXPRESSIONS

KEY T ERM

Maximum SOP simplification The form of an SOP Boolean expression that

cannot be further simplified by canceling variables in the product terms.

It may be possible to get a POS form of the expression with fewer terms

or variables.

Earlier in this chapter, we discovered that we can generate a Boolean equation

from a truth table and express it in sum-of-products (SOP) or product-of-sums

(POS) form. From this equation, we can develop a logic circuit diagram. The

next step in the design or analysis of a circuit is to simplify its Boolean expression

as much as possible, with the ultimate aim of producing a circuit that has fewer

physical components than the unsimplified circuit. In this section, we will concentrate on simplifying SOP expressions only. POS expressions can be simplified by a

similar technique, but we will not examine it further.

FIGURE 5.25 SOP Circuit from Table 5.8

A

B

Reducing Product Terms by Factoring

and Cancellation

C

Figure 5.25 shows a sum-of-products circuit that is

described by the truth table in Table 5.8. It is also

described by the following Boolean expression:

© CENGAGE LEARNING 2012.

Y5ABC1ABC1ABC

Y

120

One way to simplify an SOP expression is to look

for pairs of product terms that differ by just one variable, then factor out what is common to the term, as

you would do in other types of algebra. For example,

the first two terms of the above Boolean expression are

Digital Electronics

Copyright 2011 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

60001_ch05_Rev03.inddxiv120

60001_FM_rev03.indd

8/10/11 3:00

8/19/11

1:14 PM

Y 5 (A 1 A) B C 1 A B C

We cannot do anything to the last term, as it differs from the original first term

by three variables and from the second term by two variables.

The next step in the simplification is to cancel the variables in parentheses.

Figure 5.26 uses logic gates to show how this is done. In Figure 5.26a, a variable is

ORed with its complement. Because one input to the OR gate is always HIGH, the

OR output is always HIGH, as well. This shows that the OR term in parentheses

cancels to a logic 1. This logic 1 is ANDed with the rest of the term, as shown in

Figure 5.26b. If the term B C is a 0, the AND output is a 0; if B C is a 1, then the AND

output is also a 1. Thus, the output of the AND gate is the same as the input B C. The

Boolean expression therefore simplifies to:

TABLE 5.8 Truth Table

for Figure 5.25

A

B

C

Y

0

0

0

1

0

0

1

0

0

1

0

0

0

1

1

0

1

0

0

1

1

0

1

0

1

1

0

0

1

1

1

1

© CENGAGE LEARNING 2012.

different in that one term has A and the other has A, but both terms have B and C.

Thus, we can factor the first two terms, as follows:

Y5BC1ABC

FIGURE 5.26 Gate Equivalents of Boolean Operations

A+A=1

A

a. Cancelling opposite variables

in an OR function

© CENGAGE LEARNING 2012.

Note . . .

If two product terms in an

SOP expression differ by

exactly one variable, the

differing variable can be

canceled:

1

1· B C = B C

BC

b. Combining a variable group

with a logic 1 in an AND function

The simplified SOP circuit is shown in Figure 5.27. Because the Boolean

expression cannot be simplified any further, we refer to this form as the maximum

SOP simplification.

xyz 1 xyz

5 xy(z 1 z) 5 xy

Reusing Product Terms

Figure 5.28 shows an SOP circuit with the following Boolean expression:

Y 5 ABC 1 ABC 1 ABC

Using the technique from the previous example, we could group the first product term with the second term and cancel the B variables or group the first and

third terms and cancel the Cs. Which is better?

FIGURE 5.28 Unsimplified SOP Circuit

A

B

C

FIGURE 5.27 Simplified SOP Circuit

B

C

Y

Y = B C + ABC

Chapter 5: Boolean Algebra and Combinational Logic

© CENGAGE LEARNING 2012.

© CENGAGE LEARNING 2012.

A

121

Copyright 2011 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

60001_ch05_Rev03.inddxiv121

60001_FM_rev03.indd

8/10/11 3:00

8/19/11

1:14 PM

FIGURE 5.29 Gate Equivalent of Reusing a

Product Term

It turns out that we can do both. To do so, we have to reuse the

first product term (ABC) and group it once with the second term

and once with the third term. Is this OK? Figure 5.29 illustrates

x + x + y why this is possible.

The OR gate in Figure 5.29 has three inputs representing prod=x+y

uct terms x, x, and y. The output expression of the gate is x 1 x 1 y.

This has the same effect on the output as if we just had one x input,

rather than two. (At least one input HIGH makes the OR output HIGH. If y is LOW,

it doesn’t matter if one or two other inputs are HIGH; the output would be HIGH

in either case. If y is HIGH, it doesn’t matter what the other inputs are doing; the

output will be HIGH anyway. The output will be LOW only if all inputs are LOW.)

Therefore, we can write:

x

y

© CENGAGE LEARNING 2012.

x1y5x1x1y

This implies that a product term (represented by x) in the above expression

can be written more than once without having an effect on the output. Applying

this principle and the previous cancellation technique, we get the following simplification:

Y 5 ABC 1 ABC 1 ABC

FIGURE 5.30 Simplified SOP Circuit

5 ABC 1 ABC 1 ABC 1 ABC

5 ABC 1 ABC 1 ABC 1 ABC

5 AC (B 1 B)1 AB(C 1 C)

Y 5 AC 1 AB

A

B

Y = AB + AC

C

Figure 5.30 shows the logic diagram of the simplified Boolean expression.

© CENGAGE LEARNING 2012.

Example 5.10

Multisim Example

Multisim File: 05.04 SOP Circuit 4a.ms11

Figure 5.31 shows an SOP circuit drawn in Multisim.

TABLE 5.9 Truth Table

A

B

C

Y

0

0

0

0

0

0

1

1

0

1

0

0

0

1

1

0

1

0

0

1

1

0

1

1

1

1

0

0

1

1

1

0

a. Run the circuit simulation and determine the output truth table of the

circuit.

b. From the truth table, find the unsimplified Boolean expression.

c. Simplify the SOP expression as much as possible.

d. Modify the circuit in Figure 5.31 to show the circuit for the simplified

Boolean expression.

Solution

a. The truth table of the circuit in Figure 5.31 is shown in Table 5.9.

b. The Boolean expression for the circuit is given by: Y 5 A BC 1 AB C 1

ABC

c. The Boolean expression can be simplified as follows:

© CENGAGE LEARNING 2012.

122

Y 5 A BC 1 AB C 1 ABC 1 ABC

5 A BC 1 ABC 1 AB C 1 ABC

5 (A 1 A)BC 1 AB(C 1 C)

Y 5 BC 1 AB

continued...

Digital Electronics

Copyright 2011 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

60001_ch05_Rev03.inddxiv122

60001_FM_rev03.indd

8/10/11 3:00

8/19/11

1:14 PM

d. The Multisim file for the simplified Boolean expression is shown in

Figure 5.32.

FIGURE 5.31 Example 5.10: Multisim SOP Circuit

© CENGAGE LEARNING 2012.

VCC

1

5V

R1

2

3

4

5

1´4SIP

10 kW

A

Key = A

B

Key = B

C

Key = C

GND

Y

G1 G2 G3

FIGURE 5.32 Example 5.10: Simplified Multisim SOP Circuit

VCC

1

5V

R1

2

3

4

5

1´4SIP

10 kW

A

Key = A

B

Key = B

Key = C

C

GND

Y

G1 G2

© CENGAGE LEARNING 2012.

Chapter 5: Boolean Algebra and Combinational Logic

123

Copyright 2011 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

60001_ch05_Rev03.inddxiv123

60001_FM_rev03.indd

8/10/11 3:00

8/19/11

1:14 PM

Avoiding Redundant Terms

KEY T ERM

Redundant term An extra, unneeded product term in a simplified Boolean

expression.

Sometimes when we group terms more than once, as we did in the previous two

examples, we might end up with more terms than are necessary in a simplified

expression. These redundant terms make us use more hardware than is required

for a particular logic circuit.

For example, the SOP circuit in Figure 5.33 is represented by

the truth table in Table 5.10. The unsimplified SOP express on

has four product terms, shown in the table. We can refer to the

TABLE 5.10 Truth Table for Figure 5.33

terms by the numbers in parentheses at the far left column of the

A B C D

Y

table. Depending on how we simplify this circuit, we could end

up with two terms or with three.

(0)

0 0 0 0

1

ABCD

0

0

1

1

(2)

0

0

1

0

0

(3)

0

0

1

1

0

(4)

0

1

0

0

0

(5)

0

1

0

1

1

(6)

0

1

1

0

0

(7)

0

1

1

1

0

(8)

1

0

0

0

1

(9)

1

0

0

1

0

(10)

1

0

1

0

0

(11)

1

0

1

1

0

(12)

1

1

0

0

0

(13)

1

1

0

1

0

(14)

1

1

1

0

0

(15)

1

1

1

1

0

ABCD

FIGURE 5.33 SOP Circuit from Table 5.10

A

B

C

D

ABCD

ABCD

Y

© CENGAGE LEARNING 2012.

0

© CENGAGE LEARNING 2012.

(1)

The unsimplified Boolean expression for this circuit is Y 5 A B C D 1 A B C D 1

A B C D 1 A B C D, or showing the number value of each product term, rather

than the term itself, we can write Y 5 (0) 1 (1) 1 (5) 1 (8).

Using the earlier method of grouping and simplifying terms, we can make the

following groupings:

(0)1(1): A B C D 1 A B C D 5 A B C (D 1 D) 5 A B C

(1)1(5): A B C D 1 A B C D 5 A C D (B 1 B) 5 A C D

(0)1(8): A B C D 1 A B C D 5 (A 1 A) B C D 5 B C D

The simplified Boolean expression can be written as Y 5 A B C 1 A C D 1 B C D.

The logic diagram for this equation is shown in Figure 5.34a.

Recall that we found that it is acceptable to use terms more than once if it helps

to simplify the final Boolean expression. With that in mind, we grouped terms (0)

and (1), both of which overlapped other terms: (0)1(8) and (1)1(5). However,

this reuse of terms does not simplify the final expression. In fact, it adds one more

term than is required for the maximum Boolean simplification.

124

Digital Electronics

Copyright 2011 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

60001_ch05_Rev03.inddxiv124

60001_FM_rev03.indd

8/10/11 3:00

8/19/11

1:14 PM

FIGURE 5.34 Two Possible Simplifications of the SOP

Circuit from Table 5.10 © CENGAGE LEARNING 2012.

A

B

C

Y

a. All possible simplified terms

A

1. Each term must be grouped with another, if possible.

2. When attempting to group all terms, it is permissible

to group a term more than once.

3. Each pair of terms should have at least one term

that appears only in that pair.

B

C

D

Y

b. Redundant term eliminated

Your Turn

5.4

D

Find the maximum SOP simplifications for the function

represented by Table 5.11.

5.4 SIMPLIFICATION BY THE KARNAUGH

MAP METHOD

KEY TERMS

Karnaugh map A graphical tool for finding the maximum SOP or POS

simplification of a Boolean expression. A Karnaugh map (or K-map) works

by arranging the terms of an expression so that variables can be canceled by

grouping minterms or maxterms.

Cell The smallest unit of a Karnaugh map, corresponding to one line of a truth

table. The input variables are the cell’s coordinates, and the output variable is

the cell’s contents.

TABLE 5.11 Truth Table

for Your Turn Problem 5.4

A

B

C

Y

0

0

0

0

0

0

1

1

0

1

0

1

0

1

1

1

1

0

0

0

1

0

1

0

1

1

0

1

1

1

1

0

Chapter 5: Boolean Algebra and Combinational Logic

© CENGAGE LEARNING 2012.

Suppose we eliminate this first grouping and use

only the last two groups, which then gives us the

expression Y 5 A C D 1 B C D. The logic diagram for

this expression is shown in Figure 5.34b. This further

simplified expression covers all the required product

terms of the original expression and also gives us one

less AND gate than the other, less simplified form of

the Boolean expression.

This points to an important tip to remember when

grouping product terms for simplification of an SOP

expression. When grouping terms for simplification,

every pair of terms must have at least one term that

only belongs to that pair. Otherwise you will get

redundant terms that must be further canceled to get

the maximum SOP simplification.

In our example, in the pair (0)1(1), both (0) and

(1) were also grouped with other terms. In the other

two groups, at least one term belonged only to that

group: (5) was only grouped with (1); term (8) was only

grouped with (0).

In summary, when simplifying Boolean expressions,

the following guidelines apply:

125

Copyright 2011 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

60001_ch05_Rev03.inddxiv125

60001_FM_rev03.indd

8/10/11 3:00

8/19/11

1:14 PM

Cell coordinate A variable around the edge of a K-map that represents an input

variable (e.g., A, B, C, or D) for the Boolean expression to be simplified.

Cell content A 0 or 1 that represents the value of the output variable (e.g., Y)

of a Boolean expression for a particular set of coordinates.

Adjacent cell Two cells are adjacent if there is only one variable that is

different between the coordinates of the two cells. For example, the cells

for minterms ABC and ABC are adjacent.

Pair A group of two adjacent cells in a Karnaugh map. A pair cancels one

variable in a K-map simplification.

Quad A group of four adjacent cells in a Karnaugh map. A quad cancels two

variables in a K-map simplification.

Octet A group of eight adjacent cells in a Karnaugh map. An octet cancels three

variables in a K-map simplification.

Reducing circuitry using the laws of Boolean algebra may seem like a complex task.

We will explore a more visual method in this section. In the circuit represented by

Table 5.10, we derived a sum-of-products Boolean expression from a truth table

and simplified the expression by grouping minterms that differed by one variable.

We made this task easier by breaking up the truth table into groups of four lines.

(It is difficult for the eye to grasp an overall pattern in a group of 16 lines.) We

chose groups of four because variables A and B are the same in any one group and

variables C and D repeat the same binary sequence in each group. This allows us

to see more easily when we have terms differing by only one variable.

The Karnaugh map, or K-map, is a graphical tool for simplifying Boolean

expressions that uses a similar idea. A K-map is a square or rectangle divided into

smaller squares called cells, each of which represents a line in the truth table of the

Boolean expression to be mapped. Thus, the number of cells in a K-map is always

a power of 2, usually 4, 8, or 16. The coordinates (“edge variables”) of each cell are

the input variables of the truth table. The cell content is the value of the output

variable on that line of the truth table. Figure 5.35 shows the formats of Karnaugh

maps for Boolean expressions having two, three, and four variables, respectively.

There are two equivalent ways of labeling the cell coordinates: numerically or

by true and complement variables. We will use the numerical labeling because it

is always the same, regardless of the chosen variables.

The cells in the Karnaugh maps are set up so that the coordinates of any two

adjacent cells differ by only one variable. By grouping adjacent cells according to

specified rules, we can simplify a Boolean expression by canceling variables in their

true and complement forms, much as we did algebraically in the previous section.

Two-Variable Map

TABLE 5.12 Truth Table

for a Two-Variable Boolean

Expression

A

B

Y

0

0

1

0

1

1

1

0

0

1

1

0

Table 5.12 shows the truth table of a two-variable Boolean expression.

The Karnaugh map shown in Figure 5.36 is another way of showing the same

information as the truth table. Every line in the truth table corresponds to a cell,

or square, in the Karnaugh map.

The coordinates of each cell correspond to a unique combination of input variables (A, B). The content of the cell is the output value for that input combination.

If the truth table output is 1 for a particular line, the content of the corresponding

cell is also 1. If the output is 0, the cell content is 0.

The SOP expression of the truth table is

© CENGAGE LEARNING 2012.

126

Y5AB1AB

Digital Electronics

Copyright 2011 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

60001_ch05_Rev03.inddxiv126

60001_FM_rev03.indd

8/10/11 3:00

8/19/11

1:14 PM

FIGURE 5.35 Karnaugh Map Formats

© CENGAGE LEARNING 2012.

FIGURE 5.36

Karnaugh Map

for Table 5.12

© CENGAGE LEARNING 2012.

FIGURE 5.37

Grouping a Pair

of Adjacent

Adjjacent Cells

Only one

change of

variable

per row

Only one change of

variable per column

© CENGAGE LEARNING 2012.

Only one

change of

variable

per row

which can be simplified as follows:

Y 5 A (B 1 B)

We can perform the same simplification by grouping the adjacent pair of 1’s

in the Karnaugh map, as shown in Figure 5.37.

To find the simplified form of the Boolean expression represented in the

K-map, we examine the coordinates of all cells in the circled group. We retain

coordinate variables that are the same in all cells and eliminate coordinate

variables that are different in different cells.

In this case:

A is a coordinate of both cells of the circled pair. (Keep A.)

Note . . .

B is a coordinate of one cell of the circled pair, and B is a coordinate of the

other. (Discard B and B.)

When we circle a pair

of 1’s in a K-map, we

are grouping the common variable in two

minterms, then factoring

out and canceling the

complements.

Y 5 A (B 1 B) 5 A

Three- and Four-Variable Maps

Refer to the forms of three- and four-variable Karnaugh maps shown in Figure 5.35.

Each cell is specified by a unique combination of binary variables. This implies

Chapter 5: Boolean Algebra and Combinational Logic

127

Copyright 2011 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

60001_ch05_Rev03.inddxiv127

60001_FM_rev03.indd

8/10/11 3:00

8/19/11

1:14 PM

© CENGAGE LEARNING 2012.

FIGURE 5.38 Quad

that the three-variable map has 8 cells (because 23 5 8) and the four-variable map

has 16 cells (because 24 5 16).

The variables specifying the row (both maps) or the column (the four-variable

map) do not progress in binary order; they advance such that there is only one

change of variable per row or column.

A group of four adjacent cells is called a quad. Figure 5.38 shows a Karnaugh

map for a Boolean function whose terms can be grouped in a quad. The Boolean

expression displayed in the K-map is:

Y5ABC1ABC1ABC1ABC

A and B are both part of the quad coordinates in true and complement form.

(Discard A and B.)

C is a coordinate of each cell in the quad. (Keep C.)

Note . . .

The number of cells in a

group must be a power

of 2, such as 1, 2, 4, 8,

or 16.

FIGURE

FIGU

FI

GURE

RE 5.39

5.39

39 Octet

Y5C

Grouping cells in a quad is equivalent to factoring two complementary pairs of

variables and canceling them.

Y 5 (A 1A)(B 1 B) C

You can verify that this is the same as the original expression by multiplying

out the terms.

An octet is a group of eight adjacent cells. Figure 5.39 shows the Karnaugh

map for the following Boolean expression:

© CENGAGE LEARNING 2012.

Y5ABCD1ABCD1ABCD1ABCD

1ABCD1ABCD1ABCD1ABCD

Variables A, C, and D are all coordinates of the octet cells in true and complement form. (Discard A, C, and D.)

B is a coordinate of each cell. (Keep B.)

Y5B

The algebraic equivalent of this octet is an expression where three complementary variables are factored out and canceled.

Y 5 (A 1A)B(C 1 C) (D 1 D)

Note . . .

A Karnaugh map

completely filled with

1’s implies that all input

conditions yield an output of 1. For a Boolean

expression Y, Y 5 1.

Grouping Cells Along Outside Edges

The cells along an outside edge of a three- or four-variable map are adjacent to

cells along the opposite edge (only one change of variable). Thus, we can group

cells “around the outside” of the map to cancel the variables. In the case of the

four-variable map, we can also group the four corner cells as a quad, because they

are all adjacent to one another.

Example 5.11

Use Karnaugh maps to simplify the following Boolean expressions:

a. Y 5 A B C 1 A B C 1 A B C 1 A B C

b. Y 5 A B C D 1 A B C D 1 A B C D 1 A B C D

Solution

Figure 5.40 shows the Karnaugh maps for the Boolean expressions labeled a

and b. Cells in each map are grouped in a quad.

continued...

128

Digital Electronics

Copyright 2011 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

60001_ch05_Rev03.inddxiv128

60001_FM_rev03.indd

8/10/11 3:00

8/19/11

1:14 PM

FIGURE 5.40 Example 5.11: K-Maps

© CENGAGE LEARNING 2012.

a. A and C are both coordinates of two cells in true form and two cells

in complement form. (Discard A and C.)

B is a coordinate of each cell. (Keep B.)

Y5B

b. A and C are both coordinates of two cells in true form and two cells

in complement form. (Discard A and C.)

B and D are coordinates of each cell. (Keep B and D.)

Y5BD

Note . . .

Loading a K-Map from a Truth Table

Figure 5.41 and Figure 5.42 show truth table and

Karnaugh map forms for three- and four-variable

Boolean expressions. The numbers in parentheses

show the order of terms in binary sequence for both

forms.

We don’t need a Boolean

expression to fill a

Karnaugh map if we have

the function’s truth table.

FIGURE 5.42 Order of Terms (Four-Variable Function)

FIGURE 5.41 Order of Terms (Three-Variable

Function)

1

2

back skip

1

1

skip

Chapter 5: Boolean Algebra and Combinational Logic

2

© CENGAGE LEARNING 2012.

back

© CENGAGE LEARNING 2012.

2

back

skip

129

Copyright 2011 Cengage Learning. All Rights Reserved. May not be copied, scanned, or duplicated, in whole or in part. Due to electronic rights, some third party content may be suppressed from the eBook and/or eChapter(s).

Editorial review has deemed that any suppressed content does not materially affect the overall learning experience. Cengage Learning reserves the right to remove additional content at any time if subsequent rights restrictions require it.

60001_ch05_Rev03.inddxiv129

60001_FM_rev03.indd

8/10/11 3:00

8/19/11

1:14 PM

Note . . .

If there is more than one

group of 1’s in a K-map

simplification, each group

is a term in the maximum

SOP simplification of the

mapped Boolean expression. The resulting terms

are ORed together.

The Karnaugh map is not laid out in the same order as the truth table.

That is, it is not laid out in a binary sequence. This is due to the criterion for

cell adjacency: no more than one variable change between rows or columns is

permitted.

Filling in a Karnaugh map from a truth table is easy when you understand

a system for doing it quickly. For the three-variable map, fill row 1, then row

2, skip to row 4, then go back to row 3. By doing this, you trace through the

cells in binary order. Use the phrase “1, 2, skip, back” to help you remember

this.

The system for the four-variable map is similar but also must account for the

columns. The rows get filled in the same order as the three-variable map, but

within each row, fill column 1, then column 2, skip to column 4, then go back to

column 3. Again, “1, 2, skip, back.”

The four-variable map is easier to fill from the truth table if we split the truth

table into groups of four lines, as we have done in Figure 5.42. Each group is one

row in the Karnaugh map. Following this system will quickly fill the cells in binary

order.

Go back and follow the order of terms on the four-variable map in

Figure 5.42, using this system. (Remember, for both rows and columns, “1, 2,

skip, back.”) Try tracing the order with your finger on the page. See how fast

you can do this.

Multiple Groups

Example 5.12

Use the Karnaugh map method to simplify the Boolean function represented

by Table 5.13.

TABLE 5.13 Truth Table

for Example 5.12

A

B

C

D

Y

0

0

0

0

1

0

0

0

1

0

0

0

1

0

1

0

0

1

1

0

0

1

0

0

0

0

1

0

1

1

0

1

1

0

0

0

1

1

1

1

1

0

0

0

0

1

0

0

1

0

1

0

1

0

0

1

0

1

1

0