Arithmetic Controller as 8/16 bit Extension [ PDF

advertisement

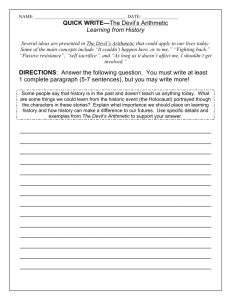

Arithmetic Overview Controller for In modern signal-processing systems with The central components of the architecture high-capacity arithmetic functions are of the arithmetic processor frame a 32-bit needed for data processing. Among the arithmetic-logical unit (ALU). The ALU is required high calculating speed for real- connected with the operand accumulator time applications numeric problems with by internal 32-bit data buses. This register standard functions often have to be solved. storages the operand data and intermedi- Applications with simple microcontrollers ate results during the command machining. often don’t reach the necessary calculation By that control unit the respective data speed to implement these tasks by software paths are switched and the control signals packets. For these applications an arithme- for several architecture components are tic processor unit that amends the system formed. 8 / 16-bit Microcontroller IPMS_ARICO as additive hardware has been developed. Based on arithmetic with real broken The data transfer and control of the arith- anchor numbers this processor offers basic, metic controller is done by a microprocessor standard and auxiliary functions. A simple interface. The operand data is stored in the configurable interface admits a connection operand accumulator. The writing of the of arithmetic processors with 8 / 16-bit command register controls the execution of microcontrollers and microprocessors. an arithmetic operation. In signal processing the occurring param- By a sequence of these control instructions eters and intermediate results in many the construction of complex calculating actual applications lie in a relatively small algorithms is possible. range. Therefore the use of floating-point arithmetic is not necessary and inexpensive The implemented digit format consists of fixed-point arithmetic can be applied. a 31-bit fixed-point representation and a Thereby the essential hardware effort sign bit. in circuit implementation is significantly Fraunhofer Institute for reduced. Photonic Microsystems IPMS Maria-Reiche-Str. 2 01109 Dresden Contact MUX dio michael.scholles@ipms.fraunhofer.de Dr. Hagen Grätz Phone +49 351 8823-217 hagen.graetz@ipms.fraunhofer.de 16 a 2 cs_b oe_b we_b µC Interface Phone +49 351 8823-201 www.ipms.fraunhofer.de erti RA C fica tio We are certified ce rtified arico-e Voluntary participation in regular monitoring according to ISO 9001:2008 BUF MUX ALU ACCB ACC MUX Quality Management n K DE OP1 OP2 OP3 OP4 OP5 OP6 OP7 OP8 1 Block diagram. T2 Control unit Dr. Michael Scholles ISO 9001:2008 Constants T1 clk rs int The instruction set of the arithmetic System features PIN name dio controller encompasses 18 commands. I/O IO Function bidirectional data bus a I address bus cs_b I choice signal available. For input and output of operands oe_b I read signal functions have been implemented that we_b I write signal convert from resp. to packed decimal clk I system clock notation. The interrupt signal indicates the rs I system reset int O interrupt output Beside addition, multiplication and division trigonometric and exponential functions are Arithmetic processor with 18 assignments 8 / 16-bit microprocessor interface Free selectable system clock end of command execution. This signal can be connected with an interrupt input of the Interrupt output 2 Pin description. controlling microprocessor. Power-down mode The microprocessor interface of the circuit is configurable by an external circuit in 8-bit Application areas resp. 16-bit mode. An implemented power- Command down mode allows the reduction of energy ADDS consumption in system neutral phases. The table in fig. 2 shows the connector pin Signal processing with smallest possible energy consumption Characteristics assignment of the circuit implementation. Size: 5268 NAND2 equivalents The system description is done in the hardware description language VHDL. Layout (1 μm CMOS): 18 mm² Therewith a synthesizable description for FPGA implementations and application Supply voltage: 1.5 – 5.0 V specific system solutions is available. Maximal clock frequency: 30 MHz The presented circuit was implemented in a 1 μm standard CMOS process. As Supply current (25 MHz): 2.5 mA components a 24-pin DIP package for 8-bit applications and a 28-pin DIP package are available. The following table shows the typical execution time of the arithmetic controller commands at a clock frequency of 25 MHz. For implementation and test of the calculation algorithms an evaluation board has been developed. Through the definition of a simple macro language the algorithms can be designed and checked independently from hardware. 4 Circuit layout. Execution time SUB 0.6 μs 0.6 μs MULS 10.1 μs DIVS 20.2 μs SQRT 22.1 μs EXP 126.0 μs LN 133.8 μs SIN 81.6 μs COS 63.1 μs TAN 120.2 μs ATAN 163.3 μs DEDU 8.3 μs DUDE 8.3 μs 3 Typical execution times.

![Information Retrieval June 2014 Ex 1 [ranks 3+5]](http://s3.studylib.net/store/data/006792663_1-3716dcf2d1ddad012f3060ad3ae8022c-300x300.png)