ISSN 2319-8885

Vol.02,Issue.11,

September-2013,

Pages:1161-1166

www.semargroups.org,

www.ijsetr.com

FPGA Implementation of Binary Coded Decimal Digit ALU

MADHUSMITHA1

R.VIJAYA2

M.Tech, ECE Dept, Dhruva Institute of Engineering &

Technology of Engineering and Technology, Hyderabad,

AP-INDIA. E-mail: madhusmitha.shial@gmail.com.

Asst Prof, ECE Dept, Dhruva Institute of Engineering &

Technology of Engineering and Technology, Hyderabad, APINDIA. E-mail:vijaya.ravula@gmail.com.

.

Abstract: Decimal arithmetic has high impact on the

overall performance of today’s financial, commercial and

all communication applications. Decimal additions,

subtraction, multiplication and division are the main

decimal operations used in any decimal arithmetic

algorithm. the building blocks of binary coded decimal

digit ALU are binary coded decimal digit adders, binary

coded decimal digit multipliers, binary coded decimal

digit subtractor and binary coded decimal digit division.

FPGAs provide an efficient hardware platform that can be

employed for accelerating binary coded decimal

algorithms. In this paper, different designs of decimal

digit adders, decimal digit multiplier, decimal digit

subtractor and decimal digit divisor are proposed. The

proposed designs were described, functionally tested, and

implemented using VerilogL and the Xilinx ISE 9.2

targeting Xilinx Vertix-5 XC5VLX30-3 FPGA..

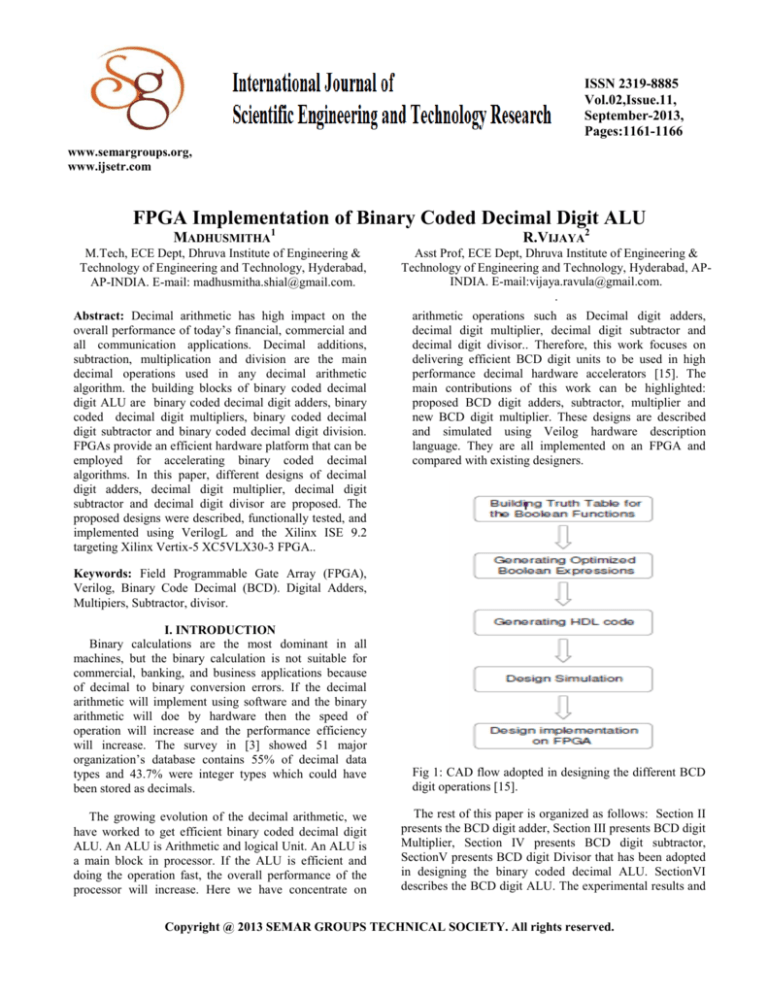

arithmetic operations such as Decimal digit adders,

decimal digit multiplier, decimal digit subtractor and

decimal digit divisor.. Therefore, this work focuses on

delivering efficient BCD digit units to be used in high

performance decimal hardware accelerators [15]. The

main contributions of this work can be highlighted:

proposed BCD digit adders, subtractor, multiplier and

new BCD digit multiplier. These designs are described

and simulated using Veilog hardware description

language. They are all implemented on an FPGA and

compared with existing designers.

Keywords: Field Programmable Gate Array (FPGA),

Verilog, Binary Code Decimal (BCD). Digital Adders,

Multipiers, Subtractor, divisor.

I. INTRODUCTION

Binary calculations are the most dominant in all

machines, but the binary calculation is not suitable for

commercial, banking, and business applications because

of decimal to binary conversion errors. If the decimal

arithmetic will implement using software and the binary

arithmetic will doe by hardware then the speed of

operation will increase and the performance efficiency

will increase. The survey in [3] showed 51 major

organization’s database contains 55% of decimal data

types and 43.7% were integer types which could have

been stored as decimals.

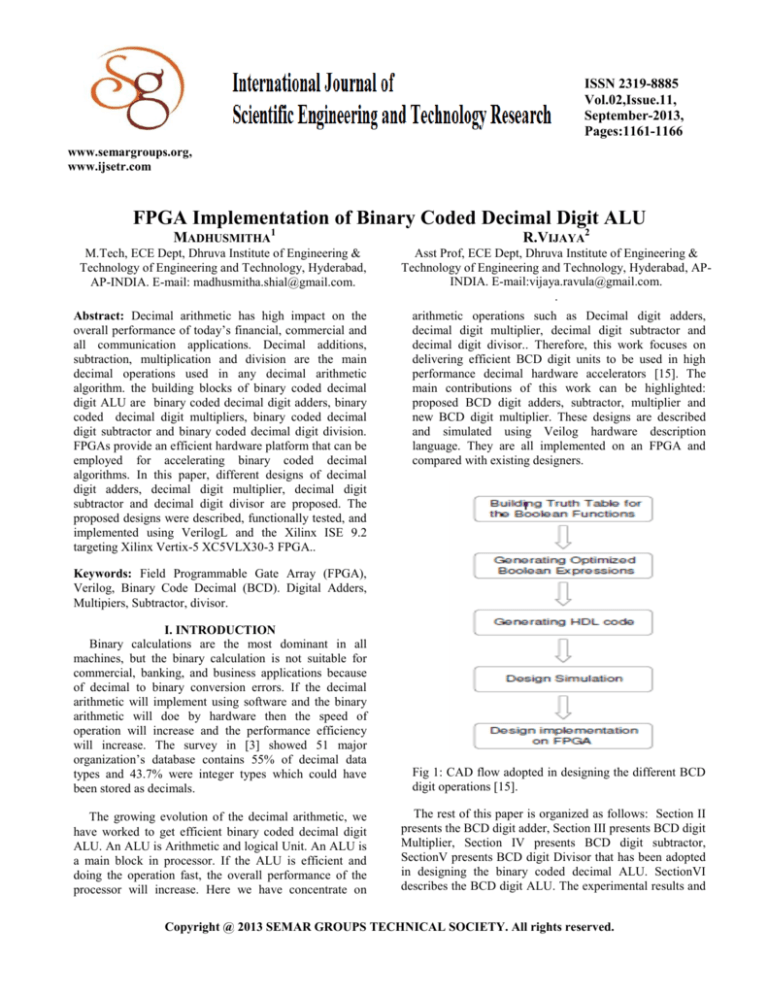

Fig 1: CAD flow adopted in designing the different BCD

digit operations [15].

The growing evolution of the decimal arithmetic, we

have worked to get efficient binary coded decimal digit

ALU. An ALU is Arithmetic and logical Unit. An ALU is

a main block in processor. If the ALU is efficient and

doing the operation fast, the overall performance of the

processor will increase. Here we have concentrate on

The rest of this paper is organized as follows: Section II

presents the BCD digit adder, Section III presents BCD digit

Multiplier, Section IV presents BCD digit subtractor,

SectionV presents BCD digit Divisor that has been adopted

in designing the binary coded decimal ALU. SectionVI

describes the BCD digit ALU. The experimental results and

Copyright @ 2013 SEMAR GROUPS TECHNICAL SOCIETY. All rights reserved.

R.VIJAYA, MADHUSMITHA

the comparisons are provided in Section VII. Finally, the

conclusion is given in Section VIII.

II. BCD DIGIT ADDER

The addition of two n-digit BCD numbers follows the

same procedure. After binary addition of any decimal pair,

the result is checked for correctness. Then, the correct

decimal carry output is passed to the next more significant

digit pair, to be added with the two decimal digits located in

the same position. The conditional addition of 6 in each

decimal digit position could be implemented using any 4-bit

binary carry-propagate adder architecture for each decimal

digit. The long carry chain for such BCD adder slows down

the addition operation.

Therefore, to improve the BCD adders speed, We have

implemented a direct BCD digit adder using a nine bit input,

five bit output combinational logic[1]. The nine bit inputs

are the two BCD input digits A and B plus the decimal carry

input Cin and the five bit outputs are the BCD digit of the

decimal sum S plus the decimal carry out Cout. The

combinational logic of this adder is constructed by

extracting the Boolean expressions for the BCD addition

result directly from the BCD input operands. the

combinational logic will represent numbers using the BCD

representation form, without any relation with the binary

numbering system. For example, to add (7 + 7 = 14), this

operation is translated to (0111 + 0111 = 10100)BCD. The

output result (10100) BCD is the BCD representation of the

decimal number 14. The most significant bit is the decimal

carry output generated from the addition operation, while

the other bits are the BCD summation digit. This is a

correction-free technique, since the addition result is in a

BCD form, and the need for correction is internally resolved

through the Boolean expressions of the addition result.

All possible combinations of the inputs are represented in

truth table. Since the inputs are nine bits, the number of

possible combinations is 29 = 512 but many of these

combinations are not valid since a BCD digit is less than

(10)10, while 4-bit number can take any value from 0 to

(15)10. This would help in minimizing the output logic

functions more.

TABLE I: Three Different Entries from the Truth

Table of The BCD Digit Adder

Inputs

cin a3a2a1a0

0

0111

0

1000

1

1001

b3b2b1b0

0111

0101

1001

Outputs

cout

s3s2s1s0

1

0100

1

0011

1

1001

Fig2: simulation output of BCD adder.

III. BCD DIGIT MULTIPLIER

Decimal digit multiplier is an integral building block of

any decimal multiplier. It produces two decimal digits as

a result of multiplying one multiplier decimal digit with

another multiplicand decimal digit. All well known

decimal digit multipliers use BCD-8421 encoding to

represent the decimal digits. In the digit-by-digit Look-up

Table approach, the bits of the multiplier BCD digit and

the multiplicand BCD digit are used to address a look-up

table, to produce the BCD digit product [8]. In [9], an

iterative BCD multiplier using digit-by-digit lookup table

technique is presented. A faster implementation was

described in [8]. The later uses the same look-up table

used in [9], but it uses a carry-save addition scheme to

add partial products, instead of the carry-propagate adder

International Journal of Scientific Engineering and Technology Research

Volume.02, IssueNo.11, September-2013, Pages:1161-1166

FPGA Implementation of Binary Coded Decimal Digit ALU

used in [9]. However, due to the wide range of digits

handled by the decimal system, digit-by-digit lookup table

multipliers are inefficient from both area and speed sides.

is 28 = 256. Among all these combinations only 100

combinations are valid and the rest are invalid[15].

TableII: Three Different Entries from the Truth Table

of the BCD Digit Multiplier

Inputs

Fig3: Expected implementation of the output functions of

the BCD digit multiplier on 6-input LUTs[15].

The BCD digit multiplier multiplies two BCD digits

to produce a two BCD digits product output. The

implemented direct BCD digit multiplier[13], word

”direct” means no need for neither ”first finding the

binary multiplication result and then converting the

product to a BCD form” as we are doing in traditional

multiplication. A simplified Boolean expressions impleme

-nted two multiply two BCD digit number. In this case,

the two operands are two decimal digits A = a3a2a1a0

and B = b3b2b1b0 and the output P = A × B is 8 bit

P7P6P5P4P3P2P1P0 (two BCD digits). Since the input is

8 bits wide, the number of combinations in the truth table

Outputs

a3a2a1a0

b3b2b1b0

P7p6p5p4

P3p2p1p0

0111

0111

0100

1001

1000

0101

0100

0000

1001

1001

1000

0001

Since the output functions in this case are functions of 8

variables, the implementation of most functions required a

hierarchy of LUTs for the case of 6-input LUTs FPGAs.

Figure 3 shows the expected implementation of the output

functions on 6-input LUTs. If the output functions depend

on more than six variables from the input variable then it

needs hierarchy of LUTs to be implemented. An example

on this is P1 which depends on all the eight input

variables. On the other hand, some functions depends

only on two variables like P0 or four variables like P7.

This means that these two outputs consumes a single 6input LUT each. The simplified Boolean expressions for

the BCD digit adders and multiplier designs are reported

by our work presented in [15].

Fig4: simulation output of BCD multiplier.

IV. BCD DIGIT SUBTRACTOR

In the BCD subtraction, the nine’s complement of the

subtrahend is added to the minuend. In the BCD

arithmetic, the nine’s complement is computed by nine

minus the number whose nine’s complement is to be

computed. This can be illustrated as the nine’s

complement of 5 will be 4 (9-5= 4), which can be

represented in BCD code as 0100. In BCD subtraction

International Journal of Scientific Engineering and Technology Research

Volume.02, IssueNo.11, September-2013, Pages:1161-1166

R.VIJAYA, MADHUSMITHA

using nine’s complement, there can be two possible

possibilities [16]:

1.

2.

The sum after the addition of minuend and the

nine’s complement of subtrahend is an invalid BCD

Code (an example is when 5 is subtracted from 8) or

a carry is produced from the MSB (an example is

when 1 is subtracted from 9). In this case, add

decimal 6 (binary 0110) and the end around carry

(EAC) to the sum. The final result will be the

positive number represented by the sum[16].

The sum of the minuend and the nine’s complement

of the subtrahend is a valid BCD code which means

that the result is negative and is in the nine’s

complement form. An example is, when 8 is

subtracted from 5[16].

The implemented BCD digit subtractor is a carry skip

BCD subtractor[15]. The carry skiping property of the

BCD adder can be beneficial only when its input carry

Cin=1. In order to extract the benefit of the carry skip

property of the BCD adder is proposed in BCD subtractor.

We have made LSB output (n[0]) of the 9’s compliment

as input carry Cin of the carry skip BCD adder and passed

‘0’ in its place for addition to the BCD adder. Therefore,

the numbers passed for addition in carry skip BCD adder

will be X+(n[3]n[2]n[1]’0’)+n[0], where n[0] will work as

Cin.[17].

Fig5: Carry skip BCD subtractor[17].

Fig6: simulation output of BCD subtractor

V. BCD DIGIT DIVISOR

A decimal division is similar to fixed point division,

except for the digits used in the operation- 0 and 1 for

fixed point, 0 through 9 for decimal. Correct alignment

must be established initially between the dividend and the

divisor. A sequence counter is initialized to the number of

bits in the divisor. When the sequence counter counts

down to zero, the division operation finished. The 2’s

compliment of the divisor is always added to the partial

remainder by EX-ORing the divisor with a logic 1. Then

the appropriate partial remainder is selected by

multiplexer, either the previous partial remainder or the

sum, which represents the current partial remainder[12].

International Journal of Scientific Engineering and Technology Research

Volume.02, IssueNo.11, September-2013, Pages:1161-1166

FPGA Implementation of Binary Coded Decimal Digit ALU

Fig7. BCD Digit Divisor

Fig8: simulation output of BCD divisor

VI. EXPERIMENTAL RESULTS AND

COMPARISONS

All our and other relevant proposed designs were

described using Verilog hardware description language,

and simulated to ensure correct functionality. They were

then synthesized with Xilinx ISE 9.2i tool and then

implemented in Vertix-5 XC5VLX30 -3 FPGA,

optimized for speed. Synthesis results of our BCD digit

ALU operation such as adder, subtractor, multiplier and

divisor shown in Tables III. These results show that the

time delay and Area in number of LUTs of BCD digit

ALU operation. However, it minimizes the area compares

to other existing design and gives the best area diagrams.

We compare our proposed BCD digit adders with

other three representative adders; the traditional BCD

digit adder (which applies the basic BCD addition

algorithm), the conditional speculative BCD digit adder

[7], and the [3:2] BCD-4221 decimal adder proposed by

[12]. The authors in [11] stated that their proposed most

recent (Q-T) based conditional speculative addition

algorithm[7], presents low latency and requires less

hardware than other alternatives. They have proposed two

TABLE III: Area for Different Decimal Digit Adders

(LUTS) and Delay(ns)

Decimal Digit

Area in Number

Delay(ns)

Operation

of LUTS

Direct Boolean

express BCD

adder

4.851

9

Direct BCD

multiplier

6.238

20

BCD

subtractor

5.098

16

BCD divisor

6.089

34

implementations for their algorithm, and they preferred

the (Q-T) carry tree implementation over their parallel

prefix carry tree implementation for their proposed adder.

However, due to the insufficient resources about the (QT) carry tree, we have implemented their other

International Journal of Scientific Engineering and Technology Research

Volume.02, IssueNo.11, September-2013, Pages:1161-1166

R.VIJAYA, MADHUSMITHA

architecture, modified for decimal addition. Results listed

in TablesIII clearly show that the implemented operations

are occupying less area with minimum delay compare to

other

The proposed BCD-4221[3:2] decimal adder of [12]

shows a good area/speed results comparing to our first

direct Boolean expressions BCD digit adder. However,

their proposed decimal adder is dedicated for [3:2] BCD4221 encoding addition, and not for [2:1] BCD-8421 one,

as ours. One can clearly observe that our direct Boolean

expressions BCD digit multiplier outperforms other BCD

digit multipliers in terms of speed and area. We have

implemented most recent BCD digit multipliers, proposed

in d [11]. The delay-optimized BCD digit multiplier of

[10], which calculates the binary multiplication of the two

BCD digits, then converts the product to a BCD form,

presents the worst speed/area results. It consists of

multiple components, which increases the number of gate

levels in the critical path, and hence the overall delay. The

SD radix-5 BCD digit multiplier of [11] was implemented

to compare with. The authors in [12] stated that their

radix-5 BCD digit multiplier gives the best speed figures

among their radix-10 and radix-4 BCD digit multipliers. It

produces four BCD-4221 digits for every BCD digit

multiplication operation. Thus, for a fair comparison,

extra hardware must be added to generate only two BCD

digits, as almost all other BCD digit multipliers in the

literature do.

V. CONCLUSION

In this paper we have implemented BCD digit ALU

arithmetic operation such as BCD digit adders, BCD digit

multiplier, BCD digit subtractor and BCD digit divisor for

the purpose of speeding up decimal arithmetic

applications over FPGAs. Each design is described,

verified and tested for a correct functionality using

Verilog coding and simulation. The different designs are

implemented using Xilinx ISE 9.2i CAD tool targeting

Xilinx Vertix-5 XC5VLX30 -3 FPGA. Experimental

results are provided and comparison with other existing

designs shows that the proposed designs outperform their

counterparts in terms of speed and area.

VI. REFERENCES

[3] A. Tsang and M. Olschanowsky, “A study of database

2 customer queries,” Tech. Rep., IBM Technical Report,

IBM Santa Teresa Laboratory, San Jose, CA, April 1991.

[4] M. S. Schmookler and A. Weinberger, “High speed

decimal addition,” IEEE Transactions on Computers, vol.

20, pp. 862–866, 1971.

[5] H. Wetter W. Bultmann, W. Haller and A. Worner,

“Binary and decimal adder unit,” 2001.

[6] J. Thompson, I. Karra, and M. J. Schulte, “A 64-bit

decimal floatingpoint adder,” in Proceedings of the IEEE

Computer Society Annual Symposium on VLSI, 2004,

pp. 297–298.

[7] A. V´azquez and E. Antelo, “Conditional speculative

decimal addition,” Nancy, France, 2006, pp. 47–57.

[8] R. H. Larson, “High speed multiply using four input

carry save adder,” IBM Technical Disclosure Bulletin, pp.

2053–2054, 1973.

[9] R. H. Larson, “Medium speed multiply,” IBM

Technical Disclosure Bulletin, p. 2055, 1973.

[10] G. Jaberipur and A. Kaivani, “Binary-coded decimal

digit multipliers,” IET Computers and Digital Techniques,

vol. 1, no. 4, pp. 377–381, 2007.

[11] E. M. Schwarz, “Decimal multiplication with

efficient partial product generation,” in Proceedings of the

17th IEEE Symposium on Computer Arithmetic,

Washington, DC, USA, 2005, ARITH ’05, pp. 21–28,

IEEE Computer Society.

[12] T. Lang and A. Nannarelli, “A radix-10

combinational multiplier,” in proc. of 40th Asilomar

Conference on Signals, Systems, and Computers, oct

2006, pp. 313–317.

[13] Binary-coded decimal digit multipliers G. Jaberipur

and A. Kaivani, omput. Digit. Tech., Vol. 1, No. 4, July

2007.

[14] Computer Arithmetic and Verilog HDL

Fundamentals von Joseph Cavanagh.

[15] FPGA Osama D. Al-Khaleel∗, Nuh H. Tuli´c§, and

Khaldoon M. Mhaidat’ FPGA implementation of Binary

Coded Decimal Digit Adders and Multipliers’ 978-14673-0862-5/12/$31.00 c 2012 IEEE.

[16]Jain, R.P.: Modern Digital Electronics, pp. 206–207.

Tata McGraw Hill, New York (2003).

[17] Himanshu Thapliyal1, Hamid R. Arabnia2, and M.B.

Srinivas” Efficient Reversible Logic Design of BCD

Subtractors.

[1] Osama D. Al-Khaleel∗, Nuh H. Tuli´c, and Khaldoon

M. Mhaidat, “FPGA implementation of Binary Coded

Decimal Digit Adders and Multipliers”, May 2009.

[2] M. F. Cowlishaw, “Decimal floating-point: Algorism

for computers,” in Proceedings of the 16th IEEE

Symposium on Computer Arithmetic (ARITH-16’03),

Washington, DC, USA, 2003, ARITH ’03, pp. 104–,

IEEE Computer Society.

International Journal of Scientific Engineering and Technology Research

Volume.02, IssueNo.11, September-2013, Pages:1161-1166