Arithmetic - Brunel University

advertisement

Arithmetic

How are numbers represented in the computer?

2 Numbers*

Unsigned integers

10110110101101102 = 0*20 + 1*21 + 1*22 + 0*23 + ….

1332668 = 6*80 + 6*81 + 2*82 + 6*23 + ….

octal

b6b6 = 6*160 + 11*161 + 6*162 + 11*163

hexadecimal

Refer to least significant bit lsp

most significant bit msp

16 bit gives us 216 numbers, normally 0 to 216 – 1

65535

Signed integers

Can still only represent 216 distinct numbers

-215 to 215 – 1 (including 0)

Use twos complement

msp becomes a sign bit

1 goes to 0 and 0 goes to 1 then add 1

-n goes to n

or n goes to -n

Twos complement

3 Numbers*

Signed integers

0000000000000000

0000000000000001

0000000000000010

0000000000000011

Wraps round to

large negative and

decreases.

=

=

=

=

0

1

2

3

………………………………

0111111111111111

1000000000000000

1000000000000001

1000000000000010

=

=

=

=

32767

-32768

-32767

-32766

………………………

Two large positives

overflow to a

negative

1111111111111101 = -3

1111111111111110 = -2

1111111111111111 = -1

0000000000000000 = 0

Addition works check:

Subtraction also:

Overflow to zero

2 + (-1) = 1

Correctly handle

the overflow

-1 – (-2) = 1

-2 –(-1) = -1

And multiplication (an exercise for the student)

Positives have

leading 0s.

Negatives 1s

4 Sign extend

Moving to registers

A number whose word length is equal to the register

width can only be loaded in one way. Copy bits.

A shorter number : byte for a 16/32/64 bit machine

two byte : 32/64 machine bit.

Can

be loaded in two ways

Copy the byte(s) into the low order bytes.

THEN

Fill the higher order bytes with zero.

OR

Sign extend

Fill the higher order bytes with the value of the msp.

1000000000000000

11111111111111111000000000000000 = -32768

Sign extend preserves the value :

Add two positive numbers – if sign bit is 1, Overflow

Add two negative numbers – if sign bit is 0, Overflow

Positive – Negative: sign bit - if sign bit is 1, Overflow

Negative – Positive: sign bit - if sign bit is 0, Overflow

On overflow,

ignore OR

generate an

exception

5 Multiply

Multiply

Multiplicand

Addition sometimes end up with more

10 1 0 1 0

bits than either have individually.

10 0 1 1 0

Multiplication usually ends up with

00 0 0 0 0

more bits.

Multiplier

1 01 0 1 0 0

1 0 10 1 0 00

Multiplicand moves to the left on each multiply.

Need a 64 bit register

Product

0 0 0 00 0 000

0 0 0 0 00 0000

Multiplicand

Shift left

64 bits

1 0 1 0 1 00 0 0 0 0

1 1 0 0 0 11 1 1 0 0

Multiplier

Shift Right

64-bit ALU

32 bits

Product

Control

Test

64 bits

Naïve – move Multiplicand on a clock cycle, move

multiplier on a clock cycle. Add (if multiplier = 1) on

cycle. Can perform them all in parallel

Can also halve

register and ALU

length. Unused

portions.

6 Multiply

Signed Multiply

Convert both to positive. Multiply and then

apply sign using normal rules

Faster multiply

Use an adder for each bit.

Lowest order bit either 0 or 1 from lsb of both numbers

Highest order bit either 0 or 1 for msb of both

numbers.

Second bit needs input from two input bits, ditto

second to last.

Significant speed up – useful elsewhere.

Helps to parallelise instructions

Need extra

hardware

7 Division

Division

Quotient

1001

Easy algorithm

1000 1001010

Line up try to subtract.

-1000

If less than zero dividend is zero,

10

add back on, move along 1 place

101

If greater than zero, dividend is 1

1010

move along one place and repeat.

-1000

10

Dividend

Don’t worry too much – infrequent.

Hardware similar to simple adder

Speed up as for multiplication not possible. Need to

know sign of remainder from partial subtractions

Divisor

Remainder

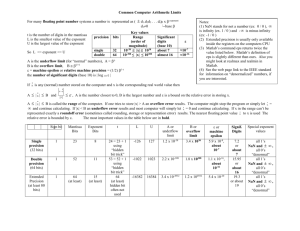

8 Floating Point

Binary fractions

A decimal is 43.1415

4*101 + 3*100 + 1*10-1 + 4*10-2 + 1*10-3 + 5*10-4

A binary 10.0101

1*21 + 0*20 + 0*2-1 + 1*2-2 + 0*2-3 + 1*2-4

How to represent:

Standard form

197.16 becomes 0.19716*10 3

197.16, 3

Standard form

0.00197 becomes 0.19716*10 -2

197.16, -2

Division by 2 in

binary has the

same effect as by

10 in decimal

Binary

10.0101 = 0.100101 * 2-2 becomes 100101, 10

How do we store this?

One part of the word is the fraction

The other is the

exponent

Scientific notation

normalised

9 FP representation

Binary fractions

Need to split bits between fraction

&

s

exponent

exponent

accuracy

range

faction

31

30-23

22-0

position

1

8

23

bits

10 VAX FP

Binary fractions

Need to split bits between fraction

&

Fraction low

31-16

s

15

accuracy

exponent

exponent

14-7

range

Bit 15 is the sign

Fraction high

6-0

position

The exponent is stored in excess 128:

the value of the exponent is the number in the

exponent field-128. The exponent can run from

-127 to 127. (Only 254 values because the value 0

has a special meaning)

The fraction has the second most significant bit in 6

and the least significant bit (the 24 th) in 16

6Fraction

high0

31

Fraction low

15

The number is normalised to 0.1… x 2 n

This means the first bit is always 1, so it isn’t stored!

11 Precision

Larger numbers or greater precision

224 is about 4 Million – so even banks need more

precision and scientific calculations frequently use

larger numbers

Double Precision

Fraction low

medium

s

exp

high

Same range

31-0

G Float

Also 8 bytes, but some of the extra bits go to range and

not precision

H Float

16 Bytes …

1984 … 32 bit

operating system &

64bit arithmetic

about 33 decimal digits and 10-4932 to 104932

G and H are much slower, they are implemented in

microcode and not hardware

In the VAX11/780 and

VAX11/750. The

floating point hardware

was optional. And

costly

12 Standard

IEEE

Defined by IEEE Std 754-1985

Developed in response to divergence of

representations Portability issues for scientific

code

Now almost universally adopted

Two representations

Single precision (32-bit)

Double precision (64-bit)

Different representations were a real pain.

S

Even without big-endian, little-endian

confusion and of course varying word

lengths

Exponent

Fraction

x ( 1)

S

(1 Fraction) 2

(Exponent Bias)

S: sign bit (0 non-negative, 1 negative)

Normalize significand: 1.0 ≤ |significand| < 2.0

Always has a leading pre-binary-point 1 bit, so no need

to represent it explicitly (hidden bit)

Significand is Fraction with the “1.” restored

Exponent: excess representation: actual exponent + Bias

Ensures exponent is unsigned

Single: Bias = 127; Double: Bias = 1023

13 IEEE

Precision and Range

Exponents 000….000 & 111…111 reserved

Range power of 2 :-126 127

Equates to about 10 to the (-38 38)

Double precision

About 10 to the (-308 308)

Double precision arithmetic tends to be much

slower, but remember (a-b)*c can loose a lot of

precision is a is approximately equal b.

Precision

Single about 6 decimal digits

Double about 16 decimal digits

Double precision arithmetic tends to be much

slower, but remember (a-b)*c can loose a lot of

precision if a is approximately equal b.

Special numbers

Infinity – and NaN (not a number) : result of 0/0

Intel had a problem

in 1994 with

accuracy.

Essentially Intel

argued that the

error occuring in

ninth digit affected

only a few people.

IBM stopped

shipping PCs with

the offending chip.

Intel forced to

replace chips an

suffered a lot of bad

publicity

14 FP arithmetic

FP add and subtract

Multi-cycle (but can be pipelined)

Normalise numbers – make exponents equal.

Multiply numbers. Normalise

Step 1

Step 2

Step 3

Step 4

15 FP arithmetic

FP multiply etc

Multiply unit, as complicated as adder.

FP unit will also do integer floating point

takes several cycles

In eg MIPS done by a separate co-processor.

VAX 11/700 series had a separate board, which

cost extra.

C code:

float f2c (float fahr) {

return ((5.0/9.0)*(fahr - 32.0));

}

fahr in $f12, result in $f0, literals in global

memory space

Compiled MIPS code:

lwc – load word to

coprocessor

f2c: lwc1

lwc2

div.s

lwc1

sub.s

mul.s

jr

$f16,

$f18,

$f16,

$f18,

$f18,

$f0,

$ra

const5($gp)

const9($gp)

$f16, $f18

const32($gp)

$f12, $f18

$f16, $f18

16 Operands

Types and Lengths

Data words also need to encode character sets

Character 8 bit

ASCII

Character 16 bit

Unicode

Also Ogham, Byzantine musical notation, ……

Integers .. Byte, half word, word, longword

Floating point, single, double.

Packed decimal (doesn’t suffer from rounding

errors)

17 Addressing

Alignment

Addressing is done via bytes, but computers work on words.

Starting at zero the first word is 0,1,2,3 bytes.

second word is 4,5,6,7

Can we use 1,2,3,4 or 2,3,4,5 or 3,4,5,6 as a word?

It depends ….

Some systems insist on stating at 0,4,8,12

This is referred to as alignment and if it is required is called

an alignment restriction

Word alignment is possible, as is half-word alignment. Some

machines allow unaligned access, but there may be a time

penalty.

sw $t0, 8($s1) stores from $t0

Addressable memory

The arguments of the instruction must give the memory

location and the register number.

The registers are numbered 0 to 31 and so need 5 bits

The memory is numbered 0 to 2n-1 bytes … it is this

restriction which determines the size of memory the computer

can address.

32 bit machine