A Historical Perspective on Computer Arithmetic

advertisement

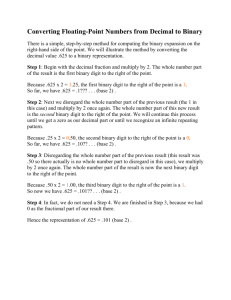

A Historical Perspective on Computer Arithmetic Stanley Mazor Outline: 7 Short Stories • Homage to comedians: Bud Abbott and Lou Costello • Routing logic adders • IBM 1620 floating point: • Fairchild Symbol IIR decimal floating point • MCS-4 floating point influence • DEC PDP-10 Fortran floating point--bug • 8080 CPU 16-bit ops vs. index register Simple Arithmetic Example by Bud Abbott 7 x 13 = 4-Switch Half-Adder S a b b a S = ab + ab b a S = ba + ab switch, relay, or MOSFET S 8-Switch Binary Full Adder S = abc + abc + abc + abc S = bca + acb + bca + acb S a c b a b c a a a b c + S ibm 1620 (1963) typewriter punched cards 1620 Decimal Operations 00345 3030333435 ASCII 00345 + 00002 Strip arithmetic 00347 00347 3030333437 result Fill ASCII • Strip, Fill, Compare, Add, Subtract, Multiply, Divide • No binary (no decimal/binary conversions) 1620 Decimal Arithmetic • • • • • • • • 6-bit = 4-bit BCD + flag + other Serial decimal-digit fixed point arithmetic Low to high order; stop at high end flag ‘end flag’ start 0373242425256229 No adder hardware: add table-lookup in memory 80 µs/digit (1 millsecond/ 10 digits) astrophysics ---50+ digit precision $100k system cost ($1,000,000 today’s dollar) 1620 Floating Point Software • • • • 2 digit exponent -99 -> +99 10 digit mantissa (?) sign/magnitude normalized fractional mantissa programmable fill: .7773333444 - .7771111333 .0002222111 .2222111xxx .2222111000, .2222111555, .2222111999 • user tries fill variations and compares results Dr. Gordon Moore 1965 Moore’s Law cost density • cost minimum • density increasing • costs decreasing Hardware will be free 1,000 amps Symbol IIR Computer Fairchild Symbol Computer (1966) • Use 10x more hardware (free) • New High Level Language • Hardware job control, paging, memory management • Hardware Translator (no other machine language) • Decimal floating point arithmetic • Variable length digit serial (MSD first) • dynamic precision control (Limit register) • explicit precision indication (empirical, exact) Symbol Computer 1968 • • • 220 IC’s per PCB 100 pin local/global bus ~120 PCB’s in computer – – – – – – – – Translator (15) Job Controller (10) Instruction Sequencer (15) Reference Processor (10) String and FPU (12*) Memory Controller (10) MemReclm, Channel (5) Text editor, Disk, etc. (8) * S. Mazor Serial Decimal Floating Point Z ←13.33333456743388; variable length decimal Z ← .333em + 76.4212345; empirical precision indication Limit ← 28; dyamic set of mantissa length upper limit Most significant digit first serial decimal arithmetic: 399 or 400 start .11222123344?? + .22333444055?? .33555567399... 399 or 400 .33555567 M 3 U X 4 1 digit buffer 1 digit buffer (incremented) 9’s counter 2 99 or 00 MCS-4 (1971) Busicom Calculator (MCS-4) MCS-4 Calculator’s PCB CPU 4 ROM’s (1k bytes) 1 RAM (80 digits) MCS-4 Block Diagram 4-bit ALU MCS-4 Block Diagram RAM MCS-4 80-digit RAM Exponent 16-digit Mantissa + 2 3 + 1 2 4 3 5 8 7 6 2 2 8 4 1 3 2 0 20 20 20 20 • RAM organized for Calculator floating point • Four 20 BCD-digit floating point numbers • 2 Signs, exponent, 16-digit mantissa • Example: +.1243587622841320 E+23 ---80 digits DEC PDP-10 (KA10) 1972 DEC PDP-10 (1972) • 36-bit words • Floating point hardware • Intel: Transient Analysis (24hrs/day) – my Fortran program PULS (before Spice) – Single user, teletype I/O – sparse matrix computation—heavy computation • Experienced: “oh that old bug” DEC Fortran bug • Fortan: Read command using F format • Software bug: lost sign in floating a decimal fraction. • Could not distinguish: .0003 from -.0003 • Difficult to track--- data dependent bug • Vendor was aware but didn’t publicize--(‘oh that old bug’) intel 8008 (1971) A B C D E H L intel 8080 (1972) intel 8080 16-bit Addition (1974) Program Counter BC + HL -> HL Stack Pointer DE + HL -> HL B C SP + HL -> HL D E HL + HL -> HL H L • Address arithmetic for HL memory address (BC or DE) • Address (indexed) into the stack (SP) • Shift HL left 8080 Decimal Adjust Accumulator 22 22 22 18 00 08 80 88 binary add 22 2A A2 A0 binary sum DAA: 00 06 60 66 22 30 (1)02 (1)06 + decimal sum • 2 packed BCD digits/byte, binary addition • DAA adjusts binary sum to BCD (and Carry)