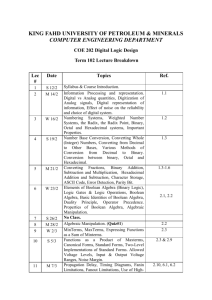

Digital Arithmetic - DoCircuits

advertisement

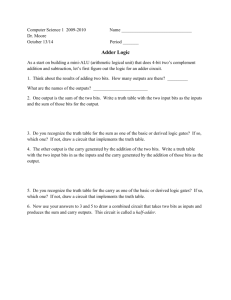

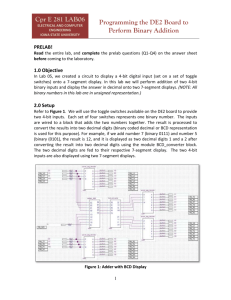

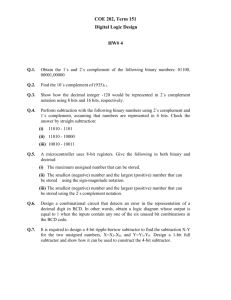

Digital Arithmetic In Chapter 2, we have discussed number systems such as binary, hexadecimal, decimal, and octal. We have also discussed sign representation techniques, for example, sign-bit representation and 2’s complement representation. Our discussions were extended to BCD and other codes, and simple arithmetic operations such as addition and subtraction using binary numbers. In this chapter, we will discuss the related digital circuits capable of performing elementary arithmetic operations, which are essential for computers and some other digital systems. After the completion of this chapter, the reader would be able to ∑ understand and design different types of adder and subtractor circuits, ∑ realize the importance of carry propagation, ∑ distinguish between binary addition and BCD addition, ∑ design 1’s and 2’s complement-based digital circuits, ∑ be familiar with the arithmetic logic unit (ALU), and ∑ design digital comparators with cascading inputs. 194 Digital Electronics 6.1 Binary Addition Addition is the most elementary arithmetic operation. Therefore, single-bit binary addition may be taken as the basic building block of digital arithmetic. Let P and Q be the two binary variables (each of 1-bit). Their sum may be any one of the following four, depending upon the magnitudes of P and Q: Binary variable P 0 0 1 1 Binary variable Q +0 +1 +0 +1 Sum (P + Q) = 0 = 1 = 1 = 10 Carry Note that only in the last case, when both operators are 1, a carry is generated and the sum becomes 0. If we consider only the primary bit of the result (Y), then the variations will be as presented in Table 6.1. Table 6.1 Binary addition (1-bit) P 0 0 1 1 Q 0 1 0 1 Y=P+Q 0 1 1 0 Comments Carry = 0 Carry = 0 Carry = 0 Carry = 1 The reader might have already correlated Table 6.1 with the truth table of an XOR gate. As a matter of fact, we may refer to Figure 3.14(c) of Chapter 3 (truth table for XOR gate) to compare with Table 6.1. They are similar in nature, and therefore, if we use an XOR gate, as in Figure 6.1, it may also be referred to as the basic building block of 1-bit binary addition. However, the circuit is not capable of generating any carry bit when both operators are 1 (refer to the last row of Table 6.1). This problem is eliminated in the half-adder circuit, discussed in following section. XOR truth table Input Output P Y Q 2-input XOR gate (a) P Q Y=P≈Q 0 0 1 1 0 1 0 1 0 1 1 0 (b) Figure 6.1 XOR gate as 1-bit basic adder (without carry bit) 6.1.1 Half Adder Referring to Table 6.1, we may note that the carry bit is generated only when both P and Q are 1. For all other conditions of P and Q, the carry bit remains 0. The simplest solution, therefore, is to incorporate a 2-input AND gate in the circuit with P and Q as the two inputs, and the carry bit as the output (Figure 6.2). Observe that now the circuit is perfectly capable of functioning as presented in Table 6.1. Digital Arithmetic Carryout Y P Q Figure 6.2 Half-adder circuit (1-bit adder with carry-out) Time to Take a Test Draw the K-map for carry-out for the half adder. 6.1.2 Full Adder The reader might wonder that if the above circuit (Figure 6.2) is capable of performing addition, then why designate it as half adder? As a matter of fact, this circuit is yet unable to perform the addition operation in the case of multi-bit operators. We have already indicated that the decimal numbers are represented by a group of multi-bit binary numbers. If we add decimal 7 to decimal 3, when both are expressed in binary, then the situation demands multi-bit binary addition, which will be as follows: Carry bit → 111 0 1 1 1 decimal 7 + 0 0 1 1 decimal 3 = 1 0 1 0 decimal 10 We can observe here that after addition of two rightmost bits (1 and 1), the result is 0 and a carry bit of 1 is generated. This carry bit is shifted to the adjacent bit (at left) where we have to add not two bits but three bits including the carry bit. In the half-adder circuit described above (Figure 6.2), there is no provision of accommodating this third bit or carry bit. We need some additional circuit for that purpose. Note that the circuit of Figure 6.2 is capable of performing only the first addition, that is, the addition of the rightmost two bits where there is no third bit (carry bit) present. Reader, Remember! Carry generated due to the addition of several bits is known as carry-out. This carry-out becomes carry-in for the next bit at immediate left and must be considered for the next bit addition. Answer to TTTT: P P Q 0 0 Q 0 1 Cout = P◊Q 195 196 Digital Electronics ? Confusion Clearing Corner The full adder accepts carry-in as the third input, but the half adder does not have any provision for it. This is the basic difference between the half adder and the full adder. How do we design the circuit of a full adder? Let us start with its truth table. With two Boolean operators P and Q, and a Carryin bit as input, we construct the truth table of a full adder with two outputs, namely Y (the sum or the main output) and Carryout, as presented in Table 6.2. Table 6.2 Truth table for full adder Input Output Carryin P Q Y Carryout 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 1 1 1 1 1 Reader, Remember! We are considering Q as the least significant bit (LSB). This will play an important role when we will consider the carry-propagation. The reader might have observed that there are two outputs (Y and Carryout) against three inputs (Carryin, P, and Q). The main output Y will be 1, if there is an odd number of 1s within the three inputs. For an even number of 1s, the Y output will be 0. The Carryout output will be 1 if two or all the three inputs are 1. If only one input is 1 or if all the inputs are 0, then the Carryout will be 0. To generate the main output Y, we may use two XOR gates, one following the other, as shown in Figure 6.3. Through this XOR gate pair, first we are adding P and Q, and their sum is then added to the Carryin bit to generate the final sum Y. To generate the Carryout, we may use three 2-input AND gates, and their output may be fed to a 3-input OR gate as illustrated in Figure 6.3. This circuit may also be designed using a K-map, as discussed below. From the truth table of a full adder (Table 6.2), a K-map may be generated as shown in Figure 6.4 to obtain the expressions for Y and Carryout. Note that we may consider three separate loops to generate the expression for Carryout as – Carry = ( Carry PQ + Carry PQ) + (Carry PQ + Carry PQ ) + (Carry P–Q + Carry PQ) out in in in in in which, after simplification, leads to the resultant expression as shown in Figure 6.4(b). in Digital Arithmetic Carryout Y Carryin P Q Figure 6.3 Full adder circuit PQ PQ PQ PQ PQ PQ PQ PQ Carryin 0 1 0 1 Carryin 0 0 1 0 Carryin 1 0 1 0 Carryin 0 1 1 1 K-map for Y K-map for Carryout Y = Carryin PQ + Carryin PQ + Carryin PQ + Carryin PQ Carryout = PQ + Carryin P + Carryin Q = Carryin (PQ + PQ) + Carryin (PQ + PQ) = Carryin (P ≈ Q) + Carryin (P ≈ Q) = Carryin ≈ P ≈ Q (a) (b) Figure 6.4 K-map for (a) sum Y and (b) Carryout for full adder The circuit shown in Figure 6.3 is known as 1-bit full adder and is generally represented by the symbol as illustrated in Figure 6.5(a). The timing diagram of this 1-bit full adder is presented in Figure 6.5(b). The reader may compare the timing diagram with the truth table of the full adder (Table 6.2). Y P Q 1-bit Full adder (a) P Carryin Carryout Carryin Q Y Carryout (b) Figure 6.5 1-bit full adder: (a) symbol and (b) timing diagram 197 198 Digital Electronics As mentioned earlier, the circuit presented in Figure 6.3 is not the only circuit for performing the operation of a full adder; several other designs are also possible to achieve the same function in different ways. Time to Take a Test Redesign the full-adder circuit using two half adders and logic gates. 6.1.3 n-bit Parallel Binary Adder As already indicated in the previous section, a binary addition is generally carried out for multiple binary digits for which several full adders are cascaded. Depending upon the system requirement, the number of full adders varies. However, in general, they are a multiple of 4. Figure 6.6 illustrates the schematic of a 4-bit binary adder consisting of four full adders with necessary interconnections. Y3 Cout FA 3 A3 B3 Y2 Cout FA 2 Cin A2 B2 Y1 Cout FA 0 FA 1 Cin A1 B1 Y0 Cout Cin A0 B0 Cin Figure 6.6 Schematic of a 4-bit binary adder In this case we are assuming that two 4-bit operands, namely A0–A3 and B0–B3, are to be added by the 4-bit adder circuit, producing the 4-bit sum Y0–Y3 along with a carry-out bit (Cout). Therefore, four numbers of full adders, namely FA 0–FA 3, are provided in the circuit. Note that as there will not be any carry-in input for the least significant bit, the Cin input of FA 0 is grounded to turn this input permanently 0. However, if used in cascade for multi-bit operations, the concerned Cin input has to be interfaced with the previous Cout output. The carry-out (Cout) generated by the first full adder (FA 0) becomes the carry-in (Cin) for the next higher bit adder (FA 1). The carry-out from FA 1 is fed into the carry-in of FA 2 and so on. The final carry-out, after Answer to TTTT: Full-adder using two half adders and one OR gate. Cin Y A B Cout Digital Arithmetic completion of 4-bit addition, is available from the Cout of FA 3, that is, the leftmost full adder. The reader may note that MSI circuits are commercially available for multi-bit binary addition (see Table 6.4). The external signals of an integrated circuit (IC) capable of performing 4-bit binary addition will be as shown in Figure 6.7. If the IC has to perform an addition of the least significant four bits where no carry-in is applicable, the Cin input of the device is grounded for 0 input. In other cases, the Cin input is obtained from the previous Cout. Y3 Cout Y2 Y1 Y0 4-bit binary adder Cin B3 B2 B1 B0 A3 A2 A1 A0 Figure 6.7 External signals of a 4-bit binary adder At this stage, the reader may be shared with a fact that apart from the purpose of simple 4-bit binary addition, the circuit illustrated in Figure 6.7 is incorporated in various other operations and, therefore, may be designated as one of the most widely used building blocks in digital circuits. Later in this chapter, we will discuss about a few more applications of this 4-bit binary adder. 6.1.4 Carry Look Ahead Adder In Section 5.12.2, we have introduced the term propagation delay, related to electronic circuits. We may recall that this propagation delay may be attributed to the activation and deactivation of diodes and transistors within any electronic circuit, which demands very small but a finite amount of time, say a few nanoseconds. The multi-bit adder circuit that we have discussed above is also affected by the propagation delay. This means that the generation of any one of its carry-out signal needs a few nanoseconds after receiving the corresponding stable input. Therefore, for any multi-bit adder circuit, this propagation delay will be cumulative as every carry-in is the outcome of the previous carry-out, because the carry propagates from one side to another like a ripple. This might create some amount of unwanted delays to generate the accurate final output after a valid initial input. For the purpose of visualization, we may consider a 64-bit adder composed of 16 numbers of 4-bit binary adders—the same module as depicted in Figure 6.7. If we assume that the generation of each carry-out after a valid carry-in input takes 3 ns, then for 4-bit addition, it will demand 12 ns. Therefore, for 64-bit addition we will receive the final carry-out after 16×12 = 192 ns. The same logic is equally valid even for the sum output, as the sum is also dependent on the carry-out of the previous bit. 199 200 Digital Electronics ? Confusion Clearing Corner This carry propagation is very much similar to the collapsing of a card-house where one card falls over the next one, propagating the card-collapsing from one side to another. To overcome this problem, an additional circuit is incorporated within the adder circuit which looks ahead (backwards) and decides for any eventual carry directly. This is known as the carry look ahead adder. To understand the concept behind this design, we have to clearly visualize the conditions of carry-generation and carry-propagation. 6.1.4.1 Carry Generation Carry is generated only if both the input bits are 1, that is, if A and B are the two input bits, then to generate any carry, both of these bits must be 1. Otherwise carry will not be generated. The reader may think that even if the value of one of these two bits A or B is 0, a carry may still be generated if the carry-in bit is 1. The reader may note that such a case is called carry-propagation (not carry-generation) and we will discuss it during carry-propagation. Please note that generation and propagation are two different activities. If we designate G as the carry-generation function, then we may express our observation as G = A ◊ B (6.1) If we consider the present bit as the nth bit, then we may rewrite the above function as Gn = An ◊ Bn (6.2) 6.1.4.2 Carry Propagation A carry is propagated if any one of the two input bits A or B is 1. If both A and B are 0, a carry will never be propagated. On the other hand, if both A and B are 1, then it will not propagate the carry but will generate the carry, as already described above. If we designate P as the carry-propagation function, then we may express it as Pn = An ⊕ Bn (6.3) To further clarify the concept, let us go through the truth table of the full adder that we have already observed in Table 6.2, which is reproduced here as Table 6.3. Here, within the column of Carryout, the symbols differentiate carry-generation and carry-propagation. From the above discussions, it should be clear that the generation or propagation of a carry depends primarily on the A and B inputs of the currently concerned bit and does not primarily depend on the status or condition of the previous bits or Carryin bit. Reader, Remember! Even if carry-in is 1, no carry will be generated if both A and B are 0. This is the reason for considering A and B as the primary contributors of the carry-propagation function. Digital Arithmetic Table 6.3 Carry-generation and carry-propagation Carryin 0 0 0 0 1 1 1 1 Input P 0 0 1 1 0 0 1 1 Q 0 1 0 1 0 1 0 1 Y 0 1 1 0 1 0 0 1 Output Carryout 0 0 0 1☼ 0 1� 1� 1☼ Legend: ☼ indicates carry generated � indicates carry propagated ? Confusion Clearing Corner The reader may note that (see Table 6.3) Cout must be 1 if the carry is generated or propagated. If Cout is 0, then the carry is neither generated nor propagated. Secondly, if both A and B are 1, then it is a case of carry-generation. If it is not a case of carry-generation, then if Cout is 1 and Cin is also 1, then it is a case of carry-propagation. 6.1.4.3 Look Ahead Expressions Now, if we consider the nth bit of a multi-bit adder, then the sum (S) and the carry-out (C) for that nth bit may be expressed in terms of the carry-generation function (G) and the carry-propagation function (P) as Sn = Pn + Cn−1 Cn = Gn + Pn ◊ Cn−1 (6.4) (6.5) However, we already know that for any full adder, the sum and the carry for any bit (say n) may be expressed as (see Figure 6.4) Sn = An ⊕ Bn ⊕ Cn−1 (6.6) Cn = AnBn + Cn−1 (An + Bn) (6.7) Considering Eqs. (6.4) and (6.6), we may express Pn as Pn = An ⊕ Bn Considering Eqs. (6.5) and (6.7), we may express Gn as (6.8) Gn = An ◊ Bn Therefore, using Eq. (6.5), we may express the carry output for the first bit (bit 0 or n = 0) as (6.9) where C0 = G0 + P0C−1 (6.10) G0 = A0 ◊ B0 (6.11) 201 202 Digital Electronics and P0 = A0 ⊕ B0 Therefore, after replacing the values of G0 and P0 in Eq. (6.10), we obtain (6.11a) C0 = A0 ◊ B0 + C−1 (A0 ⊕ B0) Similarly, from Eq. (6.5), we may express the carry output for the second bit (bit 1 or n = 1) as (6.12) C1 = G1 + P1C0 By replacing the value of C0 using Eq. (6.10), we may rewrite this as (6.13) C1 = G1 + P1 (G0 + P0C−1) which may be expanded as (6.14) C1 = A1 ◊ B1 + (A1 ⊕ B1)(A0 ◊ B0 + (A0 ⊕ B0) C−1) (6.15) Proceeding in the same way, we may develop the expressions for C2 and C3. Then we may construct the circuit for a 4-bit carry look ahead. However, for easier understanding, let us construct the circuit of a 2-bit carry look ahead. Note that after we complete the design of the 2-bit carry look ahead, we will use it to construct the circuit of a 2-bit carry look ahead adder. 6.1.4.4 2-bit Look Ahead Circuit To construct the circuit for a 2-bit carry look ahead, we will use Eqs. (6.10) and (6.14). We will consider P0, G0, P1, G1, and C−1 as the inputs. The outputs will be C0 and C1. The circuit is illustrated in Figure 6.8. The reader may note that the upper part of the circuit (output = C0) is constructed following Eq. (6.10), while the lower part (output = C1) is constructed using Eq. (6.14). With this 2-bit look ahead circuit, we are now in a position to construct the circuit of a 2-bit carry look ahead adder. C-1 P0 G0 P1 C0 C1 G1 Figure 6.8 2-bit carry look ahead circuit Reader, Remember! From Figure 6.8, it may be observed that both C0 and C1 will be available at the same time (constant delay) as both are generated by 2-stage gates. Even for a 4-bit look ahead circuit, the delay will remain the same as the delay is not dependent upon the number of bits. Digital Arithmetic 6.1.4.5 2-bit Carry Look Ahead Adder Circuit In this 2-bit case, we have taken A0, B0, A1, B1, and C−1 as the inputs as illustrated in Figure 6.9. The reader may wonder that if we are concerned with the bit-0 (LSB) of the input, then why is C−1 considered. As a matter of fact, it should not be considered in the case of the addition of LSB. However, these look ahead adders are used in cascade to take care of the multi-bit addition, and in such cases, C−1 will be necessary. In case of addition of LSB, C−1 may be connected with GND to make it 0. C-1 A0 B0 C-1 G0 A1 B1 C-1 P0 P1 2-bit carry look ahead G1 C1 P0 C0 S0 S1 P1 C1 Figure 6.9 A 2-bit carry look ahead adder The 2-bit carry look ahead circuit shown in Figure 6.8 forms the heart of the 2-bit carry look ahead adder circuit and is represented by a rectangular box in Figure 6.9. Note that the final output of this circuit will be S0, S1, and C1. The concept explained for a 2-bit circuit may be extended to a 4-bit circuit. Time to Take a Test If A = 1, B = 1, and Cin = 1, then is it a case of carry-generation or carry-propagation or both? 6.1.5 Integrated Circuit Parallel Adder Integrated circuits are commercially available to perform binary addition. A few of these ICs are presented through Table 6.4. Note that the 4-bit look ahead carry generator is available as a separate package. All of these ICs are designed for cascading to cater for multi-bit operations. Out of the ICs of Table 6.4, we will refer 7483 and use it in different application circuits. Therefore, we briefly introduce 7483 at this place. The external pin diagram along with the signal nomenclature of IC 7483 is shown in Figure 6.10. Observe that although functionally 7483 and 74283 are identical, their pin configurations are different. In the case of 74283, pin 8 will be GND and pin 16 will be Vcc. IC 7483 allows two 4-bit binary operands A1–A4 and B1–B4 along with a carry input designated as C0. The carry-out is C4, and S1–S4 will contain the 4-bit sum of the input. As already indicated, the device contains a carry look ahead circuit and is capable of performing the 4-bit addition within an average time of 15 ns. Answer to TTTT: This is a case of carry-generation as both A and B are 1. In this case, Cin does not matter. 203 204 Digital Electronics Table 6.4 Adder ICs Part number Description Number of IC pins Type Comments SN7480 1-bit gated full adder 14 LSI Suitable for cascading SN7482 2-bit binary full adder 14 MSI Suitable for cascading SN7483 4-bit binary full adder 16 MSI With in-built carry look ahead SN74182 Look ahead carry generator 16 MSI 4-bit SN74283 4-bit binary full adder with fast carry 16 MSI Pin configuration is different from 7483 A4 1 16 B4 S3 2 15 S4 A3 3 14 C4 B3 4 13 C0 5 12 GND S2 6 11 B1 B2 7 10 A1 A2 8 9 S1 Vcc 7483 Figure 6.10 Pin diagram of 7483 (4-bit binary full adder) 6.2 BCD Addition In Chapter 2 (see Section 2.5), we have introduced the BCD numbers where each decimal digit is expressed through a 4-bit binary equivalent. The reader may refer to Table 2.2 for the conversion of BCD into other number systems. Although BCD counters and BCD to 7-segment decoder cum drivers (7447) are more common in application areas, the BCD addition through a dedicated electronic circuit is not so common in industry. However, it will be interesting for the reader to be acquainted with the special circuit features necessary for the BCD addition. The BCD addition is performed with BCD numbers as inputs. The output of the addition will also be in BCD. The addition operation is performed in group of 4 bits of binary numbers representing one BCD digit. The general rule followed in this addition is, if the result exceeds 9, then add 6. We explain this through an appropriate example. Let us assume that we will add decimal 8 to decimal 4, and we know that the result will be decimal 12. Note that although the inputs are of one decimal digit, the result is of two decimal digits. Now, the BCD equivalent for decimal 8 will be 1000 and BCD for decimal 4 will be 0100. Adding both will produce 1100 in binary. Observe that the decimal equivalent of binary 1100 is 12. However, the BCD equivalent of decimal 12 will be 8-bit wide (4-bit/BCD digit × 2 BCD digits) 0001 0010. Remember that in BCD, it becomes Digital Arithmetic 8-bit binary as each BCD digit is converted into 4-bit binary. To convert the binary result 1100 into its BCD equivalent 00010010, or for any binary to BCD conversion after a BCD addition, we adopt the following procedures: Step 1: Check if the result of the addition is more than 9. If not, no action required. Step 2: If yes, then add 6 to the result. Step 3: Consider the carry obtained after the addition of 6 for the next BCD digit. Going back to our example, as the result of our BCD addition of 1000 and 0100 is 1100, which is more than 9, we add 6 (or 0110 in binary) to the result. The result is now changed to 10010 in 5-bit format or 00010010 in 8-bit format, whose corresponding BCD value is 12. 6.2.1 BCD Adder The maximum value of both BCD operators in the case of BCD addition will be 9 in decimal. Therefore, the range of the sum will vary from 0 (if both BCD operators are 0) to 18 in decimal (if both BCD operators are 9 in decimal). The binary representation of all the possible outputs of the single-digit BCD addition is presented in Table 6.5. Table 6.5 Binary range of 1-digit BCD addition S3 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 S2 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 S1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 S0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 Cout 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 X (indicates sum more than 9) 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 Sum in decimal 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 In this table we have incorporated a variable X, which is 1 if the result of the addition is more than 9; otherwise, the value of X is 0. We may now formulate the relation to generate X from S0, S1, S2, S3, and Cout. We may observe from Table 6.5 that 205 206 Digital Electronics (i) (ii) (iii) (iv) X must be 1 if Cout is 1. (This incorporates decimal range from 16 to 18). X must be 1 if both S2 and S3 are 1s (takes care of range from 12 to 15). X must be 1 if both S1 and S3 are 1s (covers the range from 10 to 11). In all the remaining cases, X must be 0 (remaining range from 0 to 9). It is now possible for us to construct a circuit incorporating these features. We may use any 4-bit full adder available to us (say 7483). The input for the first adder will be two BCD digits with any eventual carry from the previous BCD digit addition. The main output from this adder, namely S0–S3, may be directly fed to one of the 4-bit inputs of the second adder, say, into A0–A3. The carry-in input of this second adder is to be permanently grounded along with the B0 and B3 input pins. To verify whether the result of the BCD addition is greater than 9 or not, and if eventually it is more than 9, then to add 6 to the result, we will use two 2-input AND gates and one 3-input OR gate as shown in Figure 6.11. Note that the input of the first AND gate is obtained from S1 and S3 outputs of the first adder. The input for the second AND gate is obtained from S2 and S3 outputs of the first adder. The output from both of these AND gates along with the carry-out output of the first adder are fed to the 3-input OR gate. The output from this 3-input OR gate is directly connected with the B1 and B2 inputs of the second adder. The reader is encouraged to verify that the following circuit checks the condition and, if necessary, adds 6 to the result. Otherwise, the circuit will add zero and allow the output from the first adder to pass undistorted through the second adder. BCD output with carry S0 S1 S2 S3 Cout 4-bit Binary Full Adder A A0 A1 A2 A3 B0 B1 B2 B3 S0 S1 S2 S3 Cin Cout 4-bit Binary Full Adder A0 A1 A2 A3 B0 B1 B2 B3 Cin Two BCD digits' input with carry Figure 6.11 BCD adder with carry using 7483 Digital Arithmetic To conclude our discussions on BCD addition, the reader may be reminded that as a normal practice, BCD addition is performed with multiple BCD digits, and the BCD adder we have designed will be necessary in multiple numbers depending upon the number of BCD digits for the BCD operators. Time to Take a Test Perform BCD addition of 64 and 46. 6.3 Binary Subtraction Algebraically, the process of subtraction is similar to the process of addition, with only one difference. In the case of subtraction, the sign plays a role. Take the case of the addition of positive integers. The result will always be positive and we need not worry about its sign. Now, take the case of the subtraction of positive integers. Depending upon the magnitude, the result might be either positive or negative. There are several methods to construct the circuit for performing subtraction. We may conduct it either by direct straightforward method, which we are about to discuss in this section, or we may adopt the 2’s complement scheme, which we will discuss in the next section. The reader may recall that we have already introduced the 2’s complement method of number representation in Chapter 2 (see Section 2.7.2). 6.3.1 Half Subtractor If we consider P and Q to be two binary operators, each with only one binary digit, then the result of subtraction, P – Q, may be any one of the following four, depending upon the magnitudes of P and Q: Binary variable P Binary variable Q Result (P − Q) 0 −0 = 0 0 −1 = 1 Borrow = 1 1 −0 = 1 1 −1 =0 The truth table for 1-bit subtraction with two operators P and Q as inputs and Y as the output is presented in Table 6.6. The reader may compare this table with Table 6.1—the table we have prepared for 1-bit binary addition. Note that the situation of Table 6.6 will be different if Y = Q − P, whereas in the case of Table 6.1, it will remain the same if Y = Q + P. Therefore, in the case of subtraction, even if we consider it as algebraic addition, we must know which one of the two operators is having the negative sign; in our case, it is Q. The comparison between Tables 6.1 and 6.6 indicates that the Y output is identical in both cases. Therefore, we may form the expression Y = P ⊕ Q (6.16) Answer to TTTT: 64 = 0110 0100 and 46 = 0100 0110. The BCD addition of the two rightmost digits gives 1010 which is more than 9. Therefore, adding 0110 with it produces 0000 with a carry of 1. The addition of the next two BCD digits along with the carry gives 1011, which is again more than 9. Therefore, adding 0110 gives 0001 with a carry 1. Therefore, the final result is 0001 0001 0000 in BCD or 110 in decimal. 207 208 Digital Electronics However, for binary addition, the condition P = Q = 1 generated a carry. In the case of binary subtraction, P = 0 and Q = 1 produces a borrow. We may express it by C = P– ◊ Q (6.17) Therefore, we may slightly modify the half-adder circuit we have designed and incorporate an inverter gate with P before ANDing it to generate the C output. The relevant half-subtractor circuit is shown in Figure 6.12. Carryout (Borrow) Table 6.6 Binary subtraction (1-bit) P Q Y=P−Q Comments 0 0 0 Borrow = 0 0 1 1 Borrow = 1 1 0 1 Borrow = 0 1 1 0 Borrow = 0 Y P Q Figure 6.12 Half-subtractor circuit (Y = P − Q) 6.3.2 Full Subtractor The limitation of the half-subtractor circuit discussed above is its inability to cater for multi-bit subtraction, where borrow from one bit propagates to the next bit, as there is no provision for borrow-in (in the halfsubtractor circuit). To eliminate this problem, we may design the full subtractor which will perform one-bit subtraction in multi-bit operations. The truth table for the full subtractor is presented in Table 6.7. The reader may note the differences between Tables 6.7 and 6.2. Table 6.7 Truth table for full subtractor Input Carryin P 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 Q 0 1 0 1 0 1 0 1 Output Y = P − Q – Carryin 0 1 1 0 1 0 0 1 Carryout 0 1 0 0 1 1 0 1 From this truth table, we can generate the K-map and then form the expressions for Y and Carryout, as shown in Figure 6.13. If the reader is interested to compare these expressions with the expressions obtained for the full adder (see Figure 6.4), then it might be observed that the expressions for Y in both the cases are Digital Arithmetic identical. However, the expressions for carry-out differ for the P input. In the case of full adder, it was P; in the case of full subtractor, it is P–. PQ PQ PQ PQ PQ PQ PQ PQ Carryin 0 1 0 1 Carryin 0 1 0 0 Carryin 1 0 1 0 Carryin 1 1 1 0 K-map for Y K-map for Carryout Y = Carryin PQ + Carryin PQ + Carryin PQ + Carryin PQ Carryout = PQ + Carryin P + Carryin Q = Carryin (PQ + PQ) + Carryin (PQ + PQ) = Carryin (P ≈ Q) + Carryin (P ≈ Q) = Carryin ≈ P ≈ Q (a) (b) Figure 6.13 K-map of full subtractor From the derived expressions, we may now construct the circuit of the full subtractor, which is presented in Figure 6.14. This circuit may be compared with the circuit of the full adder presented in Figure 6.3. The reader may note that the only difference is the inclusion of one NOT gate in the full-subtractor circuit. Carryout Y Carryin P Q Figure 6.14 Circuit for full subtractor The method of binary subtraction we have followed here may be designated as the direct method. However, this is not the only method for binary subtraction. In the following section, we discuss about another popular method for binary subtraction. 209 210 Digital Electronics Time to Take a Test Redesign the full-subtractor circuit using two half subtractors and logic gates. 6.4 2’s Complement System The reader may recall that in Chapter 2 (see Section 2.7.2), we have introduced 2’s complement method of sign representation. In that section, through one example (5 − 4 = 1) we have indicated that one of the advantages of 2’s complement format is that it is capable of performing subtraction by addition. Let us consider another example here. Let us calculate 14 − 3 when both are in decimal. As per our method, we first calculate 1’s complement of the number to be subtracted. The binary equivalent of 3 is 0011 (in 4-bit format) and its 1’s complement is 1100. To calculate its 2’s complement, we add 1 to it or, in other terms, increment it by 1. In that case, 1100 becomes 1101. We will add this 1101 to the binary equivalent of 14, which is 1110. Now, 1110 + 1101 gives us 1011 with carry as 1. The decimal equivalent of 1011 is 11, which is the correct result of the subtraction (14 − 3 = 11). The reader may ask a question here that what will be the outcome of 3 − 14 if both are in decimal. In this case, the result should be −11 in decimal. Let us see what happens if we adopt the same procedure of 2’s complement addition. As the binary equivalent of 14 is 1110, therefore, its 1’s complement is 0001 and its 2’s complement is 0010. When this is added to the binary equivalent of 3, that is, 0011, the result of the binary addition is 0101, with no carry. Now, the decimal equivalent of 0101 is 5. We expected to obtain the result of −11 in decimal. Then where have we gone wrong? We are not wrong. The answer we have obtained is correct, but in 2’s complement form. To convert it into its normal form, we first subtract 1 from it, making it 0100, and then complement it, which gives 1011. Note that 1011 in binary is 11 in decimal. So, our procedure was correct. Only thing remains is to correctly interpret it. The rules for interpreting the result of subtraction using 2’s complement method are as follows: (i) If there is a carry-out after 2’s complement addition, the result is positive. Neglect the carry. (ii) If there is no carry after 2’s complement addition, the result is negative and is in its 2’s complement form. Convert it into its normal binary form to get the absolute value without its sign. Reader, Remember! The interpretation of 2’s complement addition is very important. If carry is not generated, it becomes even more important. Recall Sherlock Holmes’ famous comment about curious behavior of dogs regarding the missing horse case. Answer to TTTT: A P B Q Cin Half subtractor Y P P Co Q Half subtractor Y Co A–B Cout Digital Arithmetic 6.4.1 1’s Complement Constructing a circuit to perform 1’s complement of any binary input is rather easy. Assuming a group of four binary digits, we incorporate four NOT gates for this purpose, as shown in Figure 6.15. In this case, 4-bit — — input (D0 – D3) will be complemented at the output as 0 – 3. Complemented 4-bit output D3 D2 D1 D0 D3 D2 D1 D0 4-bit input Figure 6.15 Circuit for 1’s complement (4-bit) 6.4.2 2’s Complement After obtaining 1’s complement, 2’s complement may be obtained by adding 1 to it. For this purpose, any adder may be used, and if the input is available in a group of four bits, 4-bit full adders such as 7483 might be used. The relevant circuit for 2’s complement is shown in Figure 6.16. 2's complement output S3 S2 S1 S0 Cout 4-bit binary full adder B3 B2 A3 A2 A1 A0 B1 B0 Cin Vcc D3 D2 D1 D0 4-bit input Figure 6.16 Circuit for 2’s complement (4-bit) In Figure 6.16, we may note that the complemented input (D0–D3) is fed to one of the 4-bit inputs (A0–A3) of the 4-bit full adder, and other 4-bit input of the adder is connected with the ground to input zero. The Cin input is connected with Vcc so that 1 is added to the complemented input. The final output is available from S0–S3. Note that Cout = 1 to be neglected. 211 212 Digital Electronics ? Confusion Clearing Corner The term 2’s complement indicates either the operation (complement and add one) or the format (sign-bit representation, 2’s complement representation). Generally, the context will clarify the doubt regarding the usage. Time to Take a Test In the light of 1’s complement and 2’s complement, express 9’s complement and 10’s complement. 6.4.3 Subtraction with 2’s Complement Once we are ready to implement 2’s complement circuit, the remaining part of the circuit is an easier one. The complete circuit capable of 2’s complement subtraction is shown in Figure 6.17. Note that this arrangement is capable of computing B − A, both B and A operators being 4-bit. The circuit also considers any eventual carry generated from the previous modules. For the first module, the carry-in input of the top-adder should be grounded. 4-bit output with carry S3 S2 S1 S0 Cout 4-bit binary full adder B3 B2 A3 A2 A1 A0 B1 B0 Cin Cin B3 B2 B1 B0 4-bit input B S3 S2 S1 S0 Cout 4-bit binary full adder B3 B2 A3 A2 A1 A0 B1 B0 Cin Vcc A3 A2 A1 4-bit input A A0 Figure 6.17 4-bit subtraction using 2’s complement for B − A Answer to TTTT: To obtain 9’s complement, substract each decimal digit from decimal 9. Add one to it to generate 10’s complement. Digital Arithmetic 6.5 ALU Integrated Circuits Integrated circuits are commercially available to perform various arithmetic and logical operations described in this chapter and also in Chapter 3. These ICs are designated as arithmetic logic unit (ALU). Generally, these ALUs function with 4-bit operators. However, they might be cascaded for wider operators. IC 74181 is such an ALU capable of performing arithmetic and logical operations with 4-bit operators. Observe that this IC is based on combinational logic and not on the sequential logic. Its pin and signal diagram is presented in Figure 6.18. Note that this 24-pin IC accepts two 4-bit inputs, namely A0–A3 and B0–B3, along with a carry input Cn. The 4-bit result is available through F0–F3 along with a carry-out bit Cn + 4. B0 1 24 Vcc A0 2 23 A1 S3 3 22 B1 S2 4 21 A2 S1 5 20 B2 S0 6 19 A3 Cn 7 18 B3 m 8 17 G F0 9 16 Cn + 4 F1 10 15 P F2 11 14 A=B GND 12 13 F3 74181 4-bit ALU Figure 6.18 Pins and signals of 74181 (4-bit ALU) (Courtesy: Texas Instruments) Reader, Remember! As multiplication and division operations need clock pulses, which makes the circuit a sequential one, these functions are not available in the 74181 ALU because it is based on combinational logic. Its select input S0–S3 selects one of the sixteen functions for any one of the two modes, logical or arithmetic, which is decided by the condition of the external input m. A special output A = B indicates that both the input parameters are equal in magnitude. The G and P outputs indicate carry look ahead status. The functional block diagram of 74181 is presented in Figure 6.19. 213 214 Digital Electronics Vcc Data in Cn Cn + 4 A0–A3 4 F0–F3 B0–B3 4 4 74181 Result out A=B 4-bit ALU m Select S0–S3 G Status P 4 GND Figure 6.19 Functional block diagram of 74181 ALU ? Confusion Clearing Corner A = B output is necessary for cascading multiple 74181 for comparison operation. G and P outputs are necessary for carry look ahead during cascading. Table 6.8 shows all arithmetic (m = 0) and logical (m = 1) functional details for each select input (S0 – S3). The reader may note that the arithmetic addition and subtraction are indicated by plus and minus, respectively, while the logical OR operation is denoted by +sign to distinguish between the two. AB denotes A AND B. Table 6.8 Select function for 74181 ALU Selection Active-low data m = 0 (arithmetic) m=1 (logical) F = A– F = A minus 1 F=A 0 0 1 0 — F = AB F = A– + B F = AB minus 1 F = AB– minus 1 F = AB F = AB– 0 0 1 1 F=1 0 1 0 0 0 1 0 1 F= A+B F = B– F = AB plus (A + B–) 0 1 1 0 F= A≈B F = A minus B minus 1 S3 S2 S1 S0 0 0 0 0 0 0 0 1 Cn = 0 F = minus 1 (2’s complement) F = A plus (A + B–) Cn = 1 F = zero F = A plus (A + B–) plus 1 F = AB plus (A + B–) plus 1 F = A minus B (Contd.) Digital Arithmetic 1 0 0 0 F = A + B– F = A–B 1 0 0 1 F=A⊕B 1 0 1 0 F=B 1 0 1 1 F=A+B F = (A + B) F = (A + B) plus 1 1 1 0 0 F = A plus A F = A plus A plus 1 1 1 0 1 F=0 F = AB– 1 1 1 0 F = AB F = AB plus A F = AB– plus A F = AB plus A plus 1 F = AB– plus A plus 1 1 1 1 1 F=A F=A F = A plus 1 0 1 1 1 F = A + B– F = (A + B–) plus 1 F = A plus (A + B) F = A plus (A + B) plus 1 F = A plus B F = AB– plus (A + B) F = A plus B plus 1 F = AB– plus (A + B) plus 1 IC 74181 is capable of handling 4-bit data. However, it may be cascaded to handle wider data sets, if felt necessary. The reader may note that its Cn + 4 output (carry-out) is of open-collector type and needs an external pull-up resistor for proper output indication. Reader, Remember! If the reader is constructing a circuit with 74181, then one 10K pull-up resistor is to be connected between Vcc and pin 16 of 74181. 6.6 Digital Comparator Comparators perform the comparison of magnitudes of two inputs. When both inputs are analog, it is called an analog comparator. On the other hand, if both inputs are digital, then it is designated as a digital comparator. Digital comparators are simpler in operation and design, having three types of outputs, namely A = B, A < B, and A > B, when A and B are the input data. Depending upon the input conditions, one of these three output indicates HIGH (1) or true, while the remaining two indicate LOW (0) or false. Therefore, when both inputs are of 1-bit, the truth table of a comparator will be as shown in Table 6.9. Table 6.9 Truth table for a 1-bit comparator Input Output A B A>B A<B A=B 0 0 0 0 1 0 1 0 1 0 1 0 1 0 0 1 1 0 0 1 From this truth table, we can generate the K-maps for A < B, A = B, and A > B, and then design the circuit to perform the comparison operation, as shown in Figure 6.20. 215 Digital Electronics B A A<B A=B A>B Figure 6.20 Circuit for a 1-bit comparator ? Confusion Clearing Corner Throughout the section of comparator, we are assuming all the inputs to be in unsigned binary integer form and never in 2’s complement form. 6.6.1 Cascading Inputs Using the same principle, we may design a 2-bit comparator or a 4-bit comparator. Commercially, 4-bit comparator ICs are available from different manufacturers. For wider input data such as 8-bit or 16-bit, the 4-bit comparator ICs may be used in cascade. For this purpose, cascading inputs are also provided in these ICs. To understand the principle of cascading, we may cascade two 1-bit comparators. Schematically, it is presented through Figure 6.21. A=B data-in A B A0 B0 A>B A<B A<B A=B A=B A>B data-in A B Output A<B A>B cascade input Vcc Output A>B cascade input 216 A<B A=B A1 B1 Figure 6.21 Schematic of cascaded pair of 1-bit comparators 6.6.2 Truth Table for 1-Bit Comparator with Cascading Inputs The reader may note that in Figure 6.21, all three outputs from the lower comparator (for LSB, at left) become cascading inputs for the higher comparator (for MSB, at right). Therefore, the comparator is to first Digital Arithmetic investigate its own data-in, and if they are equal (A = B), then only the cascading inputs will be considered by it. We may now prepare the truth table for this 1-bit comparator with the cascading inputs, which is presented in Table 6.10. Table 6.10 Truth table for a 1-bit comparator with cascading inputs Data inputs Cascading inputs A B A>B 0 0 0 0 1 0 0 0 1 0 0 1 0 0 1 0 0 1 0 1 1 Outputs A<B A=B A>B A<B A=B 0 0 1 0 0 1 0 0 1 0 0 0 1 0 1 0 0 1 0 0 1 0 1 0 0 0 1 0 0 0 0 1 1 0 0 1 0 0 1 0 1 0 0 1 0 1 0 0 1 0 0 1 1 0 0 1 0 0 1 1 1 0 1 0 0 1 0 1 1 1 0 0 1 0 0 6.6.3 Initial Design We now proceed to design the circuit from this truth table. Although initially the truth table seems to be complex, we may simplify it through our careful observations. First, we observe that if A = 0 and B = 1, then the output will always be A < B = 1, without any influence of the three cascading inputs. This allows us to replace the logic values of the cascading inputs of these three rows by the “don’t-care” symbol ×. Secondly, we observe that the same logic is applicable for A = 1 and B = 0 input conditions. In this case also the cascading inputs do not matter and the output becomes A > B = 1. Therefore, another three rows will contain the × symbol for the cascading inputs. We now present the modified truth table in Table 6.11 after incorporating the outcome of these two observations. Table 6.11 Truth table for 1-bit comparator with cascading inputs (modified) Data inputs A B 0 0 0 0 0 0 0 1 0 1 Cascading inputs Outputs A>B A<B A=B A>B A<B A=B 0 0 1 0 0 1 0 1 0 0 1 0 1 0 0 1 0 0 × × × 0 1 0 × × × 0 1 0 (Contd.) 217 218 Digital Electronics 0 1 1 1 1 1 1 1 0 0 0 1 1 1 × × × × 0 0 1 × × × × 0 1 0 × × × × 1 0 0 0 1 1 1 0 0 1 1 0 0 0 0 1 0 0 0 0 0 1 0 0 As the 4th, 5th, and 6th rows of the table are identical, therefore, we may delete the 5th and 6th rows from the table, keeping only the 4th row. Similarly, the 8th and 9th rows may also be deleted, as they are similar to the 7th row of the table. This modified table is presented in Table 6.12. Observe that now the rows are less in number. Table 6.12 Truth table for 1-bit comparator with cascading inputs (further modified) Data inputs Cascading inputs Outputs A B A>B A<B A=B A>B A<B A=B 0 0 0 0 1 0 0 1 0 0 0 1 0 0 1 0 0 0 1 0 0 1 0 0 0 1 × × × 0 1 0 1 0 × × × 1 0 0 1 1 0 0 1 0 0 1 1 1 0 1 0 0 1 0 1 1 1 0 0 1 0 0 Now, let us observe the first three and the last three rows of the table. These rows deal with equality condition of A and B data inputs. If both A and B are 0s or both A and B are 1s, then the present cascading inputs become the output. Therefore, we may formulate our first expression for design as ∑ If both the data inputs are equal, then the output will be the cascading input. Our second expression for design is ∑ If A = 0 and B = 1, then the output will be A < B = 1 (A > B = 0, A = B = 0). Our third and final expression for design is ∑ If A = 1 and B = 0, then the output will be A > B = 1 (A < B = 0, A = B = 0) 6.6.4 Detailed Design Step 1 So we are now successful to compress Table 6.10 into the above three design expressions. To start our design, we take up the equality condition (the first expression). To generate the condition A = B for all inputs of A and B, we may use a XNOR gate. The reader may be curious about this decision. Why not a XOR gate in this case? The answer is, we need logic 1 condition at the output when both data inputs (A and B) are 1, for further processing, to be discussed in step 3. If we use a XOR gate, then we will get logic 0 as the output for equality condition. We may now present the initial stage of our circuit in Figure 6.22. The reader may note that in Figure 6.22, we have shown all inputs and all outputs apart Digital Arithmetic from the XNOR gate. The relevant circuit for the remaining part will be discussed and completed step by step. A=B A=B A<B A>B A<B A>B A B Figure 6.22 Circuit for 1-bit comparator with cascading inputs (step 1) Step 2 We may now look at the second and third design expressions. If data inputs are A = 0 and B = 1, then the output will be A < B = 1. On the other hand, if data inputs are A = 1 and B = 0, then the output will be A > B = 1. Using two NOT gates and two 2-input AND gates, we can complete this part of the circuit, and this stage of circuit design is presented in Figure 6.23. A=B A=B A<B A>B A<B A>B A B Figure 6.23 Circuit for 1-bit comparator with cascading inputs (step 2) Step 3 We now take up the further processing part, which we have indicated in step 1. From Table 6.12, we can observe that if the data inputs A and B are equal in magnitude (indicated by the output of the XNOR gate), then the output will be the same as that of the cascading input (one of three). To implement 219 220 Digital Electronics this condition, we can place three more 2-input AND gates in the circuit. One of the two inputs of each of these three AND gates will be the output from the XNOR gate. Three cascading inputs will be other three inputs of these three AND gates. This design will generate the outputs A > B, A < B, and A = B. Note that the first two outputs need further processing. However, the third one we may accept as one of the three final outputs. The condition of our yet to be finished circuit is shown in Figure 6.24. A=B A=B A<B A>B A<B A>B B A Figure 6.24 Circuit for 1-bit comparator with cascading inputs (step 3) Step 4 In this fourth and the final step of our design, we note that using the data inputs A and B, we have already obtained (in step 2) one set of A > B and A < B outputs as shown in Figure 6.23. In step 3, we left a pair of outputs, A > B and A < B, for further processing. Now, it is the time to logically OR both the sets of outputs to generate the final A > B and A < B outputs. Using two 2-input OR gates, we complete that part and also complete the present circuit design, as shown in Figure 6.25. A=B A=B A<B A>B A<B A>B A B Figure 6.25 Circuit for 1-bit comparator with cascading inputs (step 4) Digital Arithmetic The reader is now encouraged to check and verify whether the designed circuit will function properly or not. 6.6.5 4-bit Comparator 74LS85 Output Cascade input ICs for multi-bit comparison are commercially available. 74LS85 is one of such ICs, which can perform 4-bit comparison and may be cascaded for operation with more number of bits as it offers cascading inputs. Pin and signal details of 74LS85 are shown in Figure 6.26. B3 1 16 Vcc A<B 2 15 A3 A=B 3 14 B2 A>B 4 13 A2 A>B 5 12 A1 A=B 6 11 B1 A<B 7 10 A0 GND 8 9 B0 74LS85 Figure 6.26 Pins and signals of 74LS85 (4-bit comparator) The truth table for 74LS85 is presented in Table 6.13. The reader may note that its last three rows indicate special cascading input conditions. Table 6.13 Truth table for 74LS85 Comparing inputs Cascading inputs Outputs A3, B3 A2, B2 A1, B1 A0, B0 A<B A=B A 3 > B3 × × × A>B A<B A=B A>B × × × H L L A 3 < B3 × × × × × × L H L A 3 = B3 A2 > B2 × × × × × H L L A 3 = B3 A2 < B2 × × × × × L H L A 3 = B3 A2 = B2 A1 > B1 × × × × H L L A 3 = B3 A2 = B2 A1 < B1 × × × × L H L A 3 = B3 A2 = B2 A1 = B1 A0 > B0 × × × H L L A 3 = B3 A2 = B2 A1 = B1 A0 < B0 × × × L H L A 3 = B3 A2 = B2 A1 = B1 A0 = B0 H L L H L L (Contd.) 221 222 Digital Electronics A3 = B3 A2 = B2 A1 = B1 A0 = B0 L H L L H L A3 = B3 A2 = B2 A1 = B1 A0 = B0 L L H L L H A 3 = B3 A2 = B2 A1 = B1 A0 = B0 × × H L L H A 3 = B3 A2 = B2 A1 = B1 A0 = B0 H H L L L L A 3 = B3 A2 = B2 A1 = B1 A0 = B0 L L L H H L 6.7 Solved Examples Example 6.1 Design a circuit to perform the 8-bit addition of unsigned binary integers. Using the designed circuit as an example, show the result of addition of 11011010B to 11100101B. Sol. The circuit may be developed by using two 7483 4-bit adder ICs, as shown in Figure 6.27. Note that the right-side adder handles the least significant 4 bits, while the left one takes care of the most significant 4 bits along with the carry. The carry input of the lower adder (C0, pin 13) is to be connected with the system reference ground to input logic 0 for all cases of addition. V+ 1 15 S4 14 C4 5 Vcc 12 GND C0 13 0 0 1 1 9 2 6 S3 S2 S1 1 V+ 14 C4 5 Vcc 12 GND 7483 4-bit binary adder B4 B3 B2 B1 4 7 11 16 1 1 0 1 A4 A3 A2 A1 1 1 3 8 10 1 1 1 1 1 1 9 15 2 6 S4 S3 S2 S1 0 C0 13 11011010 + 11100101 7483 4-bit binary adder B4 B3 B2 B1 4 7 11 16 1 0 0 1 0 A4 A3 A2 A1 1 0 = 110111111 3 8 10 1 0 1 Figure 6.27 8-bit parallel binary adder Each of the unsigned binary operators of the present problem is divided into two parts: the lower four bits are fed to the right-sided lower adder and the higher four bits to the left-side adder. Cascading is completed by connecting the carry-out signal of the lower adder (pin 14) with the carry-in input of the higher adder (pin 13). The Vcc input for both ICs has to be connected with a +5 V dc supply. The result of addition of the given operators will be available through S outputs of the devices along with carry-out from pin 14 of the left-sided adder. Example 6.2 Design a circuit for 2-digit BCD addition and then indicate how 97 added to 53 will produce the result. Digital Arithmetic Sol. The BCD equivalents of decimal 97 and 53 are 10010111 and 01010011, respectively. After the addition, the result becomes 150 in decimal or 101010000 in binary. The reader may observe that the result is 9-bit, although both the inputs are of 8-bit. The circuit for 1-digit BCD addition is expanded for 2-digit BCD operation, taking care of the carry-out propagation from the lower to the higher digit. The designed circuit is shown in Figure 6.28. The reader may note that for the least significant BCD digit, the carry-in input (C0) is grounded to input 0, while the carry-in input of the most significant BCD digit is connected with C4 output of the least significant BCD digit adder, for carry-out propagation. 0 1 5 12 9 6 2 S 4 S3 S2 S1 C4 Vcc V+ 5 7483 4-bit binary adder GND C0 13 0 1 15 14 V+ 0 1 B4 B3 B2 B1 4 7 11 16 12 C0 3 8 10 13 0 9 2 6 S3 S2 S1 S4 7483 4-bit binary adder GND A4 A3 A2 A1 1 15 14 C4 Vcc 0 0 B4 B3 B2 B1 4 7 11 16 A4 A3 A2 A1 3 8 10 1 97 + 53 = 150 V+ 5 12 15 2 6 9 S4 S3 S2 S1 14 C4 Vcc 7483 4-bit binary adder GND C0 13 B4 B3 B2 B1 16 0 4 7 11 1 0 1 V+ 5 3 8 10 1 7483 4-bit binary adder 12 GND C0 A4 A3 A2 A1 1 15 2 6 9 S4 S3 S2 S1 14 C4 Vcc 0 0 13 B4 B3 B2 B1 4 7 11 16 0 1 0 1 A4 A3 A2 A1 3 8 10 1 1 0 1 1 1 Figure 6.28 Circuit for 2-digit BCD addition with carry Example 6.3 In many computer systems, the numbers are stored and processed in 2’s complement format. Explain with suitable examples how addition operations are performed with 4-bit integers represented in 2’s complement format. Sol. In Chapter 2, through Table 2.6 we have presented 2’s complement numbers ranging from decimal −7 to +7. A modified version of Table 2.6 is reproduced here as Table 6.14 for ready reference to the reader. 223 224 Digital Electronics Table 6.14 Decimal and 2’s complement representation (4-bit) Decimal 2’s complement (4-bit) −7 1001 −6 1010 −5 1011 −4 1100 −3 1101 −2 1110 −1 1111 −0 0000 +0 0000 +1 0001 +2 0010 +3 0011 +4 0100 +5 0101 +6 0110 +7 0111 As examples, let us consider four separate cases of 2’s complement additions, as follows: (i) 2 + 5 = 7 (ii) 3 + (−6) = −3 (iii) −5 + 7 = 2 (iv) −4 + (−3) = −7 (i) For the first case, using Table 6.14, we express 2 and 5 in 2’s complement form as 0010 and 0101, respectively. Therefore, the addition of these two numbers will be performed as follows: 0010 → 2’s complement of +2 + 0101 → 2’s complement of +5 0111 → 2’s complement of +7 Note that the most significant bit (0) indicates that the result is positive. (ii) For the second case, using Table 6.14, we express 3 and −6 in 2’s complement form as 0011 and 1010, respectively. Therefore, the addition of these two numbers will be performed as follows: 0011 → 2’s complement of +3 + 1010 → 2’s complement of +6 1101 → 2’s complement of –3 Note that the most significant bit (1) indicates that the result is negative. Digital Arithmetic (iii) For the third case, using Table 6.14, we express −5 and 7 in 2’s complement form as 1011 and 0111, respectively. Therefore, the addition of these two numbers will be performed as follows: 1011 → 2’s complement of –5 + 0111 → 2’s complement of 7 1 0010 → 2’s complement of +2 As the carry in this case is 1, therefore, we discard the carry. Note that the most significant bit (0) indicates that the result is positive. (iv) For the fourth case, using Table 6.14, we express −4 and −3 in 2’s complement form as 1100 and 1101, respectively. Therefore, the addition of these two numbers will be performed as follows: 1100 → 2’s complement of –4 + 1101 → 2’s complement of –3 1 1001 → 2’s complement of –7 As the carry in this case is 1, therefore, we discard the carry. Note that the most significant bit (1) indicates that the result is negative. Therefore, in the case of 2’s complement addition, we discard the eventual carry and then decide the sign of the result from the content of the most significant bit. If it is 1, then the result is negative; if it is 0, then the result is positive. Example 6.4 Using same operators of above Example 6.3, perform 2’s complement subtraction. Sol. Considering identical operators of Example 6.3, in the case of subtraction we may represent the operations as follows: (i) 2 − 5 = −3 (ii) 3 − (−6) = 9 (iii) −5 − 7 = −12 (iv) −4 − (−3) = −1 (i) For the first case, using Table 6.14, we express 2 and −5 in 2’s complement form as 0010 and 1011, respectively. Therefore, the subtraction of these two numbers will be performed as follows: 0010 → 2’s complement of +2 + 1011 → 2’s complement of –5 1101 → 2’s complement of –3 Note that the most significant bit (1) indicates that the result is negative. (ii) For the second case, using Table 6.14, we express 3 and −6 in 2’s complement form as 0011 and 1010, respectively. Therefore, the subtraction of these two numbers, that is, 3 − (−6) will be performed as follows: 225 226 Digital Electronics 1010 → 2’s complement of −6 0101 → its 1’s complement 0110 → its 2’s complement +0011 → 2’s complement of +3 1001 → 2’s complement of +9 Finally, we have added 0110 to 0011, resulting in 1001. However, we have accepted so far that if the most significant bit is 1, then the number is negative. Does it mean that the result is −9 or have we gone wrong somewhere? Yes, we have made a small mistake. Referring to Table 6.14, we observe that the range for the 4-bit 2’s complement representation is from −7 to +7. As the sign is indicated by the most significant bit in the 2’s complement representation, therefore, practically we are allowed to use three bits for magnitude representation and the maximum range in this case is 7. Therefore, if any operator or the result exceeds 7, then we should consider extra bits. In this case, we should consider extra bits. In this example case we may consider 5 bits. However, the normal practice is to consider eight bits. Considering 8-bits for our 2’s complement representation, let us perform the whole operation again. This time it will be as follows: 11111010 → 2’s complement of −6 (in 8-bit format) 00000101 → its 1’s complement 00000110 → its 2’s complement +00000011 → 2’s complement of +3 (in 8-bit format) 00001001 → 2’s complement of +9 (in 8-bit format) Note that now the most significant bit (0) indicates that the result is positive. Reader, Remember! In 2’s complement representation, the range of numbers is decided by one less than the total number of bits. (iii) For the third case, using Table 6.14, we express −5 and −7 in 2’s complement form as 1011 and 1001, respectively. Therefore, the addition of these two numbers will be performed as follows: 1011 → 2’s complement of −5 +1001 → 2’s complement of −7 1 0100 → 2’s complement of +4 Here again we have faced the same problem, that is, out of range. The result in this case should be −12 in decimal. The binary equivalent of decimal +12 is 01100 using the 5-bit format. Its 2’s complement is 10011 incremented by 1, that is, 10100. Verify that this is the result we have obtained. Therefore, we have to be careful about the format and the range when we are about to adopt 2’s complement scheme. Digital Arithmetic (iv) For the fourth case, using Table 6.14, we express −4 and −3 in 2’s complement form as 1100 and 1101, respectively. As we have to subtract −3, therefore, we find its 2’s complement, which is 0011. Therefore, the addition of these two numbers would be performed as follows: 1100 → 2’s complement of −4 +0011 → 2’s complement of −3 1111 → 2’s complement of −1 Note that the most significant bit (1) indicates that the result is negative. Example 6.5 Design a circuit for 2-bit subtraction using 1-bit full subtractors. Sol. We have already discussed full subtractors in Section 6.3.2, and the designed circuit for 1-bit full subtractor was presented in Figure 6.14. This 1-bit full subtractor may be cascaded for a 2-bit subtraction. The circuit is illustrated in Figure 6.29 for the subtraction of B from A. The result is Y and Carryout. Note that both A and B are of two bits. The Carryin may be connected with the system GND if not necessary. Y1 Carryout A1 B1 Y0 Carryin A0 B0 Figure 6.29 2-bit subtractor using 1-bit full subtractors Example 6.6 Design a circuit using 74181 ALU to perform the addition of 1101 to 0110 when both are in binary. Assume carry-in to be 0. Sol. Referring to Table 6.8, we can find that the select input for addition operation should be 1001. As it is an arithmetic operation, therefore, m input is to be connected with GND. Because the carry-out is of open-collector type output, therefore, a 10K external pull-up resistor is necessary between Cn + 4 output and Vcc. 227 Digital Electronics The reader should note that 74181 is designed for active-low inputs. Therefore, the desired inputs for A and B must be inverted before allowing to pass to the IC pins. Note that Cn input need not be inverted, and so also the select inputs. The 4-bit output through F0–F3 is also available in activelow form. However, Cn + 4 is available in its normal form. The complete circuit with input–output details is presented in Figure 6.30. 1 10 K 1 0 14 17 15 A=B G P F3 F2 F1 F0 Vcc +5 V 1 0 13 11 10 9 16 Cn + 4 24 GND 74181 4-bit ALU Cn A3 A2 A1 A0 B3 B2 B1 B0 S3 S2 S1 S0 3 4 5 0 1 0 1 0 0 7 19 21 23 2 0 0 1 0 18 20 22 1 0 1 12 m 6 1 8 Figure 6.30 74181 ALU circuit for 4-bit addition (A plus B) Example 6.7 Design an 8-bit comparator by cascading two 4-bit comparators. Sol We may use a pair of 74LS85 for constructing the circuit as shown in Figure 6.31. The IC at the right side is for lower four bits, while the IC at the left side is for the upper four bits of input for both A and B. The output of the right-side IC is fed to the cascading input of the left-side IC. The A = B cascading input of the right-side IC is connected with +5 V to input logic 1. Other two cascading inputs are connected with the system GND. +5 V Output 228 7 A<B 6 A=B 5 A>B 16 Vcc +5 V 8 GND 74LS85 2 A<B 3 A=B A>B 4 7 A<B 6 A<B A=B 5 A>B 16 Vcc 8 GND 74LS85 A3 A2 A1 A0 B3 B2 B1 B0 A3 A2 A1 A0 B3 B2 B1 B0 A7 A6 A5 A4 B7 B6 B5 B4 A3 A2 A1 A0 B3 B2 B1 B0 15 13 12 10 1 14 11 9 15 13 12 10 +5 V 2 A<B 3 A=B 4 A>B 1 14 11 9 Figure 6.31 8-bit comparator circuit with 74LS85 Digital Arithmetic Chapter Synopsis ∑ Operation-wise 1-bit binary addition is similar to the XOR operation except the carry generation. ∑ Along with an AND gate, one XOR gate completes the half-adder circuit, without the provision of processing carry-in. ∑ A full adder considers carry-in as well as carry-out. ∑ Multiple full adders may be cascaded to form n-bit parallel binary adder. ∑ Due to the propagation delay, carry ripples over from bit to bit, which creates an undesirable delay in multi-bit addition. ∑ A carry look ahead circuit eliminates this problem at the cost of extra hardware overhead. ∑ IC 74182 is capable of functioning as a carry look ahead. IC 7483 implements 4-bit binary addition with carry look ahead. ∑ For BCD addition, if the sum exceeds 9, then 6 is added to normalize the sum to a BCD digit, with a carry. ∑ A half-subtractor circuit needs an extra NOT gate with respect to a half-adder circuit to perform onebit subtraction. ∑ A full-subtractor circuit is capable of considering carry-in, which is essential for multi-bit subtraction. ∑ Subtraction may also be performed by addition using 2’s complement method. ∑ ICs to perform arithmetic and logic operations are commercially available. ∑ IC 74181 is a 4-bit ALU capable of performing 16 arithmetic and 16 logical operations, selectable through select and mode inputs. ∑ Comparator circuits are capable of comparing two binary inputs and generating one of the three possible output conditions as true. These three conditions are A < B, A = B, and A > B, where A and B are the inputs. ∑ These inputs may be single-bit or multi-bit. In either case, a provision of cascading inputs is available so that the ICs might be cascaded with each other. ∑ In case of multi-bit comparison, higher bits are compared first, and if they are found to be equal only then the cascading inputs from comparison of lower bits are considered. Key Concepts Introduced ∑ One-bit binary addition without considering carry-in by the half-adder circuit. ∑ One-bit binary addition considering carry-in by the full-adder circuit. ∑ n-bit parallel binary adder. ∑ Carry look ahead circuit and carry look ahead adder. ∑ BCD addition and BCD adder circuits. ∑ Half subtractor and full subtractor for 1-bit subtraction without and with carry-in. 229 230 Digital Electronics ∑ 2’s complement subtraction by addition. ∑ Introduction to Arithmetic and Logic Unit (ALU) ICs. ∑ Single- and multi-bit comparator circuits with cascading inputs. Review Questions Pick the correct one 1. The correct expression to represent carry-out for a half-adder with P and Q as two binary inputs will be (a) Cout = P + Q (b) Cout = P ◊ Q (c) Cout = P ⊕ Q (d) none of these 2. How many times will carry be generated if two 4-bit binary numbers 0101 and 1110 are added together? (a) One (b) Two (c) Three (d) None of these 3. How many 4-bit binary adders will be necessary to construct a 10-bit parallel binary adder? (a) One (b) Two (c) Three (d) None of these 4. How many times will carry be generated and how many times will carry be propagated if 1111 is added to 1111, both being binary numbers? (a) 2, 2 (b) 3, 4 (c) 4, 3 (d) None of these 5. The carry-generation and carry-propagation functions depend on the conditions of the (a) next bit (b) previous bit (c) current bit (d) none of these 6. To modify a half-adder circuit into a half-subtractor circuit, we need an extra ____ gate. (a) NOT (b) AND (c) OR (d) none of these 7. ALU 74181 accepts 4-bit inputs and generates 4-bit outputs which are (a) active low (b) active high (c) both of these (d) none of these 8. ALU 74181 can perform (a) only arithmetic operations (b) only logical operations (c) both (a) and (b) (d) none of these 9. A 1-bit digital comparator offers only Digital Arithmetic (a) one output, namely A = B (b) two outputs, namely A < B and A > B (c) three outputs, namely A > B, A < B, and A = B (d) none of these 10. For multi-bit comparison with cascaded comparator ICs, the cascading inputs are utilized if the input condition of the present IC is found to be (a) A > B (b) A = B (c) A < B (d) none of these Do you remember? 1. What is the difference between a half adder and a full adder? 2. What is the major problem of constructing any multi-bit binary full adder joining several 1-bit full adders? 3. What is meant by carry-generation and carry-propagation? 4. What is the advantage of carry look ahead adder? 5. What is the difference between the circuits of a full adder and a full subtractor? 6. What is meant by 2’s complement? 7. In 74181 ALU, which type of output is available from the carry-out pin (Cn + 4)? 8. Name the control input signals which decide the type of operation performed by 74181. 9. What will be the problem if we replace the XNOR gate by a XOR gate in the circuit of 1-bit comparator designed by us (see Figure 6.25)? 10. What output we may expect from a 4-bit comparator IC such as 7485 if we connect all of its input pins with GND, except the Vcc, which is connected with +5 V? Have you understood? 1. Design a half-adder circuit using any one of the two universal gates. 2. Is it possible to replace three 2-input AND gates and the 3-input OR gate of the full-adder circuit (see Figure 6.3) by a 3-input AND gate? Justify your answer. 3. For a 1-bit full adder [see Figure 6.5(b)], if the carry-in signal is always low (0) and the other two inputs (P and Q) remain unchanged, then what will be the change in the waveform of carry-out? 4. Following is the truth table for a 2-bit carry look ahead adder. Verify the correctness of the table. Then at each row, mark the case of carry-generation and carry-propagation for both bits by suitable symbols. 231 232 Digital Electronics Truth table for 2-bit carry look ahead adder Input Output Output/Input Input Output An Bn Cin Sn Con An+1 0 0 0 0 0 0 Bn+1 Sn+1 Con+1 0 0 0 0 0 0 0 0 0 1 1 0 0 0 0 0 0 1 0 1 0 0 0 0 0 0 1 1 0 1 0 0 1 1 0 0 0 0 0 0 0 1 1 0 0 1 1 0 0 0 1 1 0 1 0 1 0 0 0 1 1 0 1 1 0 1 0 1 0 1 0 0 0 0 0 0 1 0 1 0 0 1 1 0 0 1 0 1 0 1 0 1 0 0 1 0 1 0 1 1 0 1 0 1 1 0 1 0 0 1 0 0 1 1 0 1 0 1 0 1 0 1 1 0 1 1 0 0 1 0 1 1 0 1 1 1 1 1 1 0 0 1 0 0 0 0 0 1 0 0 1 0 0 1 1 0 1 0 0 1 0 1 0 1 0 1 0 0 1 0 1 1 0 1 1 0 1 0 1 0 0 1 0 1 0 1 0 1 0 1 0 1 1 0 1 0 1 1 0 0 1 1 0 1 0 1 1 1 1 1 1 1 0 0 1 0 0 1 0 1 1 0 0 1 0 1 0 1 1 1 0 0 1 1 0 0 1 1 1 0 0 1 1 1 1 1 1 1 1 1 1 0 0 1 0 1 1 1 1 1 0 1 0 1 1 1 1 1 1 1 0 0 1 1 1 1 1 1 1 1 1 1 Digital Arithmetic 5. What is the difference between F = A plus B and F = A + B as expressed in Table 6.8? 6. Why is the ALU chip 74181 not capable of performing multiplication or division? 7. Is it possible to multiply (a) 5 by 2 and (b) 17 by 2 using 74181 ALU? Justify your answer. 8. If we cascade two 74181 to perform 8-bit operations, how many control signals will be available to decide its operation-type? 9. If we observe always LOW output from Cn + 4 pin of 74181 ALU for all types of addition operations, what might be the probable error in the constructed circuit? 10. Is it possible for comparator ICs (e.g., 74LS85) to perform comparison of 2’s complement numbers? Justify your answer. Solve using VHDL 1. Develop a VHDL function to implement a half adder. 2. Expand the above VHDL function to perform as a full adder. 3. Convert the VHDL function to a full subtractor. 4. Develop a VHDL function to implement a 1-bit comparator with cascading inputs. Answers: Pick the correct one 1.(b) 6.(a) 2.(b) 7.(a) 3.(c) 8.(c) 4.(d) 9.(c) 5.(c) 10.(b) 233