Turn Power-Reducing Features into Low-Power Systems

advertisement

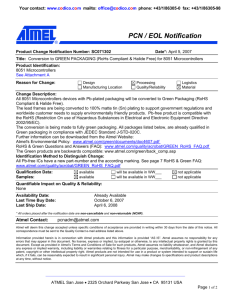

Turn Power-Reducing Features into Low-Power Systems Author: Andreas Eieland, Director of Product Marketing, Atmel System design used to be an exercise in optimizing speed. That has changed. Now systems have plenty of performance to handle many tasks, so the challenge for today’s designers is completing a task using as little energy as possible—but not necessarily making it as fast as possible. The surge in popularity of battery-powered electronics has made battery life a primary system-design consideration. In extreme cases, the desire is not to run off of a battery at all, but to harvest energy from local sources to run a system – which requires the utmost power frugality. In addition, there’s a growing family of devices like smoke detectors, door locks, and industrial sensors (4-20 mA and 10-50 mA) that can draw power through their inputs, and that power is limited. All of these trends point to the need to reduce the power requirements of electronic systems. However, the very technologies that provide the necessary performance make power reduction harder. High clock speeds, for instance, use significant dynamic current in digital CMOS ICs. Even when not active, digital circuits built on aggressive process nodes are subject to significant leakage. You’d think that the solution would be simply to select the device with the lowest power in the datasheet. But, ICs are highly integrated, with numerous modes of operation. There is no single power number. It turns out that selecting the correct device is only the start. You need the device that gives you the best power-reduction options and can achieve lower power than others, and then you must use those power-reduction options effectively. The Atmel® | SMART SAM L21 microcontroller was designed for isolated nodes that may operate far from any line power, such as in a remote Internet of Things (IoT) deployment. The SAM L21 can maintain system functionality at very low power levels. Now, let’s look at how you can leverage its options to minimize energy consumption in your systems. Reducing Power: The Big Picture The SAM L21 does best when there’s bursty activity and the processor is not continuously doing work. So, at the highest level, an effective strategy for achieving low power usage is to: • • Get computing jobs done as quickly as possible using as little energy as possible Use no (or negligible) energy when not computing As obvious as that might sound, it is subtler than it seems. While the focus is on computing, as that dominates energy consumption, computing is not the only activity. There are additional considerations when there is no computation: • Should data be retained? • Must “listeners” remain awake to detect activity? • Can some activity be accomplished without the CPU (like DMA)? • How much wake-up time can you tolerate? These issues can make low-power design more complex – and they differentiate one system from another. Reducing computing power The main determinant of power while computing is clock speed. On devices without sleep modes, the rule used to be to reduce the clock speed to the minimum necessary to accomplish a task within a time budget. But with sleep modes, it is more effective to compute quickly and then sleep for longer. With this approach, you use a higher clock rate while computing. Still, you must bear in mind that the time it takes to finish a task may not be limited by the CPU. For example, if you are consuming data that is arriving on a slow channel, that data rate may be the limiter. In that case, slowing the clock – at least until all the data has arrived – can reduce power. 2 If you slow the clock enough, the SAM L21 can provide further dynamic power savings through its built-in performance modes. The tradeoff between low- (PL0) and high-performance (PL2) modes is shown below: Parameter Max CPU clock freq. (MHz) Current* (µA/MHz) PL0 12 75 PL2 48 100 * Running Coremark benchmark, 3.3 V, LDO mode. Other examples in datasheet Minimizing memory accesses also reduces power, and that involves organizing data such that a single fetch brings as much related data as possible. Reducing idle power When the CPU isn’t needed, it can be shut down – but exactly what that means depends on the sleep modes and power islands that a given device provides. The sleep modes control which clocks are active, the state of peripheral busses, the state of peripherals, and which power domain options are available. The SAM L21 has four sleep modes: • Idle: This indicates a brief pause between computing events. Most circuits remain awake, but the CPU clock is stopped, and the AHB peripheral bus can be kept awake or made inactive. Wakeup occurs through entry into a non-masked exception handler. • Standby: This mode supports the “sleepwalking” concept. Clocks are stopped, except as needed to perform tasks, and various peripherals can be active or asleep. Power domains can be shut down, and data – both system state and RAM – can be retained or discarded. Wakeup is via peripheral interrupt. • Backup: In this mode, most of the circuit is shut down. No clocks operate, with the optional exception of the real-time counter. No state or RAM is retained. Wakeup from backup mode happens through a “backup reset” event, which can be caused by the power level returning to 3.3 V, by an external wakeup, or by the real-time counter generating an interrupt. Waking up is like restarting from scratch. • Off: In this mode, the circuit is effectively off, except that an external reset event can reawaken the circuit. Here also, waking up is like restarting from scratch. 3 Figure 1. Active, Idle, and Standby modes (including sleepwalking) can occur with either performance level, but performance levels can be changed only in Active mode. Reset from Backup (and Off) modes involves a restart, which always begins in the low-performance level. In Standby mode, you have flexibility about which power domains remain powered up or down. Much of this can happen automatically, but the advanced user can control many of these details. There are five different power domains (see Figure 2 for more details): • Backup: Contains minimal survival circuits. Active in all modes except Off, the only domain active in Backup sleep mode. • Top: Contains a few more circuits necessary for Standby, Idle, and Active modes. • PD0-2: Consists of three hierarchical functional power domains. Selectable portions of the device can be active, in retention mode, where state and RAM (back-biased) are retained, or off. 4 Main SRAM NVM PD2 CPU BACKUP TOP PD0 PD1 I/Os USB Remaining non-USB Peripherals DMA Low-Power SRAM Low-Power Peripherals Generic Clock Controller Oscillator Controller External Interrupt Controller Main Clock Controller Watchdog Timer Power Manager 32k Oscillator Controller Supply Controller Reset Controller Real-Time Counter Figure 2. Hierarchical power domains can be shut down to minimize energy consumption. Basic functions are kept in the Backup domain. At the top, computing occurs in the PD2 domain. Peripherals are split between the PD0 and PD1 domains, and DMA occurs in the PD1 domain. Sleepwalking You can use the Standby sleep mode and power domains for “sleepwalking,” which is performing tasks that don’t require the CPU while the CPU sleeps. When entering Standby mode, you specify which peripherals remain active, and power domains are powered up or down accordingly. You also specify whether the power domains retain their state when powered down. So, for example, if a peripheral initiates a DMA, it can wake the circuit up just enough to accomplish the task, and after which the circuit can either return to sleep or remain active. If the PD0 is awake and needs to initiate a DMA, it can wake up PD1 to perform the DMA, and then PD1 can go back to sleep. While this may seem complex, it doesn’t need to be. These transitions happen automatically based on settings when Standby mode is entered. Which sleep mode to enter depends on two considerations: what, if any, activity may occur while asleep and how long a wake-up time you can tolerate. The deeper the sleep, the longer it takes to wake up. Actual wake-up time depends on many variables, but the following table gives a sense of the timescales involved. Note that, from Backup and Off modes, or from Standby mode if RAM wasn’t retained, you need to add time to reload RAM. 5 Sleep mode Idle Standby Backup Off Wake-up time (µs) 1.2 2.1-76 90 2200 Benchmark Results As an alternative to so-called “bench marketing” of low-power products, all the largest semiconductor vendors—and several smaller ones that focus on low power —collaborated in a working group formed by the Embedded Microprocessor Benchmark Consortium (EEMBC). The goal was to create a generic ultra-low-power benchmark. The result of this collaboration, the new ULPBench, is rapidly gaining traction and ULPBench values have been included in recent launches from Texas Instruments and STMicroelectronics and Atmel. The ULPBench uses standardized test measurement hardware and strictly defines a benchmark code for use by vendors. The ULPBench considers both Active and Sleep mode power consumption, and can be run on 8-, 16- and 32-bit architectures. At the time of this writing, the Atmel | SMART SAM L21 product has the highest ULPBench score of any microcontroller, regardless of CPU. Conclusion Minimizing the energy your system consumes depends highly on your application requirements. Less computation means less energy consumed. Less activity during sleep states further reduces power. However, by managing the performance levels, clock frequency, sleep modes, and power domains, the SAM L21 gives you extensive control of how efficient your system will be. Effective use of these power-saving features gives your systems an edge for power-sensitive installations. Atmel Corporation 1600 Technology Drive, San Jose, CA 95110 USA T: (+1)(408) 441.0311 F: (+1)(408) 436.4200 │ www.atmel.com © 2015 Atmel Corporation. / Rev.: Atmel- 45134A-Low-Power-Systems-Eieland_Article_US_032015 ® ® Atmel, Atmel logo and combinations thereof, Enabling Unlimited Possibilities, and others are registered trademarks or trademarks of Atmel Corporation or its sub® ® sidiaries. ARM, ARM Connected logo and others are the registered trademarks or trademarks of ARM Ltd. Other terms and product names may be the trademarks of others. Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life. 6