Fundamentals of Digital Logic Design Course Outline (HCS 103)

advertisement

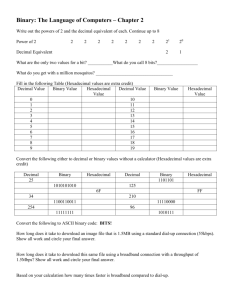

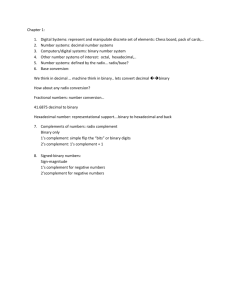

MIDLANDS STATE UNIVERSITY Department Of Computer Science and Information Systems Fundamentals of Digital Logic Design Course Outline (HCS 103) Aims and Objectives Aims: To introduce students to the fundamental principles of digital logic circuits design Objectives: At the end of this module/course successfully students should be able to: Design digital logic circuits from given specifications Trace digital signals movements in circuits Read digital logic circuits to component level Able to diagnose and repair a malfunctioning digital logic circuit Assessment Practical assignments worth 50% of Theory with worth 50% of the total final mark Continuous assessment worth 30% of the total final mark Exam mark worth 70% of the total final mark Data Representation 1) Number Bases Systems (i) Decimal 1 (ii) Binary (iii) Octal Decimal (iv) Hexadecimal (a)Conversion from Decimal to Binary/Octal/Hexadecimal using: (i) Remainder theorem/Division method (ii) Subtraction/Binary Exponential Placeholders (b) Conversion of Decimal fractions to Binary/Octal/Hexadecimal fractions using multiplication method. (c) Conversion from binary to octal decimal/hexadecimal 2) Signed Fixed Point Numbers (i) Signed magnitude (ii) One’s complement (iii) two’s complement (iv) Excess representation (v) Gray Code (vi) Converting a number in Gray Code to Binary and Vice versa (vii) Excess- 3 Gray Code 3) Range and Precision in Floating Point Numbers Representing floating point numbers in the computer (i) Binary coded Decimal (BCD) (ii) Nine’s and Ten’s Complents 4) Character Codes 2 (i) ASCII (ii) EBCDIC (iii)UNICODE 5) Logic Gates and Truth Tables NOT/OR/AND/NAND/EXOR/XNOR 6) Boolean Algebra (i) Basic Properties of Boolean Algebra (ii) Postulates (iii) Theorems (iv) DE Morgan’s Theorem 7) Karnaugh Maps (i) Two variable map (ii) Three variable map (iii) Four variable map 8) Combinational and Sequential Logic Design Reduction of combinational logic of two level expressions using: a) K- Maps b) Postulates c) Theorems 9) Examples of Logic Gates (circuits) Implementation (i) Half and Full Adders (ii) Decoders (iii) Multiplexors 3 (iv) Priority Encoders 10) Sequential Logic Circuits, Truth Tables and State Diagrams (i) SR Latch (ii) Clocked SR Latch (iii) JK and T Flip Flops (iv) JK Master Slave Configuration (v) D Flip Flop (vi) Excitation and State Tables 11) Logic Reduction (i) Effect on Speed and Performance (ii) Switching Speed (iii) Propagation delay (iv) Circuit Depth (v) Fan- in Versus Circuit depth 12) Counters and Shift Registers (i) Typical applications of Counters (ii) Synchronous and Asynchronous Counters (iii) UP – Down Counters (iv) Registers (v) Shift Registers (vi) SISO (vii) SIPO (viii) PIPO 4 (ix) PISO REFERENCES Brown S D, Fundamentals of Digital Logic Design Published by McGraw Hill (1999), India Floyd, T, L, Digital Fundamentals Published by Prentice Hall International (2000), New Jersey Cripps, Martin, Introduction to computer hardware Published by Winthrop Publishers (1989), Cambridge Morris, Mano, Computer Systems Architecture Published by Kluwer International Series (1997), California Holds worth B, Digital Logic Design 5 Published by Butterworth (1982) Roth C, H, Fundamentals of Logic Design Published by West Publishing (1995) Wakerly, F, J, Digital Design principles Published by West Publishers (1995) Gajski, D, D, Principles of Digital Design Published by Prentice Hall (1997), New Jersey Mano, M and Kune, R, K, Logic and Computer Design Fundamentals Published by Prentice Hall (1997), New Jersey Uyemura, John, Logic Circuit Design Published by Kluwer Academic Publishers (1999), California 6 7