J. Shriver, Low Level Charge Measurement, Sr. Design Document

advertisement

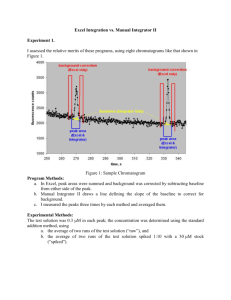

Senior Design Project Final Report: Low Level Charge Measurement Submitted by: Jason Shriver, Team 12 Technical Advisor: David Lesyna Project Advisor: Barry Todd Date: June 14, 2000 Document Number: EE175WS00-002 Revision: A Executive Summary In radiation therapy systems, it is necessary to accurately measure the position and profile of the particle beam. Specialized detectors called ionization chambers are placed in the beam line and are used to monitor the particle beam position and profile. The outputs of these detectors are in the form of very small currents that correspond to the beam position and profile. These output signals from the ionization chambers must then detected and converted to digital form to be interpreted and processed by computer systems used to operate and control the particle beam accelerator. As radiation therapy systems move from a passive method of beam delivery to an active method, finer measurements of the beam position and profile with respect to time will be needed. A microcontroller based low level charge measurement system was created to integrate the small currents coming from the ionization chambers over a programmable range of integration times. This system provides for 64 input channels with easy expandability to more input channels, an easy-to-use user interface for setting up the programmable parameters and an interface to a personal computer using an RS-232 serial connection. Key Features 64 input channels Programmable integration interval from 1 – 500 milliseconds Maximum input current of –1 microamp Sensitivity of 600 femto-coulombs RS-232 serial interface Easy-to-use user interface Page 2 of 16 Keyword List / Definitions Active Beam Delivery BUFFALO Coulomb Electron I/O Integrator Ionization Chamber LSB Microcontroller Millisecond Particle Beam Passive Beam Delivery Proton Radiation Therapy RAM ROM RS-232 VLSI Beam is modulated and scanned over area to be treated Bit User Fast Friendly Aid to Logical Operations – Monitor and debugger program resident in ROM in microcontroller Basic unit of charge, one Coulomb is equal to one Amp * Second A negatively charged particle found in the region around the nucleus of an atom Input / Output A device that performs the mathematical function of integration Specialized detector used to monitor particle beam position and profile Least Significant Bit A single chip device that contains a CPU, RAM, and I/O 10e-3 second A stream of high energy sub-atomic particles Mechanical methods are used to shape the beam and control delivered dose A positively charged particle found in the nucleus of an atom Method of cancer treatment using high energy particle beams Random Access Memory Read Only Memory A serial communication interface standard Very Large Scale Integration Page 3 of 16 Table of Contents EXECUTIVE SUMMARY ...................................................................................... 2 Key Features ................................................................................................................... 2 KEYWORD LIST / DEFINITIONS ......................................................................... 3 INTRODUCTION .................................................................................................. 6 PROBLEM STATEMENT ..................................................................................... 6 SPECIFICATION .................................................................................................. 6 General Description........................................................................................................ 6 Performance Requirements ........................................................................................... 7 Functional ....................................................................................................................... 7 Interface.......................................................................................................................... 7 Electrical / Electronic ..................................................................................................... 7 Safety.............................................................................................................................. 7 Accuracy ........................................................................................................................ 7 Diagnostics ..................................................................................................................... 8 Maintenance ................................................................................................................... 8 Options ........................................................................................................................... 8 Setup, Configuration, Calibration .................................................................................. 8 ALTERNATE SOLUTION ANALYSIS .................................................................. 8 Charge Collection vs. Charge Distribution .................................................................. 8 Digital Integration .......................................................................................................... 9 Analog Integration using Discrete Integrators .......................................................... 10 64 Channel VLSI Integrator........................................................................................ 10 Decision Matrix ............................................................................................................. 10 Decision Matrix Key ..................................................................................................... 11 SOLUTION ......................................................................................................... 11 Page 4 of 16 Overview ........................................................................................................................ 11 Key Features ................................................................................................................. 11 Block Diagram .............................................................................................................. 12 64 Channel VLSI Integrator........................................................................................ 12 Microcontroller ............................................................................................................. 13 Personal Computer ....................................................................................................... 13 Software / User Interface ............................................................................................. 13 DISCUSSION OF RESULTS .............................................................................. 14 CONCLUSIONS AND RECOMMENDATIONS .................................................. 15 REFERENCES ................................................................................................... 16 APPENDIX A – SCHEMATICS / DRAWINGS..................................................... A APPENDIX B – M68HC11EVB2 EVALUATION BOARD USER’S MANUAL .... B APPENDIX C – VLSI INTEGRATOR (TERA 03) INFORMATION ...................... C APPENDIX D – MC68HC24 PORT REPLACEMENT UNIT (PRU) INFORMATION.................................................................................................... D APPENDIX E – SOFTWARE SOURCE CODE ................................................... E APPENDIX F – SAMPLE PROGRAM RUN / TEST RESULTS ...........................F APPENDIX G – ALTERNATIVE SOLUTIONS INFORMATION .......................... G Page 5 of 16 Introduction High-energy particle beams consisting of particles such as protons or electrons are used to treat cancers in humans. In order to accurately deliver the dose to the tumor it is necessary to precisely monitor and control the particle beam position and profile as a time varying signal. This allows for accurate placement of the dose at the tumor site. Specialized detectors called ionization chambers are placed in the beam line and are used to monitor the particle beam position and profile. The outputs of these detectors are in the form of very small currents that correspond to the beam position and profile. These output signals from the ionization chambers must then be detected and converted to digital form to be interpreted and processed by computer systems used to operate and control the particle beam accelerator. Two general methods exist for delivering high energy particles to the patient in a radiation therapy systems. Each method strives to deliver the most accurate dose to the tumor while minimizing damage to surrounding tissue. These two methods are: 1. Passive – in which mechanical methods are used to shape the beam (by use of absorbers, collimators, scatters, etc.) 2. Active – in which a narrow beam is steered to aim at a small fraction of the area to be treated Problem Statement In order for radiation therapy systems to move to an active method of treatment, it is necessary to accurately monitor the particle beam position and profile as a function of time. To perform these measurements, ionization chambers with multiple strips, wires, or pixel regions are used. The outputs of these detectors are in the form of very small currents that must be detected and converted into digital form to be interpreted using computer systems. Specification General Description The low level charge measurement system consists of many independent channels capable of measuring currents in the picoamp to microamp range. This device will integrate the amount of charge detected over a configurable integration interval and then convert the result to digital format. All I/O for this Page 6 of 16 system will occur over an RS-232 serial communication link to a personal computer. Performance Requirements Functional The low level charge measurement system shall meet the following functional requirements: Support a minimum of 64 independent channels per board Accept input currents in the range of -20 picoamps to -1 microamps Integrate charge on all inputs simultaneously for configurable integration times from 1 millisecond to 500 milliseconds in 1 millisecond increments Have a sensitivity of greater than 1 pico-coulomb Include a terminal-based user interface Interface The low level charge measurement system shall communicate serially through an RS-232 link to a personal computer. Through the user interface the user shall be capable of: Setting the integration time Setting the number of integration periods Setting the range of channels to integrate over Starting an integration cycle Selecting between a user readable and a matrix output format Electrical / Electronic The low level charge measurement system shall draw power from its own dedicated power supply. Two serial ports shall be provided for communication between the low level charge measurement system and a personal computer. The first serial port shall be used to communicate through the BUFFALO debugger shell. The second serial port shall be used to communicate directly to the user interface. Safety To protect the low level charge measurement system in the event of a short circuit, all power supply input lines will be fused. Accuracy Page 7 of 16 The low level charge measurement system shall have an accuracy of 1% over the full input range from -20 picoamps to -1 microamps. The maximum allowable charge quantum (quantity of charge corresponding to one LSB) is 1 pico-coulomb. Diagnostics It is highly desirable for the board to have an onboard diagnostic feature where a calibrated current could be injected into each individual channel independently and the proper functioning of the board could be determined. Maintenance No routine maintenance will be required for this system. Options It is highly desirable for the board to support channel counts from a minimum of 64 channels per board to maximum of 256 or more channels per board. Setup, Configuration, Calibration No setup other than powering on the low level charge measurement system and downloading the S-Records file into RAM will be required. Configuration of the low level charge measurement system shall consist of setting the integration time, the number of integration periods, the range of channels to integrate over and selecting between a user readable and a matrix output format Alternate Solution Analysis Charge Collection vs. Charge Distribution To measure charge, two fundamentally different approaches can be taken: measurement by charge distribution or by charge collection. Charge measurement by the principle of charge distribution is based on the fact that V=Q/C where V is the voltage at the node (in Volts), Q is the charge deposited (in Coulombs) and C is the capacitance (in Farads). Using this method, the charge deposited on a wire can be determined by measuring the voltage of the node if the capacitance is known. One problem to this approach is the variability to stray capacitance in the cabling and the sensor itself. The second fundamental approach is that of charge collection in which the input node of the measuring device is held at virtual ground so that the sensor and cabling capacitances become unimportant. Page 8 of 16 See the following figure for an example of the two methods. Another advantage of charge collection is that because the input is at virtual ground, leakage currents can be reduced by using grounded guard rings. Due to the advantages of measurement by charge collection, this approach was applied to this project. For this project, three alternative solutions were considered. These alternatives were digital integration, discrete analog integration and a 64 channel VLSI integrator. Digital Integration In digital integration, the input current would be sampled and digitized at a high rate and several discrete values obtained during a single integration cycle would be summed to provide digital integration of the input current signal. The best possible A/D converter located was a Burr-Brown Page 9 of 16 DDC101 that has 20 bits of resolution with a maximum conversion rate of 15KHz. This device could be used in a project like this, but one A/D converter for each channel on the board would be needed. This approach was not chosen due to the lack of A/D converters with sufficient dynamic range and high enough sampling rates. Ideally, a single A/D converter, of sufficient speed, could service several channels with the use of multiplexed inputs. Analog Integration using Discrete Integrators The second approach considered was the use of discrete analog integrators. The best possible choice for a discrete analog integrator was a Burr-Brown ACF2101 dual integrator. This device has two independent integrators in a single 24 pin DIP package. This approach was not chosen due to the lower number of channels per board than could be achieved using the proposed approach and the need for substantially more support components such as A/D converters and multiplexers. 64 Channel VLSI Integrator The third and chosen approach was to use a custom 64 channel VLSI integrator. This chip consists of 64 independent current integrators that are connect to 64 16-bit counters. These 64 16-bit counters are multiplexed to an addressable tri-state digital output bus. This approach provides for a system with a high number of input channels and allows for easy scalability to greater numbers of channels. Decision Matrix Solution Method Cost per channel Scalability Complexity Availability Total Score Discrete Analog Integration 8 3 2 10 23 Digital Integration 5 2 1 10 18 64 channel VLSI Integrator 8 10 7 6 31 Page 10 of 16 Decision Matrix Key Score 0 1 2 3 4 5 6 7 8 9 10 Cost per channel >$50 per channel $45 - $50 per channel $40 - $45 per channel $35 - $40 per channel $30 - $35 per channel $25 - $30 per channel $20 - $25 per channel $15 - $20 per channel $10 - $15 per channel $5 - $10 per channel <$5 per channel Scalability < 8 channels per board 8 - 25 channels per board 26 - 50 channels per board 51 - 75 channels per board 76 - 100 channels per board 101 - 125 channels per board 126 - 150 channels per board 151 - 175 channels per board 176 - 200 channels per board 201 - 225 channels per board > 225 channels per board Complexity < 1 channel per chip 1 channel per chip 2 channels per chip 3 -4 channels per chip 5 - 8 channels per chip 9 - 16 channels per chip 17 - 32 channels per chip 33 - 64 channels per chip 65 - 128 channels per chip 129 - 256 channels per chip >256 channels per chip Availability unavailable > 10 week lead time 9 - 10 week lead time 7 - 8 week lead time 6 - 7 week lead time 5 - 6 week lead time 3 - 4 week lead time 2 -3 week lead time 1 - 2 week lead time < 1 week lead time stocked part Solution Overview A custom 64 channel VLSI integrator chip was interfaced to Motorola 68HC11 microcontroller. This system is then interfaced to a personal computer by means of a RS-232 serial communication link. On-board RAM is used to store data points that will be outputted to the personal computer serially. A 68HC24 port replacement unit (PRU) is used to regain parallel I/O lost when operating the 68HC11 microcontroller in expanded multiplexed mode. Key Features 64 input channels Programmable integration interval from 1 – 500 milliseconds Maximum input current of –1 microamp Sensitivity of 600 femto-coulombs RS-232 serial interface Easy-to-use user interface Page 11 of 16 Block Diagram COM1 PC COM2 MC2681 (DUART) PORTD (TxD/RxD) 68HC11E1 (Microcontroller) 68HC24 (PRU) PORTB PORTA PORTC PORTE Input Current Source 64 Channel Integrator (TERA03) 16K Static RAM Voltage Reference 64 Channel VLSI Integrator A custom 64 channel VLSI integrator was selected as the front end to the system. This chip consists of 64 independent current integrator channels that are each connected to a voltage comparator which generates an output pulse when a fixed amount of charge has been integrated. At this time the integrator is reset and an internal 16-bit counter is incremented. These 64 independent 16-bit counters are multiplexed together onto an addressable tri-state output bus. This tri-state bus makes scaling up the number of input channels in banks of 64 very simple. Two voltage references are utilized to set the sensitivity per count from a low of 200 femto-coulombs per count to a high of 600 femto-coulombs per count. Page 12 of 16 Microcontroller A Motorola 68HC11E1 microcontroller running in expanded multiplexed mode was chosen for this project. Operating the microcontroller in expanded multiplexed mode allows for 16K of external static ram to be addressed. A 68HC24 port replacement unit (PRU) was used to regain the parallel I/O lost when operating the microcontroller in expanded multiplexed mode. A Dual Universal Asynchronous Receiver Transmitter (DUART) was also mapped into memory space to provide a second serial communications port for the microcontroller. The asynchronous serial subsystem on the 68HC11 was used to provide the other serial communications port. The timer subsystem on the 68HC11 was used to generate the programmable integration timing along with generate the appropriate reset and data strobe signals. Personal Computer A personal computer with two serial ports is used to communicate with the low level charge measurement system. The first serial port is used to provide communication between the BUFFALO monitor and debugger shell. This BUFFALO shell is used to download S-record files into RAM and to begin program execution. The second serial port is used for communication with the user interface. Through the user interface, settings can be inputted, integration cycles can be started and data can be received. Matlab is used for data analysis and graphing. Software / User Interface Custom software residing on the 68HC11 microcontroller was created to provide a method of inputting settings, starting integration cycles and outputting data to the personal computer. A text-based menu system presents the user with the available options. All user input is checked for validity and if incorrect inputs are received the message “invalid” is displayed and the user is presented with the main menu. In order to setup the timer subsystem pre-scale factor on the 68HC11, the two low order bits of the TMSK2 register must be set within the first 64 clock cycles after reset. In order to accomplish this the following assembly code was written: REGBAS EQU $1000 // setup base for registers TMSK2 EQU $24 // setup offset for timer mask 2 register LDX #REGBAS BSET TMSK2,X $03 JMP D000 // load register base into IX register // set the two low order bits of register TMSK2 to 1 // jump to memory location D000 Page 13 of 16 This short section of code was assembled and loaded in EEPROM starting at memory location $8000. Next, the reset jump vector located at $FFFE $FFFF was modified to contain the memory location of the start of EEPROM ($8000). When a user-reset occurs the microcontroller fetches the reset vector located at locations $FFFE - $FFFF and begin executing code. After setting the TMSK2 register the code in EEPROM executes a jump to memory location $D000. The main software is located at memory location $D000 and at this time execution begins. The results of a sample run of the software can be found in Appendix F. In addition to the software running on the microcontroller, several Matlab scripts and functions were created for easy display and analysis of data coming from the microcontroller. Discussion of Results The prototype low level charge measurement system was developed using the Motorola 68HC11EVB2 evaluation board and a wire-wrapped perf-board to mount the 64 channel VLSI integrator chip. An interconnection cable was made to connect the two boards. A custom printed circuit board (PCB) would be created for a production version of the device. Guard rings were not used on the inputs of the 64 channel VLSI integrator chip for the prototype version, but would be include in a production version. Weaknesses of the current design include limited on-board memory for data point storage and the slow serial interface between the low level charge measurement system and the personal computer which limits the amount of data that can be transferred in a given amount of time. The strengths of this design include the easy-to-use user interface that can be easily changed and customized, the convenient interface to Matlab for rapid data display and analysis and the scalability of the design to support far greater numbers of channels. The reset of the VLSI integrator did not function correctly, but data can be read from the chip and displayed by the microcontroller. This problem is either due to a software error or possibly a hardware or wiring error. Leakage currents on the order of nano-amps were detected due the absence of grounded guard rings on the input channels of the 64 channel VLSI integrator chip. Page 14 of 16 Conclusions and Recommendations This system has the potential to be very valuable for low level charge measurements over many channels. This system can be used as a starting point for a more complex system using the 64 channel VLSI integrator chip. The following recommendations for future work are made: Implementation of software or hardware based input electronics saturation detection Implementation of a software or hardware based leakage current correction Implementation of software based full-scale slope calibration Implementation of input current divider or similar means of increasing maximum input currents Debugging of 64 channel VLSI integrator reset problem Increase of the serial communication speed from 9600 baud to 33600 baud Creation of custom PCB with proper input guard rings Migration of system to a higher clock rate microcontroller or microprocessor capable of addressing greater amounts of RAM and capable of faster communication rates Page 15 of 16 References Strip Ionization Chambers as 3-D Detector for Hadrontherapy – C. Brusasco, A. Cattai, R. Cirio, G. Dellacasa, M. Donetti http://www.to.infn.it/esperimenti/tera/publication.html Performances of a VLSI Wide Dynamic Range Current-to-Frequency Converter For Strip Ionization Chambers – G.C. Bonazzola, R. Cirio, M. Donetti, F. Marchetto, G. Mazza, C. Peroni, A. Zampier http://www.to.infn.it/esperimenti/tera/publication.html The Magic Cube 3D Dosimeter for Hadron Beams: A Status Report – R. Cirio, M. Donetti, F. Marchetto http://www.to.infn.it/esperimenti/tera/publication.html A VLSI Analog Pipeline Read-Out for Electrode Segmented Ionization Chambers - G.C. Bonazzola, S. Bouvier, R. Cirio, M. Donetti, M. Figus, F. Marchetto, C. Peroni, A. Zampier http://www.to.infn.it/esperimenti/tera/publication.html DDC101 20-Bit Analog-to-Digital Converter - Burr-Brown – www.burr-brown.com, March 1998 ACF2101 Low Noise, Switched Integrator - Burr-Brown – www.burr-brown.com, September 1994 M68HC11EVB2 Evaluation Board User’s Manual - Motorola – M68HC11EVB2/AD1, © 1991 HC11 – M68HC11 E Series Technical Data - Motorola – M68HC11E/D, Rev 1, © 1995 HC11 – M68HC11 Reference Manual - Motorola – M68HC11RM/AD, Rev 3, © 1991 TK68HC24 PRU – Port Replacement Unit (PRU) – Tekmos – www.tekmos.com, 8/21/99 VDEV-IO VMEbus Prototyping Board Version 2.2 – JANZ Computer AG – www.janz.com, © 1992 Page 16 of 16 Appendix A – Schematics / Drawings Page A1 Appendix B – M68HC11EVB2 Evaluation Board User’s Manual Page B1 Appendix C – VLSI Integrator (TERA 03) Information Page C1 Appendix D – MC68HC24 Port Replacement Unit (PRU) Information Page D1 Appendix E – Software Source Code Page E1 Appendix F – Sample Program Run / Test Results Page F1 Appendix G – Alternative Solutions Information Page G1