PAWAN KUMAR SINGH

advertisement

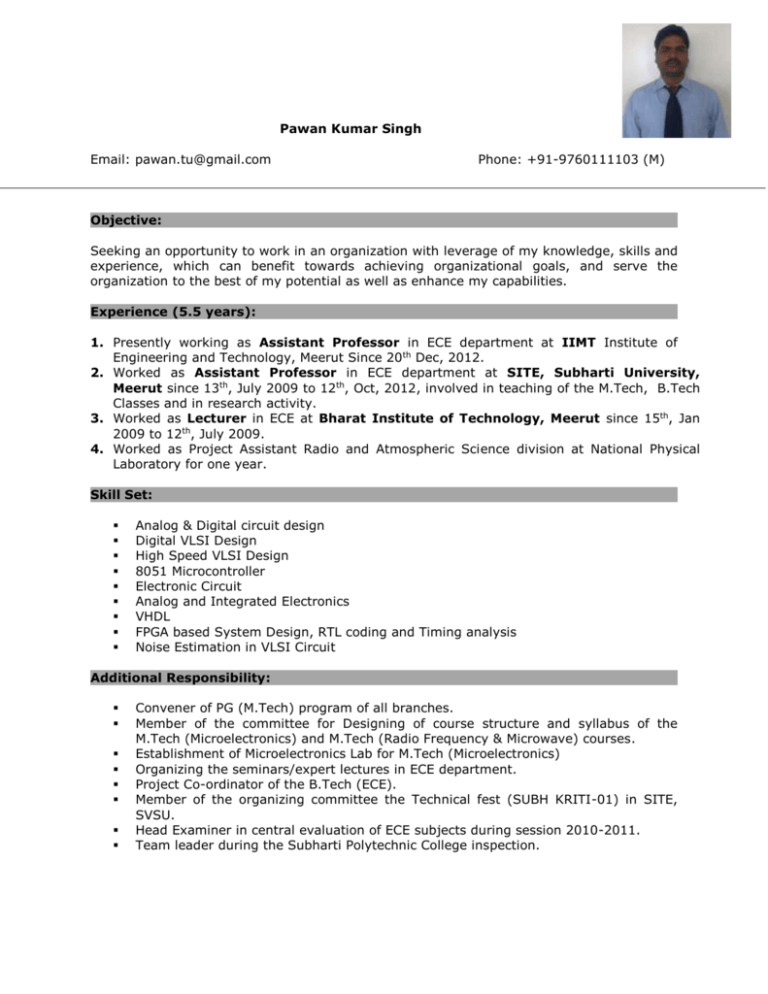

Pawan Kumar Singh Email: pawan.tu@gmail.com Phone: +91-9760111103 (M) Objective: Seeking an opportunity to work in an organization with leverage of my knowledge, skills and experience, which can benefit towards achieving organizational goals, and serve the organization to the best of my potential as well as enhance my capabilities. Experience (5.5 years): 1. Presently working as Assistant Professor in ECE department at IIMT Institute of Engineering and Technology, Meerut Since 20th Dec, 2012. 2. Worked as Assistant Professor in ECE department at SITE, Subharti University, Meerut since 13th, July 2009 to 12th, Oct, 2012, involved in teaching of the M.Tech, B.Tech Classes and in research activity. 3. Worked as Lecturer in ECE at Bharat Institute of Technology, Meerut since 15th, Jan 2009 to 12th, July 2009. 4. Worked as Project Assistant Radio and Atmospheric Science division at National Physical Laboratory for one year. Skill Set: Analog & Digital circuit design Digital VLSI Design High Speed VLSI Design 8051 Microcontroller Electronic Circuit Analog and Integrated Electronics VHDL FPGA based System Design, RTL coding and Timing analysis Noise Estimation in VLSI Circuit Additional Responsibility: Convener of PG (M.Tech) program of all branches. Member of the committee for Designing of course structure and syllabus of the M.Tech (Microelectronics) and M.Tech (Radio Frequency & Microwave) courses. Establishment of Microelectronics Lab for M.Tech (Microelectronics) Organizing the seminars/expert lectures in ECE department. Project Co-ordinator of the B.Tech (ECE). Member of the organizing committee the Technical fest (SUBH KRITI-01) in SITE, SVSU. Head Examiner in central evaluation of ECE subjects during session 2010-2011. Team leader during the Subharti Polytechnic College inspection. Master Thesis Guided: (04) Topics: High Speed Delta-Sigma Modulator without Using Op-Amp. (2010-11) FPGA Implementation of Receiver/Transmitter for OFDM System. (2010-11) Design of Monopole UWB Antenna based on MEMS Technology (2011-12) Study of Low Power Dissipation Ru/3C-SiC Schottky Barrier Diode Using Linearly Graded Doping Profile for high Voltage Application.(2011-12) Publications: International Journal 1. Pawan Kumar Singh and Sanjay Sharma, “Substrate Noise Analysis of Full Adder Circuit using Nanometer Technology for High-Ohmic Substrate” Journal of computational and theoretical nanoscience” vol 9 pp-1-5,August 2012. 2. Pawan Kumar Singh and Sanjay Sharma, “Analytical parametric modeling of Nanoscale Surrounding Gate MOSFET Based on the Poisson’s Equation" Accepted in Journal of computational and theoretical nanoscience”, vol 10, pp 1-4, 2013. 3. Pawan Kumar Singh and Sanjay Sharma, “SUBSTRATE NOISE COUPLING IN NMOS TRANSISTOR FOR RF/ANALOG CIRCUITS”, International Journal of the Physical Sciences Vol. 6(8), 4 May, 2011 page-2285-2293. 4. Pawan Kumar Singh, Shashikant Nayak, and Sanjay Sharma, “SUBSTRATE NOISE COUPLING: A STUDY FOR THE IMPACTS AND REMEDIES”, International Electronic Engineering Mathematical Society IEEMS, Volume (5), September 2010, pp. 50-58 5. Mohit Kumar, Jitender S Kuntal, Pawan Kumar Singh, Sanjay Sharma, “OPTIMIZED STRUCTURE IMPLEMENTATION OF DIVIDER FOR PREDISTORTION ALGORITHM”, International Electronic Engineering Mathematical Society IEEMS, Volume (5), September 2010, pp. 68-76 6. Pawan Kumar Singh and Sanjay Sharma “S- Parameter based Analysis of substrate coupling in NMOS Transistor for Analog/RF circuit”, IJSER, vol 3, issue 7, July, 2012. 7. Pawan Kumar Singh and Sanjay Sharma “Low Power Narrow band inductively Source degenerated LNA in presence of substrate noise” Accepted in International journal of Applied Science Engineering and Technology, Maxwell Scientific publisher, 13th September, 2012. 8. Pawan Kumar Singh and Sanjay Sharma” Substrate Coupling of RF CMOS on Lightly Doped Substrate for Nanoscale Mixed-Signal Design” accepted in journal of computational and theoretical nanoscience, April 12,2013. Conference 1. Pawan Kumar Singh, and Sanjay Sharma” "Substrate Noise Analysis in Digital Circuits using Nanoscale Technology” 2nd International Advances in Applied Physics and Materials Science Congress, 26 to 29 April 2012 in Antalya, Turkey. Communicated International Journal: 1. Pawan Kumar Singh and Sanjay Sharma, “Analysis of Substrate Coupling in Design of High Performance VLSI circuit for 0.18 µm Technology” International Journal of Electronics” March 2nd, 2013. Seminars and Training: Seminar on Placement and Routing in VLSI. Seminar on H/W-S/W co-design. Seminar on D-Calculus and D-Algorithm. Seminar on Algorithm for Floor-planning. Two week training on “Digital system design & VHDL based design” HDL Used : VHDL. EDA Tool : Xilinx Foundation Series. Description: The basic understanding of the HDL language and implementation blocks and FSM had been taught and behavioural had been done. Academic Background: Qualification M.Tech. Year of University/Board Passing Electronics and Registered Thapar University, Patiala Communication Engg. Since July, 2009 VLSI Design & CAD 2008 Thapar University, Patiala M.Sc Electronics 2005 Gorakhpur University,GKP 78.33 B.Sc Electronics 2002 Gorakhpur University,GKP 56.83 12th Science-Maths 1997 U.P. Board 56.80 10th Science 1995 U.P. Board 75.83 Ph.D. Branch Percentage/Status Reg. No.950906011 Pre submission done. 8.08 (CGPA) Key Skills: EDA Tools Mentor Graphics tool, Xilinx System edition-12.1i, Agilent ADS, HFSS. Language VHDL, C, Assembly Language (8051,8085) Embedded Development Tool Xilinx EDK, Xilinx System Generator, Keil uVision3. Methodologies Design using HDL, FPGA Implementation on (Virtex-II Pro Board, Spartan -3A/3E/3AN Logic Board). Project Summary: Project.1 Title Period Center Responsibilities Project Tools Digital Predistortion in WCDMA Power Amplifier using Embedded Processor 6 months Thapar University, Patiala Design a Digital Predistoter Tool used: Quartus, and Nios FPGA Implementation This project is designed to linearize the response of power amplifier used in WCDMA system. As we know that power amplifiers are nonlinear in nature, so in the predistortion we cascade a system which have the anti response of the power amplifier, so that system must produce linear output. Quartus-||, Nios-||, Modelsim 6.1, Matlab 7.3. Project.2 Title Development of real Time Data Acquisition System using PC Printer Port on Virtual Instrument Platform Period 6 months Center National Physical Laboratory (a CSIR Lab), New Delhi. Responsibilities Programming in ‘C’ and 8051 for the data acquisition Implementation on virtual instrument Platform (LabVIEW) Post Simulation Project The intent of this project was to develop a C language programme that is use to acquire the real time data through the printer port using the NI DAQ card. After the acquisition the data must processed for real time application. Tools C, 8051, LabVIEW 7 Expert Talks /Guest Lectures/Examiner: Recent trends in Digital VLSI Design, Department of Electronics and Communication Engg, GBIT, Meerut, UP, India, 18th February, 2011. Static Timing Analysis, Department of Electronics and Instrumentation Engg, ITM Gwalior, Gwalior, MP, India, 26th August, 2011. M.Tech Thesis Examiner in Department of Electronics and Instrumentation Engg, ITM Gwalior (2009-10). Achievements & Certificates: Mission-10X certificate on Teaching Methodologies (Five days work shop) organized by WIPRO Technology, 2010. Secured 2nd rank in department in M.Sc. Secured 1st rank in school in 10th. State scholarship holder during 9th to 12th. Workshop attended at Thapar University, Patiala, June 2012. Personal Details: Date of Birth : 15th July 1981 Sex : Male Marital status : Married Nationality : Indian Present Address : 21, Dev park colony, Baghpat Road, Meerut-250005. Permanent Address : Vill- Satabharia, Po- Saunaria, Distt- Kushinagar, UP, Pin-2743001 Languages Known : Hindi, English, Punjabi (Learning Phase) Forte : Willingness to learn. Adapt new technology in a very short period of time Belief in Teamwork. Willing to work on challenging projects. Declaration: I hereby declare that all the above-mentioned details are true to the best of my knowledge. Place: Meerut Pawan Kumar Singh