School of Computer Science

advertisement

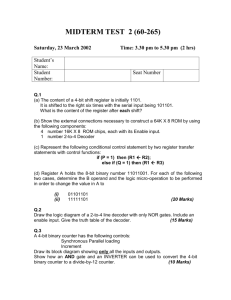

Page 1 of 9 School of Computer Science 60-265-01 Computer Architecture and Digital Design Fall 2007 Midterm Examination # 2 Wednesday, November 14, 2007 Marker Copy Duration of examination: 75 minutes 1. Answer all questions on this examination paper in the space provided. 2. This is a closed-book examination – no notes or books or electronic computing or storage devices may be used. 3. Do not copy from other students or communicate in any way. All questions will be answered only by the attending proctors. 4. All students must remain seated during the last 5 minutes of the examination. 5. The examination must be surrendered immediately when the instructor announces the end of the test period. 6. Each student must sign the examination list before leaving the classroom. Total mark obtained: ________________ Maximum mark: 36 Page 2 of 9 Question 1. [ 5 marks ] Answer all parts of this question. A. What is the radix of the integer numbers below if the solution to the quadratic equation shown is 5? [2 marks] x2 – 10 x + 31 = 0 Recall that we use positional representation, where a number is represented in an arbitrary base (or radix) using: N L d k 0 k Rk Hence, since x=5, it follows that (using decimal, or base-10 radix): 52 – (1*R+0)*5 + (3*R+1) = 25 – 5R + 3R + 1 = 26 – 2R = 0 It follows that R = 13. B. Show the value of all bits of a 12-bit register that hold the number equivalent to decimal 215 in binary. [1 mark] 215 converts to: 128 + 64 + 16 + 4 + 2 + 1 In 12-bit binary notation: C. 000011010111 Show the value of all bits of a 12-bit register that hold the number equivalent to decimal 215 in binary coded octal. [1 mark] 215 converts to: 4*49 + 2*7 + 5 In 12-bit binary coded octal notation: 000100010101 D. Show the value of all bits of a 12-bit register that hold the number equivalent to decimal 215 in binary coded decimal (BCD). [1 mark] In 12-bit binary coded decimal notation: 001000010101 Page 3 of 9 Question 2. [ 7 marks ] A sequential circuit has two D flip-flops A and B, two inputs X and Y, and one output Z. The flip-flop input equations and the circuit output are as follows: DA = Y’ A + X B DB = X Y’ + Y B Z = A A. Draw the logic diagram of the circuit. [3 marks] D-FF A Z X D-FF B Y B. Tabulate the state table (ie. fill in a state table with all required values). [4 marks] X 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 Y 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 A 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 B 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 Z = DA 0 0 1 1 0 0 0 0 0 1 1 1 0 1 0 1 DB 0 0 0 0 0 1 0 1 1 1 1 1 0 1 0 1 Page 4 of 9 Question 3. [ 10 marks ] A. Derive a combinational circuit that accepts inputs from two 4-bit registers R0 and R1, each containing a 4-bit 2’s-complement integer, and produces a single output V. The output V = 1 if and only if the result of adding R0+R1 produces an overflow (ie. a value that does not “fit” within the 4-bit representation); otherwise, V = 0. It is not necessary to represent the register flip-flops explicitly as flip-flops. Also, you may use HA (half-adder) and/or FA (full adder) MSI elements as defined in the lectures (and in Mano). [4 marks] First, it is vital to correctly define what constitutes overflow and how to recognize it. We note that adding any valid positive number to any valid negative number results in a number that is a valid 2’s complement representation – that is, such additions do not produce overflow. This leaves two cases: adding two positive numbers or adding two negative numbers. By examining such cases, it is clear that overflow situations are recognizable by an absurd change of the sign (high order) bit. For instance, in a 4-bit representation, the largest positive number is 7 (0111). Now, add 1 (0001) to this to get 7+1=8. However, 8 in binary is just 1000. In a 2s complement representation, this is the number -8, which is illogically absurd. Thus, a circuit to detect overflow only needs to check the value of the sign bit of the inputs against the sign bit of the result. Denoting the high order bits of A and B inputs as AH and BH respectively, and of the sum high order bit as SH, it follows that the overflow output V is defined by the circuit: V = AH’ BH’ SH + AH BH SH’ Page 5 of 9 B. Design a 4-bit comparator circuit that accepts two 4-bit register inputs, R0 and R1, each representing a 4-bit unsigned binary integer value, and produces three outputs: G, L and E. The value of G is 1 if R0 > R1, with L = E = 0. The value of L is 1 if R0 < R1, with G = E = 0. The value of E is 1 if R0 = R1, with G = L = 0. Note that G, L and E correspond to Greater_than, Less_than and Equal_to flag outputs and they are mutually exclusive (only one can 1 at a time, with others being 0’s). [6 marks] This was a challenging problem. Students are advised to consult the lecture slides (4a – near the end) dealing with comparators. In the following I substitute A=R0 and B=R1. A is compared with B. First stage – lowest order bits, A0 and B0. G0 = A0 B0’ L0 = A0’ B0 E0 = A0B0 + A0’B0’ A0 > B0 A0 < B0 A0 = B0 General case – k’th bits Ak and Bk. Ak 0 1 0 0 0 1 1 1 Bk 1 0 0 0 0 1 1 1 Gk-1 x x 1 0 0 1 0 0 Lk-1 x x 0 1 0 0 1 0 Ek-1 x x 0 0 1 0 0 1 Gk 0 1 1 0 0 1 0 0 Lk 1 0 0 1 0 0 1 0 Thus, it follows that: Gk = Ak Bk’ + (AkBk + Ak’Bk’)Gk-1 Lk = Ak’ Bk + (AkBk + Ak’Bk’)Lk-1 Ek = (AkBk + Ak’Bk’)Ek-1 A > B (to k’th bit) A < B (to k’th bit) A = B (to k’th bit) It is not necessary to draw the logic diagram. If you drew the diagram, then it must conform to the logic above. Ek 0 0 0 0 1 0 0 1 Page 6 of 9 Question 4. [ 7 marks ] A. Construct a 6-to-64 line decoder with four 4-to-16 with enable and one 2-to-4 line decoder. Use block diagrams. [4 marks] Number the inputs as S0, S1, up to S5. Similarly, label the outputs as D0, D1, up to D63. Next, notice that the subscripts on output D lines require 6 bits. Indeed, D0 is a 1 if and only if (S5 S4 S3 S2 S1 S0) = (000000), D15 is a 1 if and only if (S5 S4 S3 S2 S1 S0) = (001111), D31 is a 1 if and only if (S5 S4 S3 S2 S1 S0) = (011111), D47 is a 1 if and only if (S5 S4 S3 S2 S1 S0) = (101111), and D63 is a 1 if and only if (S5 S4 S3 S2 S1 S0) = (111111). There is a pattern here with the low order 4 bits ranging from (0000) to (1111) for each of the 2 high order bits ranging from (00) to (01) to (10) to (11). Thus, we use the 2-to-4 line decoder as an enabling element for each of four 4-to-16 line decoders, each of which has 16 output lines numbered 0-15 (0000 to 1111). Using block diagrams, we find: S0 S1 S2 S3 4x16 DEC E 4x16 DEC S4 S5 2x4 DEC E 0 1 2 3 E 4x16 DEC E 4x16 DEC E 0 1 15 0 1 15 0 1 15 0 1 15 D0 . . . . D15 D16 . . . . D31 D32 . . . . D47 D48 . . . . D63 Page 7 of 9 B. How many flip-flops will be complemented in a 12-bit binary counter to reach the next count after 101001101111? [1 mark] Binary counters represent unsigned binary values. Thus, adding 1 to the initial value yields the value: 101001101111 + 000000000001 101001110000 As seen above, 5 flip-flops must be complemented. C. How many 128x8 (that is, 128 addresses x 8 bits per address) memory chips are needed to provide a memory capacity of 32768x32? All chip memory units (ie. flip-flops) must be used for memory purposes only; no wastage is permitted. [2 marks] In order to construct a storage of 32 bits using 8 bit elements requires 4 elements. In order to construct an address space of 32768 = 215 from elements that provide for 128 = 27 addresses requires 215 / 27 = 28 = 256 elements. Thus, the total number of 128x8 chips needed is: 256x4 = 1024 memory chips. Page 8 of 9 Question 5. [ 3 marks ] A digital computer has a common bus system for 16 registers of 32 bits each. The bus is constructed with multiplexers. A. How many selection inputs are there in each multiplexer? [1 mark] 4 selection inputs are provided. B. What size of multiplexers are needed? [1 mark] 4 x 16 MUXes are needed. C. How many multiplexers are there in the bus? [1 mark] There must be 1 MUX for each bit, hence 32 MUXes. Page 9 of 9 Question 6. [ 4 marks ] Using a 4-bit counter with parallel load and a 4-bit adder, draw a block diagram that shows how to implement the following statements: X : R1 R1 + R2 X’ Y : R1 R1 + 1 Add R2 to R1 Increment R1 There are several ways of answering this question. The following uses a simplified approach. See explanation below the block diagram. R2 R2 X 4xAND Carry in ADD4wC Y In the diagram above I combined the 4-bit counter with parallel load and the adder to form a 4-bit adder with parallel load and carry input (ADD4wC). The input to this unit from R2 is controlled using a set of 4 AND gates (4xAND) coupled to the X input. When X=0 this input is zero through all 4 input lines, but when X=1 these inputs are the R2 bits and the Carry input is 0. When X=0 and Y=1, the R2 inputs are zero, as mentioned, but the Carry input is 1. Thus, an increment is performed. All outputs are fed back into R1, as required.