ECGR 2255 Lab Write-Ups

advertisement

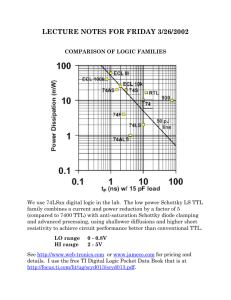

Expt. 10 T. Roppel Oct. 15, 2009 ELEC 2210 EXPERIMENT 10 Properties of TTL and CMOS Logic Families Objectives: The experiments in this laboratory exercise will investigate the properties of the TTL and CMOS logic families. The objectives of this experiment include: Measure the voltage transfer characteristic for TTL and CMOS inverters Measure the power dissipation and propagation delay for TTL and CMOS inverters Continue to develop professional lab skills and written communication skills. Introduction A detailed discussion of the voltage transfer characteristic (VTC) for a logic family can be found in Chapter 6 of the ELEC 2210 textbook, Microelectronics Circuit Design by R.C. Jaeger, 3rd Edition (Sections 6.1, 6.2 on pp. 277 – 280). Further details specific to CMOS are found in Section 7.2 (p. 355) and TTL is discussed in Section 9.11 (p. 477) Two relevant diagrams regarding the VTC are reproduced below. V– V– Figure 1. (a) Voltage Transfer Characteristic (VTC) for a logic inverter. (b) Voltage levels, logic states, and noise margins. 1 Expt. 10 T. Roppel Oct. 15, 2009 The power supplies are V+ and V– . The value of V– is most often zero (ground). The nominal (ideal or typical) output high and low voltages are VH and VL. The highest input voltage that will be recognized as a logic low is called V IL. The corresponding output is VOH. The lowest input voltage that will be recognized as a logic high is called V IH. The corresponding output is VOL. The noise margins are the safety margins that allow for noise between the output of one gate and the input to the next gate. The low-side noise margin is NML = VIL – VOL. [1] The high-side noise margin is NMH = VOH – VIH. [2] Voltages between VIL and VIH are in the undefined range. If they are applied to a logic gate, the output cannot be predicted with certainty. In addition to the VTC values, it is important to know how much power a logic gate dissipates. Average power dissipation is typically computed by averaging the power dissipation in the two logic states: PHigh = IDC(high) x VDC PAvg = (1/2)[ PHigh + PLow ] PLow = IDC(low) x VDC [3] where the subscript DC is replaced by CC for TTL and DD for CMOS. Logic Families are often compared on the basis of their Power-Delay Product (PDP). This is the average power dissipation multiplied by the average propagation delay, tP: PDP = PAvg x tP [4] The value of tP is the average of tPLH and tPHL. In this experiment, the values will be measured in the lab and compared to the relevant data sheets. Pre-Lab: Obtain the data sheet for the 7404 TTL inverter from the class web site or http://rabbit.eng.miami.edu/info/datasheets/74LS04.pdf. Obtain the data sheet for the CD4001 CMOS NOR gate from Fairchild Semiconductor: http://www.fairchildsemi.com/ds/CD%2FCD4001BC.pdf Use the data sheets to prepare a table showing the values of VOL, VIL, VIH, VOH, NML, NMH, tp, PAvg, and PDP for both devices. For all cases, use the “typical” values from the data sheets, with VCC and VDD = 5 V at 25 oC. For the TTL part, use the data for the SN7404 (on page 5). Leave space in your table to record and compare your actual values from the lab experiment. 2 Expt. 10 T. Roppel Oct. 15, 2009 Lab Exercise: (See submission instructions at the end of the writeup.) (1) Power Dissipation Obtain a 7404 TTL inverter and a CD4001 CMOS NOR gate. Select one of the inverters on the 7404 and verify that it functions properly by connecting its input to a switch and its output to an LED. Connect one of the NOR gates on the 4001 as an inverter (by grounding one of the inputs), and likewise verify that it functions properly. Make the necessary current and voltage measurements to determine the average power dissipation of each chip. Record your results in the table you prepared in the prelab. (2) Voltage Transfer Characteristic (VTC) It is not possible to perform a DC sweep with enough precision to get an accurate VTC. Therefore, we will use an AC sweep method which takes advantage of the X-Y mode on the oscilloscope. For each chip in turn, perform the following. Use the Wavetek signal generator to produce a 1 kHz triangle wave which has a minimum of 0 V and a maximum of 5 V. You will need to use the DC Offset feature, and take the output from the High (20 V) output jack. Observe this signal on Channel 1 of the oscilloscope. When it is correct, also apply this as the input to your inverter, while still running it to Channel 1 on the scope. Connect the inverter output to Channel 2 on the scope. Put the scope in X-Y mode (use the Display button / Format option). You now have a display of output voltage (vertical) vs. input voltage (horizontal) – in other words, the VTC for your logic gate. Adjust the scale factors to get a display similar to the one shown in Fig. 2 (for TTL). Identify the knee points by eye, carefully measure their coordinates with the scope, and thus obtain VOL, VIL, VIH, VOH, from which you can also compute the noise margins. Refer back to Figure 1 for definitions. Record these measurements and calculations in your prelab table. 3 Expt. 10 T. Roppel Oct. 15, 2009 Figure 2. Example VTC display for the 7404 inverter. The zero level for the output voltage (Y-axis) is the bottom line of the grid. The zero level for the input voltage (Xaxis) is the center vertical line. The scale factors are 500 mV per division in both X and Y. (The input voltage extends to negative voltage because the dc level of the input triangle wave was not properly adjusted.) (3) Power-Delay Product Put the scope back into Y-T mode (normal). Set the Wavetek signal generator to 1 MHz, square wave (0 to 5 V). Connect the Wavetek to the input of both of your inverters in turn (TTL and CMOS). Connect this signal also to Ch. 1 of the scope. Connect the inverter output to Ch. 2. Obtain a display similar to the one shown in Figure 3. Use the cursor and measurement functions to carefully measure the propagation delay (see details below). Compare with the values on the data sheet and comment. Why do you think your measured values are so much longer than those shown on the data sheet? Calculate the PDP for the TTL and CMOS chips. Record in your prelab table, and discuss. 4 Expt. 10 T. Roppel Oct. 15, 2009 Which logic family do you think is most suitable for use in low-power electronic systems? Figure 3. Propagation delay measurement for the SN7404 TTL inverter. The waveform on the bottom is the input; the waveform on the top is the output. Propagation delay measurement details: Propagation delay tP = average of tPHL and tPLH.. tPHL = time difference between 50% points* on the input and output waveforms for the high-to-low transition on the output waveform. tPLH = time difference between 50% points on the input and output waveforms for the low-to-high transition on the output waveform. *The 50% point is the point at which the voltage is halfway between the minimum and maximum voltage values. In our case, this is 2.5 V. 5