LHO 09 - Advanced VHDL

advertisement

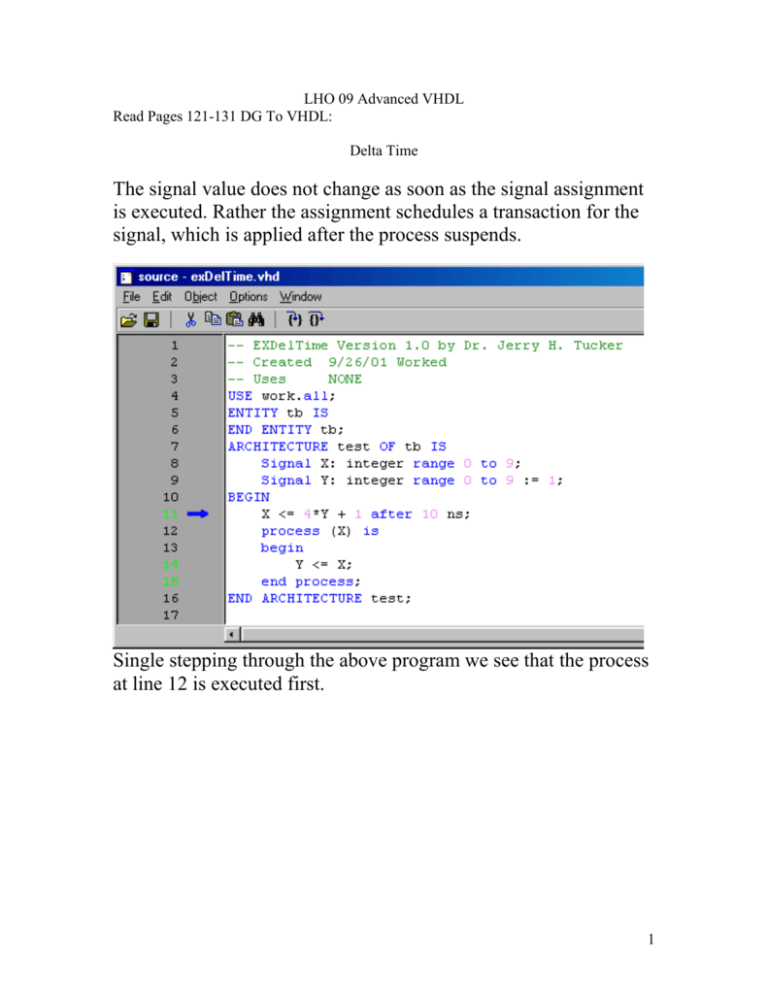

LHO 09 Advanced VHDL Read Pages 121-131 DG To VHDL: Delta Time The signal value does not change as soon as the signal assignment is executed. Rather the assignment schedules a transaction for the signal, which is applied after the process suspends. Single stepping through the above program we see that the process at line 12 is executed first. 1 The process at line 12 is executed first, but Y is not updated. Then after all delta 0 computations have been completed Y is updated at delta time 1. 2 After 10 ns, X is updated at delta time 0. This triggers the process at line 12. 3 Y is updated at delta time 1. Try using the list all signals in design and single stepping through a program. Observe the delta time changes. 4 “Signals Revisited” or “Things get even more complicated”. We have seen examples of signal assignments and examples of the delta delay. We will now discuss two other types of delay models that can be used with signal assignments. These are inertial and transport delay. See pages 124-130 of DG. Inertial Delay Model see SG 5.2.5 Inertial delay is the default and models the typical delay found in digital systems. It also enables us to specify a period of time a signal must be stable. Z <= inertial A after 10 ns; is the same as Z <= A after 10 ns; This is what we have been using, but to illustrate the capability we have with VHDL consider the following example. Example: ARCHITECTURE test OF tb IS SIGNAL Z : STD_LOGIC := '0'; SIGNAL A : STD_LOGIC := '0'; BEGIN A <= '1' after 1 ns, '0' after 2 ns, '1' after 5 ns, '0' after 10 ns, '1' after 11 ns, '0' after 20 ns, '1' after 22 ns, '0' after 30 ns, '1' after 33 ns, '0' after 50 ns; Z <= reject 2 ns inertial A after 4 ns; END test; Note that the 1 ns pulse at 1 ns is rejected, the 1 ns pulse at 10 ns is rejected, the 2 ns pulse at 20 ns is rejected, the 3 ns pulse at 30 ns is passed. The above Inertial delay model has been used to filter out unwanted spikes for the purpose of simulation. We cannot expect this to synthesize as described. Suppose we leave off the “reject 2 ns” and use “Z <= A after 4 ns;” then we get: Q: What happened? A: If a reject value is not specified, it defaults to the delay value! 5 Transport Delay Model Transport delay model situations where any input change is transported to the output. To use transport delay you must use the key word “transport”. For example: ARCHITECTURE test OF tb IS SIGNAL Z : STD_LOGIC := '0'; SIGNAL Zr : STD_LOGIC := '0'; SIGNAL Zt : STD_LOGIC := '0'; SIGNAL A : STD_LOGIC := '0'; BEGIN A <= '1' after 1 ns, '0' after 2 ns, '1' after 5 ns, '0' after 10 ns, '1' after 11 ns, '0' after 20 ns, '1' after 22 ns, '0' after 30 ns, '1' after 33 ns, '0' after 50 ns; Z <= A after 4 ns; Zr <= reject 2 ns inertial A after 4 ns; Zt <= transport A after 4 ns; END test; 6 In the above example, multiple drivers were created and resolved by the resolution function. In a process, only one driver is created for every signal assigned a value. Thus, if we have the following signal assignment with three waveform: process (…) begin … N <= 3 after 5 ns, 21 after 10 ns, 14 after 17 ns; If the process is activated at time “T”, the driver for “N” is shown below: 3 @ T + 5 ns 21 @ T + 10 ns 14 @ T + 17 ns N curr @ T Example code: ENTITY tb is END tb; ARCHITECTURE test OF tb IS SIGNAL N : INTEGER; SIGNAL C : STD_LOGIC := '0'; BEGIN C <= not C after 25 ns; process(C) begin N <= 3 after 5 ns, 21 after 10 ns, 14 after 17 ns; end process; END test; Suppose we change “C <= not C after 25 ns;” to “C <= not C after 15 ns;”. 7 What happens when we have several assignments to “N” in the same process depends on whether we are using transport or inertial delay. First, consider transport delay. In the example shown below, after the first two N <= statements are executed the driver for N looks like: 5 @ T + 5ns 20 @ T + 20ns N current@T The third assignment takes place before the assignment @ 20 ns and therefore replaces the later assignment. The final driver looks like: 5 @ T + 5ns 15 @ T + 15ns N current@T ENTITY tb is END tb; -- multiple signal assignmens in process using transport delay ARCHITECTURE test OF tb IS SIGNAL N : INTEGER; SIGNAL C : STD_LOGIC := '0'; BEGIN C <= not C after 25 ns; process(C) begin N <= transport 5 after 5 ns; N <= transport 20 after 20 ns; N <= transport 15 after 15 ns; end process; END test; If we change the order to: N <= transport 5 after 5 ns; N <= transport 15 after 15 ns; N <= transport 20 after 20 ns; We get Transport delay rule: 1. All transactions on the driver that occur at or after the delay time of the first new transaction are deleted. 2. All new transactions are added at the end of the driver. 8 For inertial delay the rule is: 1. All transactions on a driver that are scheduled to occur at or after the delay of the first new transaction are deleted (as in the transport case). 2. Add all the new transactions to the driver. 3. For all the old transactions on the driver that occur at times between the time of the first new transaction (say F) and F minus the pulse rejection limit, delete the old transactions whose value is different from the value of the first new transaction. Example: ARCHITECTURE test OF tb IS SIGNAL N : INTEGER; SIGNAL C : STD_LOGIC := '0'; BEGIN C <= not C after 25 ns; process(C) begin N <= 5 after 5 ns; N <= 15 after 15 ns; N <= 20 after 20 ns; end process; END test; Gives: Remember this: Setting up multiple assignments to a signal inside a process using transport delay works, as you would expect. Inertial delay is more complicated and may not give what you expect. If you intend to define a waveform inside a process using multiple assignments then use transport delay. 9 For inertial delay the rule is: 4. All transactions on a driver that are scheduled to occur at or after the delay of the first new transaction are deleted (as in the transport case). 5. Add all the new transactions to the driver. 6. For all the old transactions on the driver that occur at times between the time of the first new transaction (say F) and F minus the pulse rejection limit, delete the old transactions whose value is different from the value of the first new transaction. ARCHITECTURE test OF tb IS SIGNAL N : INTEGER; SIGNAL C : STD_LOGIC := '0'; BEGIN C <= not C after 25 ns; process(C) begin N <= 5 after 5 ns; N <= 20 after 20 ns; N <= 15 after 15 ns; end process; END test; ARCHITECTURE test OF tb IS SIGNAL N : INTEGER; SIGNAL C : STD_LOGIC := '0'; BEGIN C <= not C after 25 ns; process(C) begin N <= reject 2 ns inertial 5 after 5 ns; N <= reject 2 ns inertial 20 after 20 ns; N <= reject 2 ns inertial 15 after 15 ns; end process; END test; 10