Homework 2

advertisement

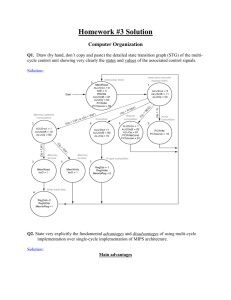

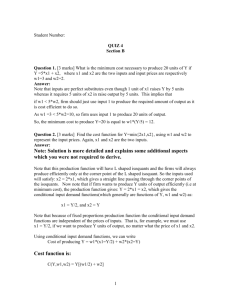

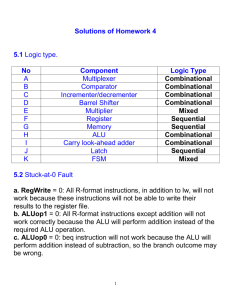

COSC 3430 Homework 2. 1. Construct the truth table for a four input odd-parity function. 2. Implement the four input odd-parity function with AND and OR gates. You can use bubbled inputs and outputs for inverting inputs to make the drawing some simpler. 3. Show that the odd parity equation derived from the sum of products can be written in the simpler way using XOR gates. 4. Assume that X consists of 3 bits, x2 x1 x0. Write four logic functions that are true if and only if ■ X contains only one 0 ■ X contains an even number of 0s ■ X when interpreted as an unsigned binary number is less than 4 ■ X when interpreted as a signed (two’s complement) number is negative 5. Assume that X consists of 3 bits, x2 x1 x0, and Y consists of 3 bits, y2 y1 y0. Write logic functions that are true if and only if ■ X < Y, where X and Y are thought of as unsigned binary numbers ■ X < Y, where X and Y are thought of as signed (two’s complement) numbers ■X=Y 6. Implement a switching network that has two data inputs (A and B), two data outputs (C and D), and a control input (S). If S equals 1, the network is in pass-through mode, and C should equal A, and D should equal B. If S equals 0, the network is in crossing mode, and C should equal B, and D should equal A. 7. The ALU supported set on less than (slt) using just the sign bit of the adder. Let’s try a set on less than operation using the values –7ten and 6ten. To make it simpler to follow the example, let’s limit the binary representations to 4 bits: 1001two and 0110two. 1001two – 0110two = 1001two + 1010two = 0011two This result would suggest that –7 > 6, which is clearly wrong. Hence, we must factor in overflow in the decision. Modify the 1-bit ALU in Figure B.5.10 on page B-33 to handle slt correctly. You can make your changes on a photocopy of this figure and possibly B.5-11 to save time. 8. A simple check for overflow during addition is to see if the CarryIn to the most significant bit is not the same as the CarryOut of the most significant bit. Prove that this check is the same as in Figure 3.3 on page 172. 9. We showed how to build a 4 bit register from D flip-flops in class. A register file consisting of 4 (or more) registers could be constructed by assembling 4 such 4 bit registers and the hardware necessary to read or write certain registers. This hardware, based on the work in class, will consist of 4 to 1 multiplexers for selecting the proper registers to read and 2 to 4 decoders for loading the data into the proper register in the file. The two inputs to the decoder will be the register to write, i.e., 00, 01, 10, 11, and the output will be four bits with all being 0 except the one corresponding to the write register which will be 1. Similarly, the inputs to the 4 to 1 multiplexer will be 4 4-bit inputs, one from each register, and the selector will be two inputs to select the proper register as for the decoder. Design the multiplexer and decoder and show how to interface them with the register file. 10. Describe the effect that a single stuck-at-0 fault would have for the signals below, in the single-cycle datapath in figure 5.17 on page 307. Which instructions, if any, would work correctly? a. b. c. d. e. f. RegWrite = 0: ALUOp0 = 0 ALUOp1 = 0: Branch = 0: MemRead = 0 MemWrite = 0: 11. Consider the following two control signals: Control signal 1 is set according to (((A OR B) XOR B) Or (A OR C)) OR (A AND B) and Control signal 2 is set according to A AND B. (a) Implement the logic for the Control Signal 1. You should directly implement the given expression (do not reorganize or optimize the expression), using NOT gates and two inputs AND, OR, and XOR gates. (b) Assume all gates have equal latencies (time from the time of data entering the gate until the output is available). What is the length of the critical path (the longest path in terms of the number of gate levels) in your circuit? 12. In problem 11 we have two control outputs based on one set of input conditions A, B, and C. a. Design a single circuit that will output the two control signals sharing as much of the circuitry of the two circuits above as is possible. b. What is the length of the critical path in this circuit in terms of gates? 13. Assume the following latencies for the logic blocks in the datapath where I-Mem and D-Mem refer to Instruction and Data memory accesses. I-Mem Add Mux ALU Regs D-Mem Sign-extend Shift-left-2 400ps 100ps 30ps 120ps 200ps 350ps 20ps 0ps a. What is the clock cycle time if the only type of instruction we need to support are ALU instructions? b. What is the clock cycle time if we must support add, beq, lw, aand sw instructions? 14. Suppose we have a floating-point unit that requires 400 ps for a floating-point add and 600 ps for a floatingpoint multiply, not including the time to get the instruction or read and write any registers, which take the same as for an integer instruction. Use the functional unit times from the example on page 315. In these exercises, we will find the performance ratio between an implementation in which the clock cycle is different for each instruction class and an implementation in which all instructions have the same clock cycle time. Assume the following: ■ All loads take the same time and comprise 30% of the instructions. ■ All stores take the same time and comprise 15% of the instructions. ■ R-format instructions comprise 25% of the mix. ■ Branches comprise 10% of the instructions, while jumps comprise 5%. ■ FP add and subract take the same time and together total 5% of the instructions. ■ FP multiply and divide take the same time and together total 10% of the instructions. Find the time for the FP operations 15. We wish to add the jr instruction to the single-cycle-datapath figure 5.17. Add any necessary datapaths and control signals to the single-cycle datatpath and show the necessary addition to figure 5.18. You can photocopy these figures to make it faster to show the additions. 16. Describe the effect that a single stuck-at-0 fault (i.e., regardless of what it should be, the signal is always 0) would have on the multiplexors in the single-cycle datapath in Figure 5.17 on page 307. Which instructions, if any, would still work? Consider each of the following faults separately: RegDst = 0, ALUSrc = 0, MemtoReg = 0, Zero = 0. 17. We wish to add the instruction addi (add immediate) to the single-cycle datapath described in this chapter. Add any necessary datapaths and control signals to the single-cycle datapath of Figure 5.17 on page 307 and show the necessary additions to Figure 5.18 on page 308. You can photocopy these figures to make it faster to show the additions. 18. We wish to add the sll instruction to the single-cycle-datapath figure 5.17. Assume the ALU control input for sll is 0011. Don’t be concerned that we did not develop the ALU to handle sll. Although shifts are usually done in a separate unit for efficiency, assume this hardware is in the ALU. Add any necessary datapaths and control signals to the single-cycle datatpath. Are any modifications or additions to figure 5.18 necessary. Show necessary changes and/or additions to figure 5.13 on page 302. You can photocopy these figures to make it faster to show the additions. 19. What effect would stuck at 0 faults have on the multiple-cycle datapath in figure 5.28. Consider the following faults: a. RegWrite = 0 b. MemRead = 0 c. MemWrite = 0 d. IRWrite = 0 e. PCWrite = 0 f. PCWriteCond = 0. 20. We want to add the lui instruction to the multicycle data path shown in figure 5.28. Show the necessary modifications to the finite state machine of figure 5.37. You may want to examine the execution steps shown on pages 325 to 329 and consider the steps necessary to execute the new instruction. How many cycles are required to implement this instruction?