Project description

advertisement

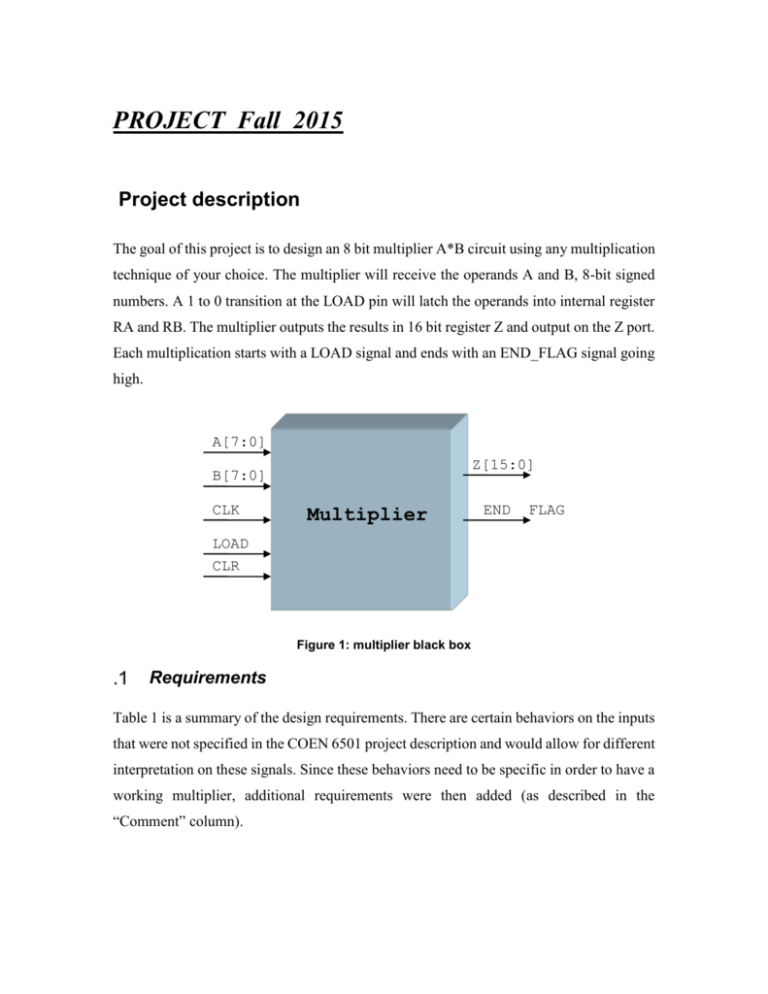

PROJECT_Fall_2015 Project description The goal of this project is to design an 8 bit multiplier A*B circuit using any multiplication technique of your choice. The multiplier will receive the operands A and B, 8-bit signed numbers. A 1 to 0 transition at the LOAD pin will latch the operands into internal register RA and RB. The multiplier outputs the results in 16 bit register Z and output on the Z port. Each multiplication starts with a LOAD signal and ends with an END_FLAG signal going high. A[7:0] Z[15:0] B[7:0] CLK Multiplier END FLAG LOAD CLR Figure 1: multiplier black box Requirements Table 1 is a summary of the design requirements. There are certain behaviors on the inputs that were not specified in the COEN 6501 project description and would allow for different interpretation on these signals. Since these behaviors need to be specific in order to have a working multiplier, additional requirements were then added (as described in the “Comment” column). Requirement Description number The design shall perform an 8bit x 8bit multiplication of R1 signed numbers. R2 The design shall be structural. The operands A and B are latched into registers RA and R3 RB when LOAD transitions from high to low. The CLEAR signal will clear all registers to ‘0’. R4 The 16-bit multiplication product shall be loaded into the R5 16-bit Z port. The multiplier performs the multiplication until R6 END_FLAG becomes high. The Test Bench, & Stimulator can be constructed using R7 “Algorithmic” modeling method. Table 1: Design Requirements Signal Specifications A0-A7: B0-B7: C0-C15 CLR: LOAD: CLK: END_FLAG Signed 8 bit Operand A Signed 8 bit Operand B Signed Output Clears selected registers Loads Operand into internal register Clock input Indicates end of multiplication Optional Expansion of the method for 16*16 bits operands. Pipelining of the design. Synthesis of the design using FPGA Multiply Accumulate Comment Delivery: Project reports due date is 2:00 P.M. Tuesday Dec. 14th, 2010 (to be handed to me in my office or to the secretary at front desk). Penalty for late delivery: 2 marks for the first day. 1 additional mark for each day after. Evaluation: a) Give full design particulars and all circuits used. b) Model your circuit using VHDL c) Simulate your design with various inputs that tests your circuit effectively d) Provide detailed timing diagram Projects will be judged based on: Delivery on time Specification Design methodology and approach and any methodology used to minimize area delay or power Effectiveness of results, testing methodology and Analysis of results Code organization Presentation and documentation .