Acs manual

advertisement

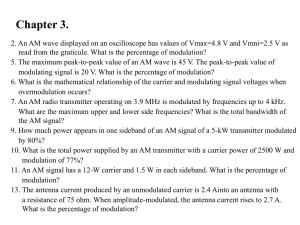

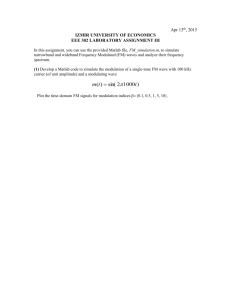

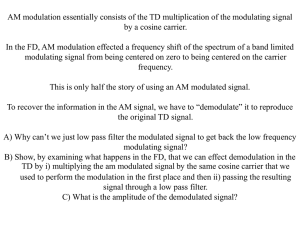

www.androiderode.com SUBJECT : 24055 ADVANCED COMMUNICATION SYSTEMS PRACTICAL (Acs manual download) 1. Trace the output waveform of a PSK modulation circuit 2. Trace the output waveform of a PSK demodulation circuit 3. Find the output of a ASK Modulation circuit. 4. Find the output of a ASK Demodulation circuit. 5. Determine the output of a FSK Transmitter 6. Determine the output of a FSK Receiver 7. Determine the output of a TDM signal. . 8. Trace the output waveform of PCM signal 9. Construct and test Analog transmitter and receiver 10. Trace the output of a Pulse width modulated Signal. 11. Construct a circuit to find the given LED and Photo diode characteristics 12. Set up a fiber optic analog link 13. Set up a fiber optic digital link 14. Measure the bending loss and propagation loss in fiber optics. 15. Test the performance of Manchester encoder and decoder 16. Measure the Numerical aperture of optical fiber 17. Construct & test a voice link using Optical fiber 18. Install & test a DTH system. 24056 - MICROCONTROLLER PRACTICAL (Mc Manual Download) 1. Write an Assembly Language Programme for Multi-byte Addition and execute the same in the 8051 Kit. 2. Write an Assembly Language Programme for Multiplication and Division of two numbers and execute the same in the 8051 3. Write an Assembly Language Programme for Arranging the given data in Ascending order and execute the same in the 8051 4. Write an Assembly Language Programme for BCD to Hex conversion and execute the same in the 8051 Kit. 5. Write an Assembly Language Programme for Hex to BCD conversion and execute the same in the 8051 Kit. 6. Write an Assembly Language Programme for ASCII to Binary and execute the same in the 8051 Kit. 7. Write an Assembly Language Programme for Parity bit generation and execute the same in the 8051 Kit. 8. Write an Assembly Language Programme for using timer / Counter and execute the same in the 8051 Kit. INTERFACE 1. Write an Assembly Language Programme for interfacing Digital I/O board and test it. 2. Write an Assembly Language Programme for interfacing Matrix keyboard and test it. 3. Write an Assembly Language Programme for interfacing seven segment LED displays and test it. 1 www.androiderode.com www.androiderode.com 4. Write an Assembly Language Programme for interfacing Traffic light control and test it. 5. Write an Assembly Language Programme for interfacing 8 bit ADC and test it. 6. Write an Assembly Language Programme for interfacing 8 bit DAC and test it. 7. Write an Assembly Language Programme for interfacing STEPPER MOTOR and test it. 8. Write an Assembly Language Programme for interfacing DC motor and test it. 9. Write an Assembly Language Programme for Sending data through port. 24057 – Very Large Scale Integration Practical 1. SIMULATION OF VHDL CODE FOR COMBINATIONAL CIRCUIT Optimize a 4 variable combinational function (SOP or POS), describe it in VHDL code and simulate it. Example: F= ( 0,5,8,9,12) in sop or pos 2. SIMULATION OF VHDL CODE FOR ARITHMETIC CIRCUITS Design and Develop the circuit for the following arithmetic function in VHDL Codes and Simulate it. Addition, Subtraction Multiplication (4 x 4 bits) 3. SIMULATION OF VHDL CODE FOR MULTIPLEXER Design and develop a 2 bit multiplexer and portmap the same for developing upto 8 bit multiplexer. 4. SIMULATION OF VHDL CODE FOR DEMULTIPLEXER Design and develop an 8 output demultiplexer. Simulate the same code in the software 5. VHDL IMPLEMENTATION OF MULTIPLEXER Describe the code for a multiplexer and implement it in FPGA kit in which switches are connected for select input and for data inputs a LED is connected to the output. 6. VHDL IMPLEMENTATION OF DEMULTIPLEXER Switches are connected for select inputs and a data input, Eight LEDs are connected to the output of the circuit. 7. VHDL IMPLEMENTATION OF 7 SEGMENT DECODER Develop Boolean expression for 4 input variables and 7 output variables. Design and develop a seven segment decoder in VHDL for 7 equations. A seven segment display is connected to the output of the circuit. Four switches are connected to the input. The 4 bit input is decoded to 7 segment equivalent. 8. VHDL IMPLEMENTATION OF 7 SEGMENT DECODER BY LUT Develop a 7 segment decoder using Look up table. Describe the seven segment decoder in VHDL using developed Look up table. A seven segment display is connected to the output of the circuit. Four switches are connected to the input. The 4 bit input is decoded into 7 segment equivalent. 9. VHDL IMPLEMENTATION OF ENCODER Design and develop HDL code for decimal (Octal) to BCD encoder. There will be10 input switches (or 8 switches) and 4 LEDs in the FPGA kit. The input given from switches and it is noted that any one of the switch is active. The binary equivalent for the corresponding input switch will be glowing in the LED as output.Page | 163 10. SIMULATION OF VHDL CODE FOR DELAY Develop a VHDL code for making a delayed output for 1second or 2 seconds by 2 www.androiderode.com www.androiderode.com assuming clock requency provided in the FPGA Kit. 11. VHDL IMPLEMENTATION FOR BLINKING A LED Develop a VHDL Code for delay and verify by simulating it. This delay output is connected to LED. Delay is adjusted such away LED blinks for every 1 or 2 seconds. 12. SIMULATE A VHDL TEST BENCH CODE FOR TESTING A GATE Develop a VHDL test bench code for testing any one of the simple gate. Simulate the test bench code in the HDL software. 13. VHDL IMPLEMENTATION FOR BLINKING A ARRAY OF LEDS Design and develop a VHDL Code for 4 bit binary up counter. Four LEDs are connected at the output of the counter. The counter should up for every one seconds. 14. VHDL IMPLEMENTATION OF A SPELLER WITH AN ARRAY OF LEDS Design and develop VHDL Code for a 5 bit Johnson ring counter 4 bit The LEDs are connected at the output of the counter. The speller should work for every one seconds. 5. VHDL IMPLEMENTATION OF 7 SEGMENT DISPLAY Design and develop a seven segment decoder in VHDL. Design and develop a 4 bit BCD counter, the output of the counter is given to seven segment decoder. A seven segment display is connected to the output of the decoder. The display shows 0,1, 2.. 9 for every one second. 24064 Embedded systems Practical 1. STUDY OF ARM PROCESSOR KIT (whatever the ARM processor kit the institution is having) Example: LPC2148 The student should able to Understand the memory mapping of the IO and peripherals List the peripherals present in the processor Explain that how to use an IO pin, related SFRs and instructions Explain that how to use timer, UART, its related SFR and instructions sets 2. SIMULATION OF ARITHMETIC OPERATION ON ARM IN ASSEMBLY Develop an assembly level code for the single precision (32 bit) arithmetic function. a. Addition, b.Subtraction and b. Multiplication (Note: simulate the program in the software) 3. SIMULATION OF ASSEMBLY LEVEL PROGRAM FOR SOFT DELAY Develop an assembly level code for the 32 bit or 64 bit delay routine. Calculate the no of clock taken for the routine and adjust the delay value for the desired. (Note: simulate the program in the software) 4. SIMPLE LED BLINKING WITH VARIABLE SPEED IN ASM Develop an assembly level program of ARM processor to blink a LED (including delay routine) in variable speed in the trainer kit. Upon change in the delay program the speed should vary. No need to change the speed dynamically. (Note: Student should study the list of special function registers associated for accessing the IO pin. Manual containing List of IO registers (SFR for IO) can be given to the students for the final exam) 5. REALIZATION OF INPUT AND OUTPUT PORT IN ASM Develop an assembly level program of ARM processor to read a port in which switches are connected in the trainer kit. Send back the receive input to output in which LEDs are connected in the trainer kit Note: Student should study the list of special function 3 www.androiderode.com www.androiderode.com registers associated for accessing Port the read and write. Manual containing List of IO registers (SFR for IO) can be given to the students for the board exam) 6. SIMPLE LED BLINKING WITH VARIABLE SPEED IN C Develop a C program for ARM processor to blink a LED (including delay routine) in variable speed. Upon change in the input switch the speed should vary. (Note: The C code should be in while loop) 7. SEVEN SEGMENT LED DISPLAY INTERFACE IN C Develop a C program for ARM processor to interface a seven segment LEDdisplay. The display should count up for every one second. 8. SEVEN SEGMENT LED DISPLAY INTERFACE IN C Develop a C program for ARM processor to interface a seven segment LED display. The display should count up for every one second. The delay can be used from experiment 3 9. REALIZING TIMER PERIPHERAL IN ARM BY POLLING METHOD Develop a C program for ARM processor to run a timer peripheral in ARM. The timer flag can be pooled for timer end. As timer ends reset the timer and update new value to the LED display. 10. REALIZING TIMER PERIPHERAL IN ARM BY INTERRUPT DRIVEN METHOD Develop a C program for ARM processor to run a timer peripheral in ARM. The timer flag can be pooled for timer end. As timer ends reset the timer and update new value to the LED display.Page | 203 11. SERIAL TRANSMISSION AND RECEPTION OF A CHARACTER IN C BY POLLING METHOD Write a C Programs for receiving a character from other device (Computer) and send the next character of the received one to the device back. Note: Student should understand the SFRs used for serial communication. Manual containing list of SFRs for the UART can be given to the students for their final examination 12. SERIAL TRANSMISSION AND RECEPTION OF A CHARACTER IN C BY INTERRUPT METHOD Write a C Programs for receiving a character from other device (Computer) and send the next character of the received one to the device back. 13. DISPLAYING ALPHANUMERIC CHARACTERS IN 2X16 LINE LCD MODULE Write a C Programs for displaying a number and an alphabet in the LCD module by just calling the built in LCD function. The display should come in the desired line and column. (Built in function for the LCD can be given in the manual) 14. CONVERTING HEXADECIMAL TO DECIMAL AND TO DISPLAY IN LCD Write a C Programs for converting the given 8 bit hexadecimal into decimal and there by converting into ASCII which is to be displayed in the LCD module. (Built in function for the LCD can be given in the manual) 15. ACCESSING INTERNAL ADC OF THE ARM PROCESSOR AND TO DISPLAY IN LCD Write a C Programs for reading an ADC, convert into decimal and to display it The ADC input is connected to any analog sensor. 24035 ELECTRICAL CIRCUITS & INSTRUMENTATION PRACTICAL 4 www.androiderode.com www.androiderode.com 1. All students must have his own soldering iron and multimeter 2. At least 10 experiments should be constructed using breadboard / soldering 3. Different component value should be given for EACH batch of students. 1. Construct a circuit to verify ohm’s law 2. Construct a circuit to verify kirchoff’s voltage and current law 3. Construct a circuit to verify super position theorem 4. Construct a circuit to verify Thevenin’s Theorem 5. Construct a circuit to verify Norton’s Theorem 6. Construct a circuit to verify maximum power transfer Theorem 7. Construct and test the performance of series resonant circuit and parallel resonant circuit 8. Calibrate the given ammeter and voltmeter 9. Extend the range of given voltmeter and ammeter 10. Construct and test the performance of Wheatstone bridge 11. Measure the amplitude and frequency of signals using dual trace CRO 12. Measure the frequency and phase angle using CRO by Lissajous figure 13. Measure voltage and current using CRO 14. Test the performance of LVDT 15. Measure strain using strain gauge. 16. Determine the characteristics of a thermistor 7. Test the performance of a load cell 18. Construct and test the performance of a photo electrode Integrated circuit lab. 1. Verification of truth table of OR, AND, NOT, NOR, NAND, EX-OR gates. 2. Realization of basic gates using NAND & NOR gates. 3. Realization of logic circuit for a given Boolean expression. 4. Half adder, Full adder using IC’s. 5. Half subtractor, full subtractor using IC’s. 6. Construction and verification of truth table for Decoder/Encoder. 7. Multiplexer/De-multiplexer using multiplexer IC’s. 8. Parity generator and checker using parity checker/ generator IC’s. 9. Construction and verification of truth table for RS, D, T, JK, flip-flop. 10. 4- bit ripple counter using FF 11. Construct a Single digit Decade Counter with 7 segment display. 12. Construct and test shift registers in SIPO mode using IC 74164. 13. Inverting Amplifier and Non inverting Amplifier with AC signal using OPAMP. 14. Integrator and Differentiator using Opamp 15. Summing amplifier & Differential amplifier using Opamp. 16. Astable multivibrator using IC 555. 17. Construction of simple power supply using IC 78XX. 18. DAC using R-2R network. 5 www.androiderode.com www.androiderode.com 24045 INDUSTRIAL ELECTRONICS & COMMUNICATION ENGINEERING PRACTICAL INDUSTRIAL ELECTRONICS PRACITCAL 1. Phase control characteristics of SCR 2. Construct and test commutation circuits of SCR. 3. Construct a Lamp dimmer using TRIAC (in Bread Board Only) 4. Construct and test a MOSFET based PWM chopper circuit 5. Construct and test an IC based buck converter using PWM 6. Write and implement a simple ladder logic program using digital inputs and outputs for PLC 7. Write and implement a simple ladder logic program for interfacing a lift control with PLC. 8. Write and implement a simple ladder logic program for interfacing a conveyer control with PLC 9. Write and implement a simple ladder logic program using timer and counter with branching and subroutines with PLC. COMMUNICATION ENGINEERING PRACTICAL 1. Construct & test symmetrical T & Pi attenuators 2. Construct and test constant k passive low pass filter & high pass filter 3. Construct an AM modulator and Detector circuit and trace the output waveform 4. Construct a FM modulator circuit and trace the output waveform 5. Construct and test PAM generation circuit and detection circuit. 6. Construct and test PWM generation circuit and detection circuit 7. Construct and test PPM generation circuit and detection circuit 8. Construct and test PCM transmitter and receiver circuit Construct and test a three way crossover network. 24066 SIMULATION PRACTICAL All experiments should be designed and verified through SPICE simulation tool (like PSPICE /Multisim/ Lab VIEW/ OrCAD/ TINA) 1. Study of simulation software features using simple circuits 2. Rectifier Circuits (Half wave, full wave and bridge rectifiers with filters) 3. Power supply design with regulators 4. Waveform generators using transistors (Astable multivibrators) 5. Waveform generators using transistors (mono stable multivibrators) 6. Clippers and Clampers 7. Op-amp applications – I (any three circuits) (Inverting and non-inverting amplifiers, voltage follower, integrator, Differentiator, summing amplifier, difference amplifier) 8. Op-amp applications – II (any three circuits) (Hartley and phase shift oscillators, sine, square and triangular waveform generators, precision rectifiers ) 9. Instrumentation amplifiers 10. AM Modulation and Demodulation 11. FM Modulation and Demodulation 6 www.androiderode.com www.androiderode.com 12. ASK Modulation and Demodulation 13. FSK Modulation and Demodulation 14. PSK Modulation and Demodulation 15. Single side PCB layout design using CAD tool Lab syllabus 1. Introduction of Microcontroller Kit 2. Addition, Subtraction 3. Multi-byte addition 4. Multiplication of two numbers 5. Finding the maximum value in an array 6. Arranging the given data in Ascending order 7. BCD to Hex conversion 8. Hex to BCD conversion 9. Hex to ASCII 10. ASCII to Binary 11. Square Root of an given data 12. Least Common Multiple 13. Greatest Common Divisor 14. Parity bit generation 15. Program using I/Os in port 1 16. Counter using timer 17. Program using interrupt INTERFACING WITH APPLICATION BOARDS Minimum Six Experiments to be conducted Digital I/O 1. Matrix keyboard 2. Seven segment displays 3. LCD Displays 4. Traffic light 5. 8 bit ADC and 8 bit DAC 6. STEPPER MOTOR CONTROL 7. DC motor control 8. Lift control 9. Sending data through serial port between controller kits 10. Printer Interfacing with Microcontroller kit 7 www.androiderode.com www.androiderode.com EQUIPMENT REQUIRED Sno Name of the Equipments Range Required 1 Microcontroller Kit 15 2 8085 Microprocessor Kit 2 3 Stepper motor Interface kit 2 4 DC motor Interface kit 4 5 Traffic light control kit 2 6 Key board interface 2 7 ADC and DAC 2 S.NO ACS LAB MANUAL 14055-ADVANCE COMMUNICATION SYSTEM, LIST OF EXPERIMENT DATE NAME OF EXPERIMENT PAGE NO 1 Transistor video amplifier 2 Sync separator 3 Sample and Hold 4 PSK modulation 5 PSK demodulation 6 Fiber optic analog link 7 Fiber optic digital link 8 Bending loss and propagation loss in fiber 9 TDM of signals 10 Analog transmitter and receiver 11 FSK transmitter and receiver 12 ASK modulation 13 PWM modulation 14 Deflection sensitivity of CRT 15 Sound section fault finding 16 Video section fault finding 17 Picture tube deflection section 18 Testing of Yagi antenna 8 www.androiderode.com www.androiderode.com 1. TRANSISTOR VIDEO AMPLIFIER Aim: To construct and test the video amplifier Apparatus required: S no Equipments Range QTY 1 TV demonstrator 1 2 Video amplifier board 1 3 CRO 1 4 Pattern generator 1 5 Connecting wires 10 Theory:-High frequency response video amplifier. The used load resistance RC makes the response fault over a load wide range of middle frequency. RC coupled amplifier is used for amplifying and with minimum frequency and phase distortion and blanking is increased. The gain of video amplifier is down at high frequency because of shunting capacitance. Shunt peaking:-The peaking coil responsibly with CE to boost the gain for high frequency. Series peaking:-The wires peaking circuit more gains them shunt peaking because there is less shunt capacitance across RL while LC provides a resonant rise of voltage across them. Combination peaking:-It has more gain compared to shunt and series peaking for the same frequency response. TL has more than shunt peaking. Low frequency response of the video amplifier:-At low frequency, the reactance of the coupling capacitor CC increases and affects the low frequency response of video amplifier. Effects low frequency compensation:-The low frequency response can be compensated by the decoupling filter RF- CC in Bf supply line. It increases the gain and reduce phase distortion for very low frequency. Effect of loss of high video frequency:-The picture does not appear sharp and clear small details of picture information such as individual falls in a region and details of edge are not reproduced. Effect of loss low voltage frequency:-The video frequency from looking down to 30 HZ represent the main parts of picture information such as background shading lettering and other large areas.Because the loss of low video frequency, the whole picture becomes wear with poor contrast. Frequency distortion:-The response of the uncompensated video amp is down for high video frequency of 1KHZ and above. Hence high frequency compensation in necessary. The response of the video amplifier over the middle range of frequency is normally flat and requires no communication 9 www.androiderode.com www.androiderode.com Phase distortion:-The effect of phase distortion in time delay aspect time delay distortion have the effect of displacing picture information on the screen. The result is linear in the picture. Beam current limiting:-Excessive beam current may overload the EHT supply and also damage the value screen. This beam current can be limiting by means of a diode capacitor coupling between the video o/p and the picture tube cathode and RL in the picture tube. Result::-Thus the transistor video amplifier is constructed and tested successfully. 2. SYNC SEPARATOR Aim : to construct and test a sync separator using transistor. Apparatus required: S no Equipments Range Quantity 1 Power supply 0 -30 V 1 2 Signal generator - 1 3 Transistor BC kit 2 4 Resistor 2K,100K, 1K, 47K, 67K, 33K 1 5 Capacitor 47f, 0.01f 1 Procedure: In sync separator circuit which separates the horizontal and vertical sync pulses from the composite video signals. This is done by using low pas filter integrator and high passes filter differentiator.Time constant of R2C2 is 0.5s which is very low compared to sync duration of 5s. as the capacitor charges exponentially at the rate determined by R2, C2, the O/P voltage falls exponentially to zero level. The O/P in the form of spikes which is given to the AFC system for connecting the horizontal oscillator frequency.Separation of VSYNC pulse:The time constant of R1, C! integrator is 100s. the separator vertical sync pulse consist to five individual pulses each of 27s. When integrator allows Vsync, signals ‘C’ charges to 27 % of applied voltage and C1 discharges for 100s. the above process is repeated and hence the voltage across C1 builds upto maximum amplitude at the end V-sync pulses. The resulting O/P triangular pulses are given to the vertical oscillator for triggering. Result:Thus the construct and test a sync separator using transistor is verified. 3. SAMPLE AND HOLD AMPLIFIER Apparatus required: sample and hold amplifier kit 1 CRO 1 Patch chords 5 Procedure: Sample and is circuit hold amplifier freeze analog voltage instantly. During this process the HOLD command is issued and analog voltage is available for and extended period. If the input voltage to be digitized is varying a sample and hold amplifier chip is 10 www.androiderode.com www.androiderode.com mandatory ADCs with more precision cannot give their accuracy without a sample and hold amplifier chip.The purpose of this circuit is to hold the analogue value steady for a short time while the converter or other following system performers some operation that takes a little time. A SHA chip presents very high input impedance, and its bandwidth is considerable. When the control is changed to hold below 1.4V, the sampled voltage is held on a hold capacitor and the output voltage is frozen at that point. There is a settling time after the HOLD command is issued, until the output is within 1 mV of its steady value. After the HOLD command is issued, the aperture time is the time after the internal nodes to settle, and the output to be within, say 0.1 % of its final value, when a 10V step is made at the input. The acquisition time depends on the size of the hold capacitor. Times from the HOLD command issuance are measured from the 1.4V point of the control waveform. Sample and hold amplifiers are used in signal processing, analog to digital conversions, sensors, and imaging. Sample and hold amplifier chips are key building blocks for many discrete time signal processing applications. A simplified sample and hold circuit diagram.Al is an analog input, AO – an analog output, C- a control signal. Sample and hold circuits are often used when multiple need to be measured at the same time. Each value is sampled and held, using a common sample clock. The values can then be read at leisure. In order that the input voltage is held constant for all practical purposes, it is essential that the capacitor has very low leakage, and that it is not loaded to an significant degree which calls for a very high input impedance. The purpose Of the sample and hold circuitry is to take a snapshot of the sensor signal and hold the value. The ADC must have a stable signal in order to accurately perform a conversion. An equivalent circuit for the sample and hold is shown if figure. The switch connects the capacitor to the signal conditioning circuit once very sample period. The capacitor then holds the voltage value measured until a new sample is acquired. Many times, the sample and hold circuitry is incorporated into the same integrated circuit package. Problems with a sample and hold Finite aperture time: the sample and hold takes a period of time to capture a sample of the sensor signal. This is called the aperture time. Since the signal will vary during this time, the sampled signal can be slightly off.Signal feed through: when the sample and hold is not connected to the signal, the value being held should remain constant. Unfortunately, some signal does bleed through the switch to the capacitor, causing the voltage being held to change slightly.Signal Droop: the voltage being held on the capacitor starts to slowly decrease over time if the signal is not sampled often enough. Solution:-The main solution to these problems is to have a small aperture time relative to the sampling period. This means that if the designer uses a high sampling rate, the aperture time of the sample and hold must be quite small. Fast acquisition to 0.01 % 70ns (max) Low offset error +_ mV (Max)+_ 10mV (Max) Low pedestal error +_ 10mV (Max) Low Droop Rate (Max) Wide unity gain bandwidth 40MHZ 11 www.androiderode.com www.androiderode.com Low power Dissipation 220mW (Max) Total harmonic distortion (Hold Mode) – 72dBc Fully differential inputs., On chip hold capacitor. 4. PSK MODULATION Aim : to study the principles of phase shift keying modulation and Demodulation Apparatus Required: 1. PSK Kit. 2. Power supply 3. Patch card. Theory of the experiment. PSK modulation In the PSK modulation or phase shift keying for all one to zero transistors of the modulation data, the modulated O/P switches between the inphase and outphase. Components of the modulation frequency the frequency and phase components choosen for PSK modulating as follows. 1. 0.5 Mhz sine wave carriers (0) for refreshing carrier. 2. 1 Mhz sine wave carrier (1) for refreshing carrier. PSK modulator also utilizes a 7 to 1 modulator for switching from inphase out of phase components for all 1 to 0. Transition occurring in the transmitted data stream. The figure shows the logic implemented. Experimental procedure: Maintain the setup as for the other keying experimental connect SIN2 to I/P of the modulator. The amplitude of SIN can be adjusted by means of potentiometer P2. Connect SI2to the I/P of the modulator. The amplitude of the sine wave can be adjusted by means of potentiometer P3. Connect the oscilloscope to the control I/P of the modulator and the modulated I/P. Observations: Observe the PSK modulated O/P with respect to the control I/P observe the phase shifts in the frequency during each transients in the data. PSK modulation:-The PSK modulation works on the principle of square law which is explained below principles PSK modulation wave can be represented mathematically as follows. Observe the M(t) as a frequency component w and negative sign is eliminated.Now the inphase reference carrier can be recover by dividing the frequency of the squared modulated carrier by 2.Once the carrier is recovered, the data can be detected by comparing the phase of the RXD modulated carrier with the phase of the reference carrier. The logic for the above is built around flip flops where PLL is used for squaring the modulated carrier which is illustrated below. A phase detector works on the principle of squaring loops. The PLL recovers the carrier form the frequency O/P of the phase splitter, at the frequency of recovered carrier is twice that of the TXD carrier. So a divide by 2 connector is used to divide the frequency of the PLL output by 2. Thus the receiving the reference carrier. They delay data and the reference carrier by recovering data. 12 www.androiderode.com www.androiderode.com Observation:- Observe the PSK modulated O/P and the modulating data using 2 channels of the Osillascope. Observe the incoming modulated carrier. Observe the contracted reference carrier. With reference to the inphase modulating carrier. Also observe the recovered data with respect to modulating data. Inference: It is observed that the successful operation of the PSK is fully dependent on the phase component of the transmitted modulated carrier. If the phase reversal of the modulated carrier. If the phase reversal of modulated carrier along with the rising and falling edges of the data are not proper them. The efficient detection of the data from PSK modulated carrier becomes impossible. Result:Thus the principles of the PSK modulation and De-modulation are suited. 5. PSK DEMODULATION Aim : to study the principles of phase shift keying modulation and demodulation Apparatus Required : 1. PSK kit 2. Power supply 3. Patch card THEORY OF THE EXPERIMENT PSK modulation:-In the PSK modulation or phase shift keying for all one to zero transistors of the modulating data, the modulated O/P switches between the inphase and outphase. Components of the modulating frequency, the frequency and phase components choosen for PSK modulation as follows. 1. 0.5 Mhz sine wave carriers (0) for refreshing carrier. 2. 1 Mhz sine wave carrier (1) for refreshing carrier. PSK modulator also utilizes a 7 to 1 multiplexer for switching from inphase to out of phase components for all 1 to 0. Transition occurring in the transmitted data stream. The figure shows the logic implemented. Experimental procedure:- Maintain the setup as for the other keying experiments connect SIN2 to I/P of the modulator. The amplitude of SIN2 can be adjusted by means of potentiometer P2. Connect SIN2 to the I/P of the modulator. The amplitude of the sine wave can be adjusted by means of potentiometer P3. Connect oscilloscope to the control I/P of the modulator and the modulated I/P. Observations:- Observe the PSK modulated O/P with respect to the control I/P observe the phase shifts in the frequency during each transient in the data. PSK modulation:- The PSK modulation works on the principle of square law which is explained below principles PSK modulation wave can be represented mathematically as follows. On squaring the modulated carrier, the negative side gets eliminated and the frequency components gets multiplied by 2. Observe the M(t) as a frequency component w and negative sign is eliminated. Now the inphase references carrier can be recover by dividing the frequency of the squared modulated carrier be2. Once the carrier is recovered, the data can be detected by comparing the phase of the RXD modulated carrier with the phase of the reference carrier. The logic for the above is 13 www.androiderode.com www.androiderode.com built around flipflops where PLL is used for squaring the modulated carrier which is illustrated below. A phase detector works on the principle of squaring loops. The PLL recovers the carrier from the frequency O/P of the phase splitter, at the frequency of recovered carrier is twice that of the TXD carrier, so a divide by 2 connector is used to divide the frequency of the PLL output by 2, thus the receiving the reference carrier. The delay data and the reference carrier by recovering data. Observations: Observe the PSK modulated O/P and the modulating data using 2 channels of the oscilloscope. Observe the incoming modulated carrier. Observe the contracted reference carrier. With reference to the inphase modulating carrier. Also observe the recovered data with respect to modulating data. Inference: It is observed that the successful operation of the PSK is fully dependent on the phase component of the transmitted modulated carrier. If the phase reversal of the modulated carrier. If the phase reversal of modulated carrier along with the rising and falling edges of the data are not proper them. The efficient detection of the data from PSK modulated carrier becomes impossible. Result Thus the principles of the PSK modulation and De – modulation are studied. 6. FIBER OPTIC ANALOG LINK AIM: to construct and test the fiber optic analog link. Apparatus Required: 1. OFT Kit 2. 2 channel, 20 Mhz oscilloscope 3. Function generator TheoryThis experiment is designed to familiarize the user with OFT. An analog fiber optic link is to be setup in this experiment. The preparation of fiber optic for coupling light into it and the coupling of fiber to the LED and detector are described in Appendix A. the LED used in 350nm LED. The fiber is a multimode fiber with a cone diameter of 1000m. the detector is a simple PIN detector. The LED optical power O/P is directly proportional to the current driving the LED. Similarly for the PIN diode. The current is proportional to the amount of light falling on the diode are non – linear devices. The current in the pin diode is directly proportional to driving current of the LED. Procedure: The inner face used to experiment are summarized. The 1m and m optical fiber provided with OFT are to be used. 1. Set the switch 8 WB to the analog position switch the power ON. 2. Feed a 1v P.P( Peak to Peak) sinusoidal signal at 1 KHZ. From a function generator. 3. Connect the BNC- BNC 1/03 to the analog from the BNC socket I/03. 4. Connect the signal post I/03 using the following procedure, P11 using patch card. 5. With this the signal from the function generator is fed through to the analog in signal post P11 from the I/03 BNC sockets. 6. Connect the end of the 1m fiber to the LED source. LED1 in the optical Txt Block. 7. Observe the light O/D and the other end of the fiber. 14 www.androiderode.com www.androiderode.com Result Thus the fiber optic analog link is constructed and tested. 7. FIBER OPTIC DIGITAL LINK Aim:To construct and test the fiber optic digital link. Apparatus Required: OFT kit 1. Two channel, 20Mhz, Oscillator 2. Function generator (1 Mhz – 10 Mhz) TheoryThe Oft can be used to setup two fiber optic links, one at a wave length of 650 nm and the other at 850nm LED in the optical Txr block is an 850nm LED. PDI in the optical Rx1 block is a PIN detector which gives a current proportional to the optical power falling on the detector. The received signal is amplified gain control plays a crucial role in the conversion. PD2 in the optical Rx2 block in another receiver block which directly gives out a F+1 signal. Both the pin can receive 850nm as well as 850nm signal. Procedure: The interfaces used in the experiment one summarized in table. 1. Set the switch SW8 to the digital mode. 2. Connect 1m optical fiber between LED1 and PIN diode PDI. Remove the shorting plugs of the coded data shorting links s6 in the matches her coder block and 826 of clock recovery block. 3. Feed a TTL signal of about 20 Khz from the function generator to post B of 86 use the BNC 1/05 for feeding the observing signals as described in experiment 1. Observe the received analog signal at the amplifier post P31 on channel 1 of the oscilloscope. Note that the signal at P#! gets cut off above 3.5V. increase and decrease the gain and obseve the effect. 4. Observe the gain and received signal at port A of S26 on channel of the oscilloscope which still observing the signal at P31 on channel 1. Note that the signal at gain till the signal at P31 is less than 0.5V. note that signal at the P31 is now becomes all high this is because the B31 signals is fed to the comparator-com-inverter to give signal at S26. 5. Set the gain such that the signal at P31 is about 2V. observe the input signal from the function generator on channel 1 & the received TTL signal at port A of S26 on channel2 vary the frequency of the I/P signal and observe the O/P response. 6. Repeat the steps 4,5,& 6 with 3m fiber. Result Thus the fiber optic digital link is constructed and tested. 8. LOSSES IN OPTICAL FIBERS AIM: the aim of the experiment is study various types of losses that occur in optical fibers and measures the loss in dB of two optical fiber patch cards. Apparatus Required: 1. OFT kit 2. Power supply 15 www.androiderode.com www.androiderode.com 3. Cables TheoryAttenuation in an optical fiber is a result of a number of effects. This aspect is well covered in the refined to we will confine our study to attenuation in a fiber due to macro bending and estimate the losses in two different patch cards.The optical power of a distance h in an optical fiber is given P2 = __where _ is the launched power and ~ is the attenuation co- efficient in decibels co – efficient value for the fiber under consideration here is 0.3 dB meter a wave length of 660mm.One symbol and popular way to attenuate optical power at fiber functions is to create a known airgap of at junction.All the light existing from the transmitting side is not coupled to the receiving fiber resulting is attenuation. Procedure Mark one face of the hexogens offset nob with pen connect one end of the 1m fo cable to the LED of TNS 20A. keeping the connector with making on the hexagonal nob free. 1. Next connects the free end of cable 1 to the line adapter by rotating it connect the free end of the inline adapter lightly but without forces. 2. Set the power meter to read a convenient value say 20dB. 3. Next loss the lock nob with the making by one turn. Pull the cables gently to create an airgrap of 1.4m note the meter reading as 3 point disturb cable 2 position. 4. The losses due to the airgraps are tabulated above. These don’t with in the optical approximations form loss due to the airgrap. The losses measured with these cases are much lower than these expected. Result Thus the study of various types of losses that occur in optical fiber measurement of losses in db is determined. 9.TIME DIVISION MULTIPLEXING (TDM) AIM:- To study and observe the TDM of four inputs signal. Apparatus required:S.no Equipments required Range Quantity 1 TDM Kit 1 2 Patch cord 10 3 Power supply 1 4 Cro 1 5 Cro probe 2 6 Function generator 1 Theory:-Time division multiplexing use the four bit of sampling such that narrow pulses with wide range space between them can be used by signals from other source also the space are of fixed length, narrow pulse may be used which permits generation of higher order multiplexing. The fig shows four channels inter placed in the TDM systems. A set 16 www.androiderode.com www.androiderode.com of Multi pulses consisting of 1 sample from each of the Multi I/p channels is called a “Frame”. The receivers as a four pole analog switch that demultiplexes the channels. Procedure:The TDM unit consist of 1. Sine wave 1. 2. Square wave 3. Triangle wave 4. Sine wave 2. Experimental procedure:-Connect the four channel inputs 25hz,500hz,1khz,2khz to the I/P of Txr CH0,CH1,CH2 andCH3 respectively. Connect Tx clock to Rx clock.Connect Tx Cho to Rx Cho Connect Tx to Rx Observe the multiplexed data circuit. TDX, Txr, clock at find transmitter sync at Tx Cho. Observe the demultiplexed signals at the Rxr across. The o/p of 4th order LPF at CHO, CH1, CH2, CH3 respectively. Observation From the above setup, we can observe that signals are recorded at the Rxr faithfully and one varied from each other. By removing the other two lines apart from the Txr, we find that be reconstructed signals suffer from several distortion. RESULT:- From the above observations, we conclude that synchronization is a very critical aspect of any TDM signals. 10. ANALOG TRANSMITTER AND RECEIVER Aim: To construct an analog communication system and test its performance. Apparatus required: S.no Name of the Equipments Range Qty 1 Sampling and Reconstruction trainer kit 1 2 Patch cords 10 3 Power supply 1 4 Cro 1 5 Cro probe 2 6 Function generator 1 Theory:- An analog source produces an O/P that can have a one of the continuous possible value when an analog signal is connect over an analog communication system, the full message is used at all times. To send the same analog signal over a digital system requires only its sampled values.At the receiver original message is reconstructed completely according to the sampling theorem. A band limited signal of maximum FM signal can be completely reconstructed using a sampling frequency whose maximum frequency is at least two times FM are the sampling interval Is<=1/2 times. 17 www.androiderode.com www.androiderode.com PROCEDURE:-The analog signal sampling and reconstruction unit consists of three modules. Sampling signal generation and control logic. Sampling circuits of logic. Filter section. Sampling signal generation and control logic.The 6.4 Mhz crystal oscillator generates the clock the decade counter divides the frequency by 10 and the counter generates the basic sampling frequency from 320khz to 20khz. Sampling circuits of logic.The analog s CD4016 Ic switches at the rate of the sampling rate speed. The sampling clock acts as the control I/P AND WHEN EVER THE SWITCH IS on ie., t on the sampling frequency, the base band signal from the unity gain is latched to the O/P the switch changes it state at the rate of sampling frequency selected Filter:-At the reconstruction side the low pass filter samplex the signal to produce the original source signal. A low pass filter is a few selective circuit. The second order low pass filter as it on and its roll at 40db decade. Experimental procedure:-Connet the 2khz signal the analog I/P by means of patch cords. Observe the sampling O/P wave form at that ampled output. Connect this sampled o/p to the fourth order low pass filter. Observe the reconstructed signal at the sampled & hold o/p at the o/p. Connect the sample hold o/p to the I/p of second order low pass filter. Connect the sample hold o/p to the sixth order low pass filter I/p. Observations Observe the signal is reconstructed more faithful in 4th order low pass filter compare to the 2nd order filter. Since the role of filter increases the performance and efficiency also increases resulting in more production reconstruction of the original signal. Result:- Thus the analog transmission and receiver performance is tested. 11. FSK MODULATION AND DEMODULATION Aim:- To study the aspect of frequency shift keying modulation with kit. Apparatus required:S.no Equipments required Range Quantity 1 FSK kit 1 2 Patch cord 10 3 Power supply 1 4 Cro 1 5 Cro probe 2 6 Function generator 1 Theory: FSK modulation:- In this type of modulation, the modulated o/p shift between 2 frequency for all one to zero transistors. The two carrier sine signals are generated by employing and oscillator built around a PLL the 2 signals are setup the modulator is simple 2:1 multiplexer that latches one of these carriers to the o/p depending on the 18 www.androiderode.com www.androiderode.com control i/p. The control i/p is driven by modulating data which is to be keyed and the o/p FSK wave represents a carrier of 1mhz for all one” and 0.5mhz for all zeros. Experimental Procedure:- Connect SIN 1 to the I/p of the modulator. Connect SIN 2 to the I/p of the modulator. Connect data of the control i/p of the modulator. Connect space of the control modulating data. Observations:- Observe the FSK modulation o/p and the modulating the data in the two channels of the oscilloscope. Observing modulated carrier and constructed data with respect to the modulating data. Interference:-Since the blanking ability and the time response of the PLL is limited, a small phase close exists between the recovered data and the modulating data. Demodulation: FKS detectors are built around PLL logic. The phase detector o/p of the PLL directly gives the FSK detected o/p provided atleast one of the modulation frequency falls within the range of PLL refer the block diagram. The phase locked oscillator can be used to a demodulated a frequency shift keyed signal. The VCO in the above fig. In basically a frequency modulator and oscillators at the centre frequency then no signal is being received or when the modulation on the receive carrier is zero. Under the later condition, the oscillator o/p is exactly the same has the received signal (F in),and the phase detector circuit puts out a “O” signal. When the incoming frequency varies because of modulation to F in+f7, the phase comparator o/p create an o/p signals, which drives the Vco freq., o/p until it again time at Fin+AF. The signal appearing at the i/p to the vco us the sum of a fixed DC bias puts the com o/p signal. Since the OSC shift to high frequency and for this to be tune the i/p, there must tracking. Now if modulation drives the received signal freq., low, the OSC will also be forced to move low in freq. And comparator o/p will adjust itself to the vale necessary to procedure this frequency. If the received signal freq., Varying in accordance with modulation signal. The value in accordance with the modulating signal. The PLL centre freq., and clock range fixed around 1Mhz. A LPF at the o/p will remove the carrier components bias voltage, leaving only the signal. Experimental Procedure:1. Establish the same connection for FSK modulation. 2. Connect the FSK modulated o/p to the FSK demodulation. 3. Connect scope to the Control input of o/p’ s. Observations:-Observe the FSK modulated o/p and the modulati0n data in the two channels of the scopes modulating data in the two channels of the scopes. Observe incoming modulated and carrier and recover w.r.t the modulated date. RESULT:-Thus the study of aspects FSK modulation & demodulation.. 12. ASK MODULATION AND DE MODULATION Aim : to study the principle of ASK modulation and demodulation. Apparatus required: 1. ASK trainer kit 2. CRO 19 www.androiderode.com www.androiderode.com 3. Patch card. Theory In this experiment to function generated IC X 2206 it is used for generating ASK modulated signal. This IC consist of a VCD and analog multiplexer. The BCD is used to generate a high frequency carrier signal. The frequency is determined by the external timing capacitor and timing resistor. The frequency can be adjusted by varying resistance, the variable resistor 50K in series with pin 3, determine peak amplitude of the output waveform of the CD. 1. The output is presented PIN 2 2. Open the douggle switch in the data input section. 3. In the I/P and DC bias I/P circuit, adjust the variable resistor 1 /r5, so that DC voltage bias, as find out in previous section. 4. Connect T4 to T5. 5. User 1 KHZ square wave form source as the binary data source. 6. The 1 KHZ signal is obtained from the 100 KHZ carrier frequency divided by 100. 7. This is the modulating signal to be improved over the mid point bias values I/O voltage bias. 8. Set the binary data source signal to be 1 V peak using the amplitude control in this section. Set the oscilloscope in AC coupling and measure. 9. Close the toggle switch to connect the binary data with voltage bias. 10. Vary the amplitude of the signal i.c. the amplitude of the square pulse and obtain 100% modulation. 11. Draw the resulting waveform. 12. Vary the amplitude of modulating signal i.c. amplitude of square pulse and uptime 75% modulation. Draw the resulting waveform. 13. Select Cd,Rd, and connect in the detector circuit. 14. Connect the output of the ASK modulator output to the input of ASK demodulator circuit. 15. Observer the waveform at the peak detection of 1 channel of oscilloscope. 16. The recovered the signal. Simulate to the original modulating signal with some destruction. 17. Vary the amplitude and frequency to conform that the recovered signal follow the changes. Result;-Thus the ASK modulation and de modulation was tested. 13. PWM GENERATION AND DETECTION Aim : to understand generation and detection. To write pulse width modulation and test in. 20 www.androiderode.com www.androiderode.com To write demodulation test ct. Apparatus required: 1. PWM trainer kit 2. CRO Theory:-The PWM signal is generated by .comparator. The message signal is compared with the saw tooth and triangle wave carrier when amplitude of the message signal that is instant in that of carrier, comparator output is the pulse width modulation signal. PWM Pulse width modulation:-As discussed carrier, 8KHZ triangular carrier wave and 1KHZ sine wave modulating signal are given as two input to a comparator. The width of the message signal pulse at the given in time proportional to amplitude of message signal corresponds to wide one pulse, and a small value of the message a narrow pulse. PWM demodulation:-PWM output is given to the low pass filter to filter the harmonics and to generate sine wave. Procedure:Modulation:-Switch on the power supply using the oscilloscope measure the triangular wave form output.Vary the frequency and set into 8KHZ measure the square wave form output. Connect the 8HZ square wave output to the square input off TTL. Converter and measure the output using oscilloscope it should be 1 KHZ TTL output.Connect the 1 KHZ square wave input to sine wave there is a control of vary the amplitude and set the output.Measure the output, it should be 1 KHZ sine waves.Connect the 8KHZ triangle wave form as input and connect the 1 KHZ sine wave in other channelMeasure the PWM output in one channel and another channel.Vary the amplitude of input sine wave form and observe the pulse width variation in the PWM output. Demodulation:- Connect the PWM output to the input of PWM detection section. There is cascade low pass filter circuit which will be move the harmonic and produce the sine wave. Measure the output using oscilloscope. Compare with original sine wave input. Result;-Thus the results of PWM modulation and demodulation are studied. 14.Deflection Sensitivity of TV Picture Tube. Aim: to verify deflection sensitivity of both vertical and horizontal direction of picture. Apparatus require: Sno Equipment Range QTY 1 Power supply 0-30V 1 2 Rheostat 150Ώ /1 A 1 3 Ammeter 0 -1 A 1 4 TV Demonstrator Dynamic 1 5 Patch card 21 www.androiderode.com 5 www.androiderode.com Theory In TV picture tube the electron magnetic deflection is employed. The two pair of coil around the neck of the picture tube is illustrated. The orientation of magnetic field procedures by them. In combination the V and H deflection coil are called Yoke. This Yoke is fixed outside and clods the neck of the tube. The magnetic field of the coil reacts with electron beam to case its deflection. Each coil gets its respective sweep I/P from the associated sweep circuit and together they from the raster upon which the picture information tracked. Procedure:-The displacement of the spot from the centre of the screen is measured then the values displacement fro efficient values of the currents are tabulated. Until the spot reaches the end of current the screen measurement of H deflection sensitivity the coil is chosen in the HDC (Q) y1 +y2 the Rxr set is switched on and the above process is repeated. Here the deflection of the deoren path is in H direction when the power supply polarity is reversed then the measurement of electrons path coil opposite in direction. Deflecton sensitivity = displacement of beam in m / current in mA. Result Thus the deflection sensitivity of both vertical of horizontal direction of picture is obtained. 15. FAULT FIND IN SOUND SECTION Aim : to identify the created fault in sound section and to rectify the same result. Apparatus required: S no Equipments Range QTY 1 Sound O/P circuit 1 2 Separator 1 3 TV demonstrator 1 4 Multi meter 1 Procedure Sound section The sound section was uses two ICs. TBA 1120’s and LA810. The former amplifiers the 5.5Mhz inter carrier FM signals to the sound IC’s. the detected sound O/P is taken from the pin no. 11 of TBA 10s and through C1 volume control. At the pin no 2. In IC CA810 delivers an audio O/P of about 4 watts to the 82 pf. Impedance loud speaker fault and rectification no sound. detective – ON, OFF switch. Open E1 start circuit silicon diodes in bridge circuit. Identify the components. Sound take OFF transformer. 1. The FM amp discrimination transistor TBA 120S. 2. Volume control front panel. 3. Tone control 4. Sound O/P IC TBA 810 with heat sink 5. O/P coupling condenser 1000f to the separator 22 www.androiderode.com www.androiderode.com 6. 6’’X4” 80_, PMLC. Trouble shooting of the sound section Faults and rectification Plane finger on the centre of the volume control 1. It makes speaker than heat half of the circuits is good 2. And trouble is indicated to be in front half 3. It gives any one 3 results 1. That means audio O/P circuit is dead due to falls in O/P voltage IC and biasing Voltage the tube. O/P transformer and speaker need to be tested. 2. Volume control does cause some changes in the speaker O/P 3. Hour or tiny bit of audio. 4. Trouble before the volume control test the audio IF and Audio detector. Result:-hus the identification of the created fault in sound section and rectification in the fault was found. 16. FAULTY FINDING IN VIDEO SECTION AND RECTIFICATION Aim: to identify the fault in the video section of a TV demonstrator and verify the same Apparatus required Sno Equipment Range 1 TV demonstrator 1 2 Multimeter 1 3 Wires 2 Procedure Any problem in the video or picture tube is mainly due to RF tuner. Video IF amplifier stage video amplifier of deflection coils are in video section Function of video IF section The main function is performed by this section. The functions are amplified by video IF, sound IF signals and the automatic gain control. Additional functions such as pro amp of video signal. Pre amplification of inter carrier signal, IF signal and noise limiting may also be provided. If either picture or sound is normal then the section is likely to be working normal. If raster is normal, but neighbor picture sound is received and an audio or video signal at the I/P of this section. Video amplifier stage: Video signal obtained from the IF sections are given to the video amplifier which amplify these signals to a level sufficient to drive the picture stage. The amplified signals are given to the cathode of the picture stage. The amplified signals are given to the cathode of the picture tube. This stage also attenuates the inter carrier sound IF present in the video signal and provide blanking of the retrace lines. The picture tube stage provides proper voltage to the picture tube which display the video signal in the forms of the picture which the helps of the line and frame sweeps. If the raster is normal and an video signals of about 2V is applied to the base of the driver transistor and the contrast 23 www.androiderode.com www.androiderode.com and brightness control are functioning properly then these stages are working normally. ResultThus the created faults in the video sections of the TV demonstrator is rectified. 17. FALULT FINDING IN PICTURE TUBE DEFLECTION SECTION AIM: to find the faults in picture tube deflection section and rectify it. Apparatus required: Sno Equipment Range QTY 1 TV demonstrator 1 2 Multimeter 1 3 Patch cards 5 Procedure A natural and eventual cause of picture tube failure is loss of emission at the cathode. The result is a dim picture. In a color set, the gray scale. Imbalance identifiers the weak rod gun. For example a cyan picture points to a weak rod gun remember the addition of cyon and red makes white. Although video circuits provides can cause implies symptoms the picture tube gives a few more dues first increase of low emission. The weak cathode takes a long time to worm upto procedure any emission at all a tube that takes a half twines to give a reassemble picture is de finding bad. Second the picture status OFF cyan instead of black and white, but then generally balanced procedure a neutral gray scale after 20 to 30 mm. A monochrome picture can be increased by tuning down the color control. A wind warmup time for emission from the red gun. An unbalanced gray scale also results from the weak emission. A third due to low emission of the saturation limiting of the beam current. The weak cathode current supply enough electrons for the height across area of the picture when other the brightness or contrast control is advanced the while appears to shown. When the picture tube is replaced either a new or a result tube can be used, rebuilt picture tube cost less because they use the old glass envelop or ‘dual’ but the internal parts are all new for same new tubes for replacement. Width This is a resistance set for optimum performance is for set value of this resistance the raster covers the entire screen in the horizontal direction.If due to some reason the width is reduced. Thus presents can be readjusted to raster original deflection. In face changing the gain of the horizontal deflection amplifier. Height With the help of this present the raster can be made to comr the entire section in the vertical direction amplifier circuit. UMf adjusting the height present we are infact arranging the gain of the amplifier stage increase height falls below the neutral level. The present may be adjusted to increase the gain of the vertical deflection amplifier. Result Thus the faults in deflection section rectified. 18. STUDY OF YAGI ANTENNA AIM: to study about the Yagi antenna details Apparatus required Sno Equipments 24 www.androiderode.com Range QTY www.androiderode.com 1 Director 10 2 Reflector 1 3 Dipole 1 4 Booster 1 5 Feed wire 30 mts Procedure The TV signals picked up the TV receiving antenna. Its input impedance is 300 and connecting the antenna to RF tuner by using 75 co – axial cable. Parts of Antenna 1. Dipole 2. Reflector 3. Director Reflector an director are called as parasitic dement. Director The gain of he directivity of the half wave dipole is increased by addition of director Yagi Antenna A folded dipole working in conjunction with a reflector and a system of direction are called Yagi Antenna. Length of dipole= λ/2 Length of reflector λ/2+ 0.05 λ/2 Length of director λ /2 – 0.4 λ/2 0.096 λ/2 Space between dipole reflector = 0.2λ Director of dipole = 0.12λ. Result Thus the study of Yagi antenna is verified. 25 www.androiderode.com