Exam 2

advertisement

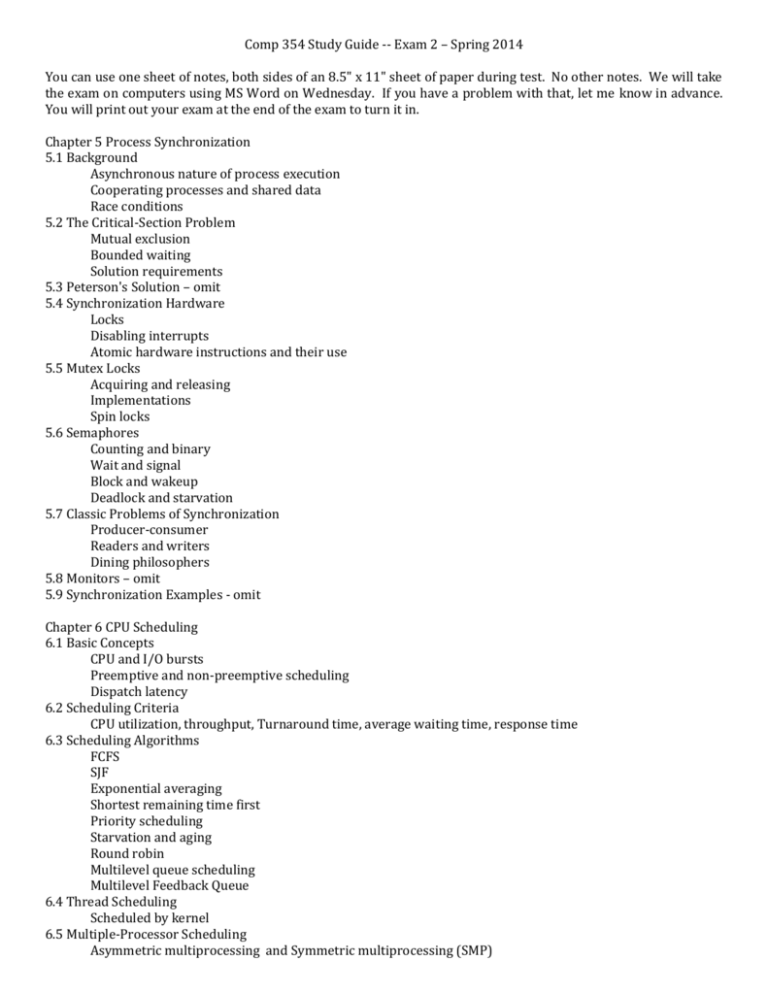

Comp 354 Study Guide -- Exam 2 – Spring 2014 You can use one sheet of notes, both sides of an 8.5" x 11" sheet of paper during test. No other notes. We will take the exam on computers using MS Word on Wednesday. If you have a problem with that, let me know in advance. You will print out your exam at the end of the exam to turn it in. Chapter 5 Process Synchronization 5.1 Background Asynchronous nature of process execution Cooperating processes and shared data Race conditions 5.2 The Critical-Section Problem Mutual exclusion Bounded waiting Solution requirements 5.3 Peterson's Solution – omit 5.4 Synchronization Hardware Locks Disabling interrupts Atomic hardware instructions and their use 5.5 Mutex Locks Acquiring and releasing Implementations Spin locks 5.6 Semaphores Counting and binary Wait and signal Block and wakeup Deadlock and starvation 5.7 Classic Problems of Synchronization Producer-consumer Readers and writers Dining philosophers 5.8 Monitors – omit 5.9 Synchronization Examples - omit Chapter 6 CPU Scheduling 6.1 Basic Concepts CPU and I/O bursts Preemptive and non-preemptive scheduling Dispatch latency 6.2 Scheduling Criteria CPU utilization, throughput, Turnaround time, average waiting time, response time 6.3 Scheduling Algorithms FCFS SJF Exponential averaging Shortest remaining time first Priority scheduling Starvation and aging Round robin Multilevel queue scheduling Multilevel Feedback Queue 6.4 Thread Scheduling Scheduled by kernel 6.5 Multiple-Processor Scheduling Asymmetric multiprocessing and Symmetric multiprocessing (SMP) Processor affinity Load balancing Hyperthreading 6.6 Real-Time CPU Scheduling Hard vs. soft real-time systems Application response time Rate monotonic scheduling Earliest Deadline First Scheduling (EDF) Proportional Share Scheduling 6.7 Operating-System Examples - omit Chapter 7 Deadlocks 7.1 System Model Resources and their use by processes 7.2 Deadlock Characterization 4 necessary conditions Resource allocation graphs 7.3 Methods for Handling Deadlocks Prevention and avoidance 7.4 Deadlock Prevention Preventing at least one of the necessary conditions 7.5 Deadlock Avoidance Safe state Maintaining a safe state by use of resource allocation graph Banker’s algorithm - omit 7.6 Deadlock Detection - omit 7.7 Recovery from Deadlock - omit Chapter 8 Main Memory 8.1 Background Virtual/logical memory space and physical memory space Memory address binding Base and limit registers Dynamic linking 8.2 Swapping Cost of context switching I/O complications 8.3 Contiguous Memory Allocation Dynamic allocation strategies Fragmentation Compaction and coalescing 8.4 Segmentation Segment table Address mapping 8.5 Paging Pages and page frames Page tables Address mapping TLB and effective access time Memory protection and shared access 8.6 Structure of the Page Table Hierarchical Paging Hashed Page Tables Inverted Page Tables 8.7 Example: Intel 32 and 64-bit Architectures IA-32 only 8.8 Example: ARM Architecture - omit