Updated DRAFT of instruction semantics

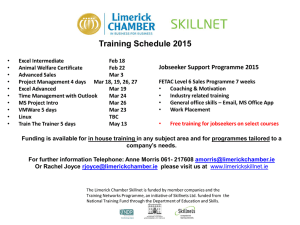

advertisement

Simulator Semantics Adapted from the description of the MARIE CPU presented by Linda Null and Julia Lobur in The Essentials of Computer Organization and Architecture, 4th ed., Jones & Bartlett Learning, 2015. The adaptations derive from design modifications which allow the PC and MAR to be incremented and to be loaded directly from the internal CPU bus. FETCH: 1. MAR←PC 2. IR ← M[MAR], PC += 1 DECODE: 1. CU.decode( IR[15:12] ), MAR ← IR[11:0]. In Table 1, X is shorthand notation for IR[15:12]. EXECUTE: The semantic activity for the execute phase of each instruction appears in the following table. Observe: 1. Not all possible four-bit patterns are used to represent opcodes. 2. The control unit uses the bits IR[11:10] in order to determine the condition to be evaluated for the Skipcond instruction (opcode = 0x8). 3. There is one clock cycle per numbered line of register transfers. 4. For simulation purposes, when multiple operations appear on a single numbered line of Register Transfer Language, simulate the operations in order from left to right. Table 1. RTL for the Modified CPU Opcode 0b0000 = 0x0 Instruction JnS X Register Transfer Language 1. MBR[11:0] ← PC 2. M[MAR] ← MBR; MAR += 1 3. PC ← MAR 0b0001 = 0x1 Load X 1. MBR ← M[MAR] 2. AC ← MBR 0b0010 = 0x2 Store X 0b0011 = 0x3 Add X 1. 2. 1. 2. 0b0100 = 0x4 Subt X 0b0101 = 0x5 Input MBR ← AC M[MAR] ← MBR MBR ← M[MAR] AC ← AC + MBR; set OVERFLOW accordingly 1. MBR ← M[MAR] 2. AC ← AC – MBR; set OVERFLOW accordingly 1. AC[7:0] ← InReg Notes 1. Jump and store return address 2. Used to transfer control to subroutines 3. Assumes increment capability for the MAR 1. Load the AC 2. Loaded value passes through the MBR 1. Store the value of the AC 1. Add a value to the AC; and 2. Store the result in the AC 1. Subtract a value from that of the AC 2. Store the result in the AC 1. Copy the content of the input register into the low order half of 2. 0b0110 = 0x6 Output 1. OutReg ← AC[7:0] 1. 0b0111 = 0x7 Halt 1. R ← 0 1. 0b1000 = 0x8 Skipcond 1. If (IR[11:10]==0x00 and AC<0) or (IR[11:10]==0x01 and AC==0) or(IR[11:10]==0x10 and AC>0) then PC += 1 1. PC ← IR[11:0] 1. 0b1001 = 0x9 Jump X 0b1010 = 0xA 0b1011 = 0xB Clear AddI X 1. 1. 2. 3. 0b1100 = 0xC JumpI X 1. PC ← M[MAR][11:0] 0b1101 = 0xD LoadI X 1. MAR ← M[MAR][11:0] 2. MBR ← M[MAR] 3. AC ← MBR 0b1110 = 0xE StoreI X 1. MAR ← M[MAR][11:0] 2. MBR ← AC 3. M[MAR] ← MBR 0b1111 = 0xF Not used AC ← 0 MAR ← M[MAR][11:0] MBR ← M[MAR] AC ← AC + MBR 2. the AC Advance the interrupt request pointer Copy the content of the low order half of the AC into the output register Stop the FETCH, DECODE, EXECUTE, CFI cycle by clearing the R flag Uses the extra bits, IR[11:10] to select whether to test the AC for a negative, zero or positive value. If the selected test condition is met, increment the PC, in order to skip the next consecutive instruction 1. Unconditionally transfer control to the instruction pointed to by X 1. Set the AC to zero 1. Use the value of X as a pointer from which to get the actual operand address. 2. Acquire the operand 3. Add the operand to the AC and replace the AC 1. Use the value of X as a pointer from which to get the actual jump target address. 1. Use the value of X as a pointer from which to get the actual operand address. 2. Acquire the operand 3. Load the operand into the AC 1. Use the value of X as a pointer from which to get the actual storage address. 2. Stage the AC into the MBR 3. Write the value of the MBR to M