a routing technique algorithm for vehicle navigation

advertisement

A ROUTING TECHNIQUE ALGORITHM FOR VEHICLE

NAVIGATION

Katikala Mamatha

M.Tech(VLSI & ES), Dept of ECE,

DRK Institute of Science and

Technology, Hyderabad, India

Email : mamatha.aash@gmail.com

`

Abstract : This paper is a DIJKSTRA’S

Somisetty Adilakshmi

Assistant Prof.,Dept of ECE,

DRK Institute of Science and

Technology, Hyderabad, India

Email: adilakshmi.s@gmail.com

INTRODUCTION

algorithm based architecture designed for the

The project deals with the vehicle

purpose of finding the shortest path between the

navigation using DIJKSTRA’S algorithm. The

nodes in vehicle navigation. Dijkstra's algorithm

data transmission time is increased with the

is a graph search algorithm that solves the

protocol standard. One of the section runs with

single-source shortest path problem for a graph

driver unit and LPC2929 with display unit and

with non-negative edge path costs, producing a

another PC as server section runs on a Matlab

shortest path tree. This algorithm is often used in

platform. Communications between two nodes

routing and as a subroutine in other graph

(hardware and application) are accomplished

algorithms. For a given source vertex (node) in

through IEEE 802.15.4. The user can give the

the graph, the algorithm finds the path with

source and destination node address to the server

lowest cost (i.e. the shortest path) between that

section. Using DIJKSTRA’S algorithm the

vertex and every other vertex

shortest path will be find out and graph plot will

be displayed on the server section. Using IEEE

Keywords: ROBOTICS, RTOS, GSM, ARM.

standard communication protocol the shortest

path will be feeded into the robotic module.

Using the path as a reference, the robot moves

in the ordered direction. After reaching the

destination node, the display unit displays the

name (particular place) of the particular node.

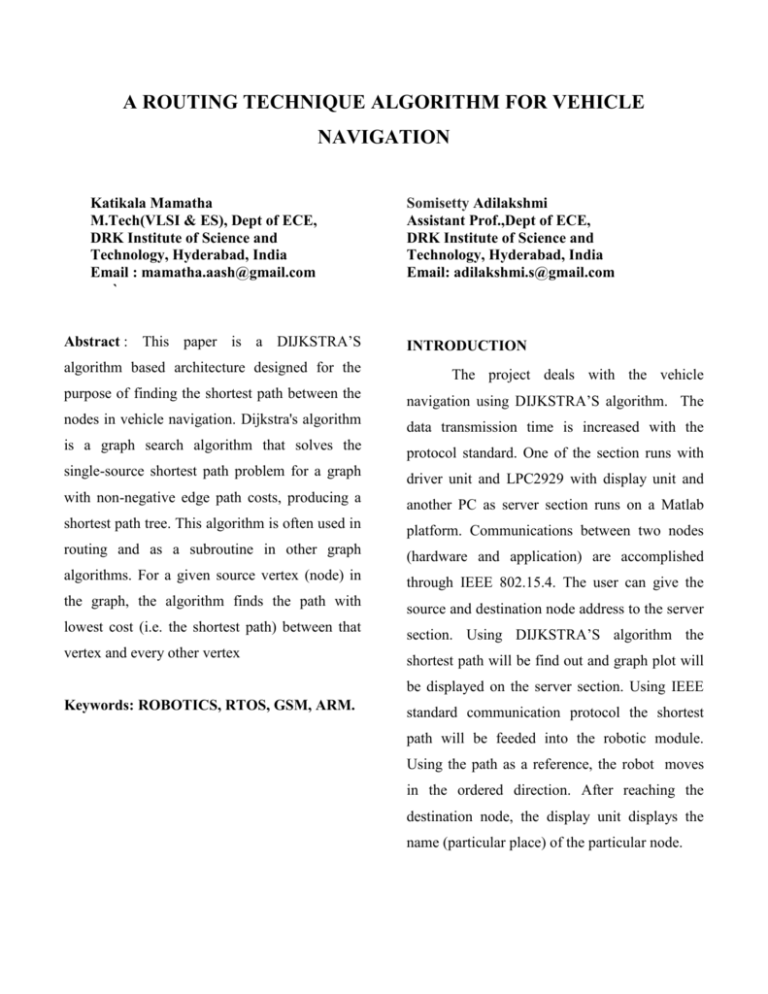

BLOCK DIAGRAM:

Two DTL buses (a universal NXP interface)

for interfacing to the interrupt controller and

Robot section:

the Power, Clock and Reset Control cluster

(also

called

subsystem).

Three

ARM

Peripheral Buses (APB - a compatible superset

ARM

Processor

Power

supply

U

A

R

of ARM's AMBA advanced peripheral bus) for

IEEE

802.15.4

Protocol

T

connection to on-chip peripherals clustered in

subsystems. One ARM Peripheral Bus for

event router and system control.

GPIO

The

LPC2926/2927/2929

configures

the

ARM968E-S processor in little-endian byte

order. All peripherals run at their own clock

Driver

unit

Display

unit

Driver

unit

frequency to optimize the total system power

consumption. The AHB-to-APB bridge used in

Motor 2

Motor 1

the subsystems contains a write-ahead buffer

one transaction deep. This implies that when

the ARM968E-S issues a buffered write action

to a register located on the APB side of the

Monitoring section

bridge, it continues even though the actual

write

IEEE 802.15.4

Protocol

Serial data

Transfer unit

Pro

Pro

may

not

yet

have

taken

place.

Completion of a second write to the same

subsystem will not be executed until the first

write is finished. The ARM968E-S is a general

HARDWARE DESIGN

purpose 32-bit RISC processor, which offers

ARM core:

high

ARM9 core:

consumption. The ARM architecture is based

The

LPC2926/2927/2929

consists

of:

performance and very low power

An

on Reduced Instruction Set Computer (RISC)

ARM968E-S processor with real-time emulation

principles, and the instruction set and related

support An AMBA multi-layer Advanced High-

decode mechanism are much simpler than

performance Bus (AHB) for interfacing to the

those

on-chip memory controllers

Instruction

of

microprogrammed

Set

Computers

Complex

(CISC).

This

simplicity

results

instruction

16-bit controller using 16-bit registers. This is

throughput and impressive real-time interrupt

possible because THUMB code operates on the

response from a small and cost-effective

same 32-bit register set as ARM code. THUMB

controller core. Amongst the most compelling

code can provide up to 65 % of the code size of

features of the ARM968E-S are: Separate

ARM, and 160 % of the performance of an

directly connected instruction and data Tightly

equivalent ARM controller connected to a 16-bit

Coupled

Write

memory system. The ARM968E-S processor is

buffers for the AHB and TCM buses Pipeline

described in detail in the ARM968E-S data sheet

techniques are employed so that all parts of the

The LPC2926/2927/2929 includes a 256 kB, 512

processing and memory systems can operate

kB or 768 kB flash memory system. This

continuously. The ARM968E-S is based on the

memory can be used for both code and data

ARMv5TE five-stage pipeline architecture.

storage. Programming of the flash memory can

Typically, in a three-stage pipeline architecture,

be accomplished via the flash memory controller

while one instruction is being executed its

or the JTAG. The flash controller also supports a

successor is being decoded and a third

16

instruction is being fetched from memory. In

integrated on

the five-stage pipeline additional stages are

addition to

added for memory access and write-back

LPC2926/2927/2929 includes two static RAM

cycles.

also

memories: one of 32 kB and one of 16 kB. Both

employs a unique architectural strategy known

may be used for code and/or data storage. In

as THUMB, which makes it ideally suited to

addition, 8 kB SRAM for the ETB can be used

high-volume

memory

as static memory for code and data storage.

restrictions or to applications where code

However, DMA access to this memory region is

density is an issue. The key idea behind

not supported.

Memory

in

a

high

(TCM)interfaces

The ARM968E-S

applications

processor

with

kB,

byte-accessible on-chip

the

EEPROM

LPC2926/2927/2929.

the two

32

kB

TCMs

In

the

THUMB is that of a super-reduced instruction

set. Essentially, the ARM968E-S processor has

LCD DISPLAY UNIT:

two instruction sets:

LCD DISPLAY

Standard 32-bit ARMv5TE set 16-bit THUMB

Liquid crystal displays (LCDs) have

set The THUMB set's 16-bit instruction length

materials which combine the properties of both

allows it to approach twice the density of

liquids and crystals. Rather than having a

standard ARM code while retaining most of the

melting point, they have a temperature range

ARM's performance advantage over a traditional

within which the molecules are almost as mobile

as they would be in a liquid, but are grouped

DIJKSTRA’SALGORITHAM:

together in an ordered form similar to a crystal.

This algorithm finds the shortest path from a

An LCD consists of two glass panels, with the

source vertex to all other vertices in a weighted

liquid crystal material sand witched in between

directed graph without negative edge weights.

them. The inner surface of the glass plates are

Here is the algorithm for a graph G with vertices

coated with transparent electrodes which define

V = {v1, ... vn} and edge weights wij for an edge

the character, symbols or patterns to be

connecting vertex vi with vertex vj. Let the

displayed polymeric layers are present in

source be v1.Initialize a set S = . This set will

between the electrodes and the liquid crystal,

keep track of all vertices that we have already

which makes the liquid crystal molecules to

computed the shortest distance to from the

maintain a defined orientation angle. One each

source.Initialize an array D of estimates of

polarisers are pasted outside the two glass

shortest distances. D[1] = 0, while D[i] = , for

panels. These polarisers would rotate the light

all other i. (This says that our estimate from v1 to

rays passing through them to a definite angle, in

v1 is 0, and all of our other estimates from v1 are

a particular direction. When the LCD is in the

infinity.)Essentially, what the algorithm is doing

off state, light rays are rotated by the two

is this:Imagine that you want to figure out the

polarisers and the liquid crystal, such that the

shortest route from the source to all other

light rays come out of the LCD without any

vertices. Since there are no negative edge

orientation,

appears

weights, we know that the shortest edge from the

transparent. When sufficient voltage is applied to

source to another vertex must be a shortest path.

the electrodes, the liquid crystal molecules

(Any other path to the same vertex must go

would be aligned in a specific direction. The

through another, but that edge would be more

light rays passing through the LCD would be

costly than the original edge based on how it was

rotated by the polarisers, which would result in

chosen.) Now, for each iteration, we try to see if

activating / highlighting the desired characters.

going through that new vertex can improve our

The LCD’s are lightweight with only a few

distance estimates. We know that all shortest

millimeters thickness. Since the LCD’s consume

paths contain subpaths that are also shortest

less power, they are compatible with low power

paths. (Try to convince yourself of this.) Thus, if

electronic circuits, and can be powered for long

a path is to be a shortest path, it must build off

durations.

another shortest path. That's essentially what we

and

hence

the

LCD

are doing through each iteration, is building

another shortest path. When we add in a vertex,

we know the cost of the path from the source to

stepping

motors,

as

well

as

other

high

that vertex. Adding that to an edge from that

current/high-voltage loads in positive-supply

vertex to another, we get a new estimate for the

applications. All inputs are TTL compatible.

weight of a path from the source to the new

Each output is a complete totem-pole drive

vertex.

This algorithm is greedy because we

circuit, with a Darlington transistor sink and a

assume we have a shortest distance to a vertex

pseudo-Darlington source. Drivers are enabled in

before we ever examine all the edges that even

pairs, with drivers 1 and 2 enabled by 1,2EN and

lead into that vertex. In general, this works

drivers 3 and 4 enabled by 3,4EN. When an

because we assume no negative edge weights.

enable input is high, the associated drivers are

The formal proof is a bit drawn out, but the

enabled and their outputs are active and in phase

intuition behind it is as follows: If the shortest

with their inputs. When the enable input is low,

edge from the source to any vertex is weight w,

those drivers are disabled and their outputs are

then any other path to that vertex must go

off and in the high-impedance state. With the

somewhere else, incurring a cost greater than w.

proper data inputs, each pair of drivers forms a

But, from that point, there's no way to get a path

full-H (or bridge) reversible drive suitable for

from that point with a smaller cost, because any

solenoid or motor applications. On the L293,

edges added to the path must be non-negative.By

external high-speed output clamp diodes should

the end, we will have determined all the shortest

be used for inductive transient suppression.

paths, since we have added a new vertex into our

set for each iteration.This algorithm is easiest to

CONCLUSION

follow in a tabular format. The adjacency matrix

of an example graph is included below. Let a be

The user can give the source and destination

the source vertex

node address to the server section. Using

L293D:

DIJKSTRA’S algorithm the shortest path will be

The L293 and L293D are quadruple high-current

find out and graph plot will be displayed on the

half-H drivers. The L293 is designed to provide

server

bidirectional drive currents of up to 1 A at

communication protocol the shortest path will be

voltages from 4.5 V to 36 V. The L293D is

feeded into the robotic module. Using the path as

designed to provide bidirectional drive currents

a reference, the robot

of up to 600-mA at voltages from 4.5 V to 36 V.

direction. After reaching the destination node,

Both devices are designed to drive inductive

the display unit displays the name (particular

loads such as relays, solenoids, dc and bipolar

place) of the particular node

section.

Using

IEEE

standard

moves in the ordered

REFERENCES:

[1] National Highway Traffic Safety Administration,”

Automotive Collision Avoidance Systems (ACAS) Final

Report”. August 2000.

[2] “Google Cars drive themselves in Traffic”, J. Markoff - The

New York Times, 2010 - bngumassd.org

[3] Tyler Folsom, “Social Ramifications of Autonomous Urban

Land Vehicles” IEEE International Symposium on Technology

and Society, May 2011, Chicago

[4] “A Method for Shortest Path Search using Extended

Dijkstra’s Algorithm”, IEEE International Conference on

System, Man and Cybernetics, 2000

[5] “Proof of a modified Dijkstra's algorithm for computing

shortest bundle delay in networks with deterministically timevarying links”, Lee, Fraser.S, IEEE Xplore 2011

[6] T.Imielinski and J.C. Navas, “GPS-Based Geographic

Addressing, Routing, and Resource Discovery,” Commun. ACM,

vol. 42, no. 4 Apr. 1999

[7]Q.Xu, R.Sengupta and D.Jiang, “Design and Analysis of

Highway Safety Communication Protocol in 5.9Ghz DSRC,”

Proc. IEEE VTC vol.57, no.4, 2003, pp. 2451-2455

AUTHOR BIOGRAPHY

S. Adilakshmi

She received her M.Tech from TKR College of

engineering

and

technology,

JNTUH,

Hyderabad. Currently she is a Asst. Professor at

DRK Institute Of Science & Technology,

JNTUH University, Hyderabad.

Dr. K Praveen Kumar received the Ph.D in

Microwave Antennas with EBG. Currently he is

a HOD at DRK Institute Of Science &

Technology, JNTUH University, Hyderabad.

Dr. Balasowrya received the Ph.D and currently

he is a Principal at DRK Institute of Science &

Technology, JNTUH University, Hyderabad.

Katikala Mamatha

Completed her U.G in Electronics and

Communication Engineering from JNTU,

Hyderabad, she is pursuing her Masters from

DRK Institute Of Science & Technology, with

specialization in VLSI&ES, JNTUH University,

Hyderabad.