CPRE281_Final-Project - Electrical and Computer Engineering

advertisement

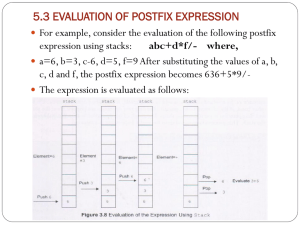

Cpr E 281 FINAL PROJECT FINAL Project ELECTRICAL AND COMPUTER ENGINEERING IOWA STATE UNIVERSITY Objectives The main objective of the final project is to teach you how to put together all of the class material that you have learned so far in order to program the Altera DE2 board to carry out an independent activity. You will have to design a circuit to realize one digital machine that accepts input from switches and outputs to LEDs and 7-segment displays. Project Selection Feel free to choose any one of the following three projects. They are all of approximately the same difficulty. Your grade will not depend on the project that you pick, as long as you implement the entire project. If you don’t like any of the provided projects, then you also have the option of specifying your own project. If there was something that you always wanted to do, now is your chance. The only two constrains are that your project must: 1) include a state machine; and 2) run on the boards proved in the lab. Project #1: Random Number Generator Design a system that will fill a register file with pseudo-randomly generated numbers. This system will include a register file to hold the values, an initial seed value for the random number generator, and a state machine to generate the random digits to be written to the register file. You will first need to create a 4-bit wide 4-register file. It will have the following inputs and outputs: R0 - R3: Contents of registers 0 through 3 (displayed via HEX LEDs). WA: Write register address WR: Write enable LD_DATA: Write data input The next component is an 8-bit parallel-in serial-out right-shift register. The seed value to the random number generator will be loaded into this register. Then, one-by-one, the bits of the seed will be shifted right out of the shift register to be fed to the state machine. Let the value that is about to be right-shifted out of the register be called S. 1 Cpr E 281 FINAL PROJECT FINAL Project ELECTRICAL AND COMPUTER ENGINEERING IOWA STATE UNIVERSITY The last major component is the pseudo-random number state machine. In each clock cycle, it uses the previously computed digit and S to compute a digit in the range [0, 9] to be written into the register file. Its next state logic is defined as follows. Let f(t) represent the previously generated digit and S be the current input from the shift register: Note that this arithmetic is performed with respect to mod 10 so that the values remain in the range [0, 9]. (For example, if f(t) = 2 and S = 1, the next number will be 9). As these digits are computed, the results are stored in the register file sequentially. This means that at the first clock edge (i.e. t = 1), the output of the state machine should be written into R0 of the register file. Then at the second clock edge, the output should be written into R1. Consider how you might create this behavior with a 2-bit counter. Use Case: 1. User loads an 8-bit value seed into the shift register. 2. Cycle the clock 8 times. At each active edge: a. Another random number is written to the register file. b. The shift register shifts its contents to the right. c. The state machine begins calculating the next number using the current number and the next value in the seed. 3. Observe the resulting values in the register file. Some Notes: It may be helpful to display the contents of the shift register on the LEDs. Since f(0) = 0, the first number that will be written into the register file will be either 0 (in the case that S = 0) or 7 (if S = 1). The described use case will cycle through the register file twice, since the seed is 8 bits while the register file contains only 4 registers. Sample Case: The seed 11000011 will yield the sequence 7, 4, 2, 6, 8, 4, 1, 8 with final register values R0 = 8, R1 = 4, R2 = 1, R3 = 8. 2 Cpr E 281 FINAL PROJECT FINAL Project ELECTRICAL AND COMPUTER ENGINEERING IOWA STATE UNIVERSITY Project #2: Stack Arithmetic For this circuit, you will need to implement a simple finite state machine to control a stack of 4-bit unsigned integers. If you are not familiar with the stack abstract data type, check http://en.wikipedia.org/wiki/Stack_(abstract_data_type) . You have to design this stack so that its contents can be used to perform some simple arithmetic. The user must be able to perform four operations: Push - A value is added to the top of the stack. Pop - The top-most value is removed from the stack. Pop with Add - The top two values on the stack are popped from the stack, added together, and the result is pushed back onto the top of the stack. Pop with Subtract - The top two values on the stack are popped from the stack, used to perform subtraction, and the result is pushed back onto the top of the stack. (The first value popped is subtracted from the second value popped.) To keep things simple, the maximum stack depth will be four. Your circuit should display the complete contents of the stack on HEX3 through HEX0. To be clear, HEX3 should display the first value pushed onto the stack, HEX2 should display the second value, and so on. The seven-segment display should have no lit LEDs if it does not contain a value. Some notes about error handling: Stack Overflow - If a push is performed, but there is no more room on the top of the stack, the contents of the stack should not be changed and the stack overflow register should be set. Hook this register up to an LED to notify the user. This register and LED should remain set and lit until the board is reset. Stack Underflow - If any of the three pop operations are performed without enough values on the stack to perform that operation, the contents of the stack should not be changed and the stack underflow register should be set. Hook this register up to an LED to notify the user. This register and LED should remain set and lit until the board is reset. Some hints: You may find it convenient to implement the stack using a 4-bit register file with 4 registers, two read ports, and one write port. If there is only one value on the stack, only HEX3 should display a value. The other HEX displays should not have any lit LEDs. 3 Cpr E 281 FINAL PROJECT FINAL Project ELECTRICAL AND COMPUTER ENGINEERING IOWA STATE UNIVERSITY Project #3: Sorting Machine Design a sorting machine that sorts numbers in either ascending or descending order. The idea is to design a two-port read two-port write register file with k registers. You must choose a value for k in your design and it must be at least 4. The data are stored in registers using some input switches (address and data are specified by switches). Then there are two counters, C1 and C2. A four state machine sorts the numbers using the bubble sort algorithm as follows. Load the registers with initial values. Start the machine in state S0. State S0: C1 is initialized to 0. Go to state S1. State S1: C2 is initialized to C1 + 1. Go to State S2. State S2: Read the contents of the two registers from the two addresses specified by C1 and C2. Call these values D1 and D2. Feed D1 and D2 into a maximizer/minimizer circuit, which will yield MAX and MIN on two ports. At the clock edge, MAX is written into register C1 and MIN is written into register C2. This will swap the values if they were out of order or keep them the same if they were in order. If C1 = k-2 then Go to State S3 Else if C2 = k-1 then Increment C1 and Go to State S1 Else Increment C2 and Go to State S2 State S3: Registers are sorted and displayed on 7-segment displays. Done. 4 Cpr E 281 FINAL PROJECT FINAL Project ELECTRICAL AND COMPUTER ENGINEERING IOWA STATE UNIVERSITY Notes on the Three Provided Projects The three projects descriptions outline all necessary details for the projects. If you choose to implement one of these projects, you must follow all details listed in the project description. Your implementation, at a minimum, should satisfy all implementation features and constraints as specified in this document. This means that if you do not implement a certain feature or reduce the complexity of the project you will lose points. You are allowed to work beyond the basic functionality so long as the implementation improves upon the specified design. It would be helpful to discuss any such changes with a TA. Project #4: Specify Your Own Project Propose a project of your own design. It should include a state machine and must be of sufficient difficulty. If you choose this option, you must discuss your intended design with your lab TA to see if the project would be appropriate for this class. This discussion can be over e-mail. Please contact your lab TA. 5