SampleFinalWAns

advertisement

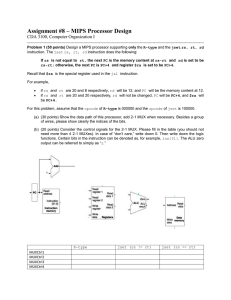

CDA 3100 Final Exam Fall 2013 Name : Part I. Multiple choice questions Please select one answer for each question by circling the index of the answer. 5 points for each question. You may also write down a short sentence in the provided space to explain your choice. If your choice is wrong but your explanation is partially correct, partial credit will be given. 1. The binary representation of -33ten in 8 bits in 2’s complement is (a) 11101110 (b) 11100011 (c) 11011111 (d) None of the above. 33 –> 32+1 -> 0010 0001 -> 1101 1110 -> 1101 1111, c 2. Assume the current values in $t0 and $t1 are 0 and 1, respectively. What will be the content in $t0 after the following instructions? xori $t0, $t1, 6 srl $t0, $t0, 2 (a) 5. (b) 6. (c) 7. (d) None of the above. D, 1 3. Assume the content of array A is 0,1,2,3,4,5,6,7,8,9. What will the content in this array be after the following instructions? la $t0, A li $t1, 8 add $t1, $t1, $t0 lw $t1, 0($t1) sw $t1, 4($t0) (a) (b) (c) (d) 0,2,2,3,4,5,6,7,8,9 0,1,2,3,8,5,6,7,8,9 0,8,2,3,4,5,6,7,8,9 None of the above. a 4. Assume the current values in $t0 and $t1 are 0 and 1, respectively. What will be the content in $t0 after the following instructions? beq P3_L0: add beq P3_L1: add (a) (b) (c) (d) $t0, $t0, $t0, $t0, $t1, $t0, $t1, $t0, P3_L1 $t1 P3_L0 $t1 1 2 3 None of the above. c 5. Which statement is true if the processor runs into the following code segment? jal P5_L0 P5_L0:jal P5_L2 P5_L1:jr $ra P5_L2:addi $ra, $ra, 4 j P5_L1 (a) (b) (c) (d) Eventually, the processor will repeatedly execute jr $ra and then j P5_L1. The processor will execute jr $ra exactly once. The processor will execute jr $ra exactly twice. None of the above. a. 6. Please read the following Verilog module: module statem (clk, O); input clk; output [1:0] O; wire D1, D0, Q1, Q0, Q1bar, Q0bar; assign D0 = Q1bar; Dff1 C0 (D0, clk, Q0, Q0bar); assign D1 = Q1bar | Q0; Dff1 C1 (D1, clk, Q1, Q1bar); assign O[1] = Q1; assign O[0] = Q0; endmodule Which of the following statements is true? (a) (b) (c) (d) It generates a sequence of 0222222… It generates a sequence of 032032032.. It generates a sequence of 012301230123…. None of the above. b 7. Which statement is true about the datapath below? (a) (b) (c) (d) The data path supports lw. The data path supports sw. Both of the above. None of the above. b 8. The following datapath supports R-type, lw, sw, and beq. Which of the following statements is true if we decide to support less instructions? (e) (f) (g) (h) a If only to support R-type and lw, we need exactly 3 2-1 MUX. If only to support R-type and beq, we need exactly 2 2-1 MUX. Both of the above. None of the above. 9. Consider the MIPS processor that supports the R-type, lw, sw, and beq instructions. Suppose $t0 is holding 9, $t1 is holding 4, the data memory location 4*i is holding value i, when we encounter the following instruction: beq $t0, $t1, L1 where L1 is the 4th instruction after the beq instruction. Suppose the control signal for a 2-1 MUX is 0 if we do not care about its value. What will be the stable values showing at ports WriteData of the register file and WriteData of the data memory during the execution of this instruction? (a) 1 and 9. (b) 5 and 4. (c) 20 and 4. (d) None of the above. b 10. Consider the MIPS processor that supports the R-type, lw, sw, and beq instructions. Suppose we mistakenly connected the RegWrite signal (the one that controls if the WriteRegister in the register file is changed to WriteData at the next rising edge of the clock) to 1, but have made no other mistakes. Suppose the instruction is sw $t0, 4($t1) while $t0 and $t1 are storing 8 and 12, respectively. Suppose the control signal for a 2-1 MUX is 0 if we do not care about its value. Which of the following statements is true? (a) (b) (c) (d) c No register will be changed because sw only writes to memory. Register 20 will be changed to 12 at the next rising edge of the clock. $t0 will be changed to 16 at the next rising edge of the clock. None of the above. Part II. Short answer questions Problem 1 (10 points) Please read the following MIPS code and answer the questions. A: .data .word 12, 34, 67, 1, 45, 90, 11, 33, 67, 19 .text .globl main main: la $a0, A la $a1, 10 la $a2, 35 jal f1 done: li $v0,10 syscall # these two lines tell the simulator to stop f1: li $v0, 0 li $t0, 0 f1L0: sll $t1, $t0, 2 add $t1, $t1, $a0 lw $t1, 0($t1) slt $t2, $t1, $a2 beq $t2, $0, f1L1 addi $v0, $v0, 1 f1L1: addi $t0, $t0, 1 bne $t0, $a1, f1L0 jr $ra a) (2 points) When the program just finishes executing “lw $t1, 0($t1)” for the first time, what is the value in $t1? 12 b) (2 points) When the program just finishes executing “slt $t2, $t1, $a2” for the first time, what is the value in $t2? 1 c) (2 points) When the program just finishes executing “beq $t2, $0, f1L1” for the first time, will the next instruction to be executed be “addi $v0, $v0, 1”? yes d) (2 points) When the program just finishes executing “bne $t0, $a1, f1L0” for the first time, will the next instruction to be executed be “jr $ra”? no e) (2 points) When the function returns, what is the value in $v0? 6 Problem 2 (8 points) Please read the transition diagram and complete the next state table. Assume states S0, S1, S2, and S3 are encoded as 00, 01, 10, and 11, respectively. X=1 S0 X=0 X=1 X=0 S3 X=1 S1 X=0 X=0 X=1 X=1 S2 X=1 Q1 0 0 0 0 1 1 1 1 Q0 0 0 1 1 0 0 1 1 X 0 1 0 1 0 1 0 1 D1 0 1 1 0 0 1 0 1 D0 0 0 1 0 1 1 0 0 Problem 3 (6 points) Please read the following next state table and write down the logic functions for D1 and D0. (This is not the answer to the previous problem.) Q1 0 0 0 0 1 1 1 1 Q0 0 0 1 1 0 0 1 1 X 0 1 0 1 0 1 0 1 D1 1 0 0 1 0 0 0 1 D0 1 1 0 1 1 0 1 0 D1 = Q0X + ~Q1~Q0~X D0 = ~Q1~Q0 + ~Q1X+Q1~X Problem 4 (10 points) Suppose we need to design a circuit that has two inputs, clk and X, and produces one output bit Y. X may change every clock cycle, where the change happens at the falling edge of the clock. The circuit samples X at every rising edge of the clock. Y should be 1 if the last 4 bits of X are “1011” from the least recent bit to the most recent bit. Please draw the state transition diagram of this circuit. Close to an arc, show X=1 or X=0. Name the states as S0, S1,… , and so on. X=1 X=0 S1 X=1 S0 X=0 X=0 X=1 X=0 S4 S2 X=0 X=1 S3 X=1 Problem 5 (16 points) Design a MIPS processor supporting only the sw and the AAA rd, rs, rt instruction. The AAA rd, rs, rt instruction does the following: If rs is equal to PC, the next PC will be changed to the value of rt, and rd will be changed to the value of rs; otherwise, rd will be changed to be memory value at address rs. For this problem, assume the opcode of sw is 000000 and the opcode of AAA is 100000. (a) (8 points) Please design the datapath for this processor, add 2-1 MUX when necessary. Please show clearly the indices of the bits near the wires. Please give clear indices to the 2-1 MUXes starting from 1. (b) (4 points) Please determine the values of the control signals for the 2-1 MUXes by filling in the table. In case of “don’t care”, write down “X.” Assume other control signals have been generated correctly. (c) (4 points) Please write down the logic functions for the control signals for the 2-1 MUXes. Certain bits in the instruction can be denoted, for example, as instuct[31]. The ALU zero output can be denoted simply as “zero.” When deriving the logic functions, if the value of a control signal is “don’t care” under a certain condition, assume it should be 0. If rs is equal to PC, the next PC will be changed to the value of rt, and rd will be changed to the value of rs; otherwise, rd will be changed to be memory value at address rs. MUXCtrl1 MUXCtrl2 MUXCtrl3 MUXCtrl4 M1 = instruct[31] & zero M2 = ~instruct[31] M3 = instruct[31] & ~zero M4 = instruct[31] & ~zero sw 0 1 0 X AAA (rs == PC) 1 0 x 0 AAA (rs != PC) 0 0 1 1