Lab 11 Data Acquisition System

advertisement

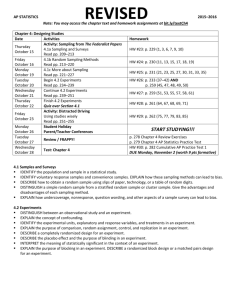

ECE 381 Lab 11 – Data Acquisition System Data Acquisition System Objective Develop a PSoC design that will provide the user with a menu of sampling and waveform reproduction choices. Specifically, the option to sample one of two separate analog inputs and store those samples to one of four 8kB memory blocks in a 32kB SPI SRAM. Sampling of an input will only occur when indicated by the user. The user can select among a range of sampling rates. The user will also be presented with an option of reproducing two of those four stored signals out to two different DACs at the specified sampling rate. Hardware Configuration This project uses the same SPI SRAM configuration as the previous lab. Make sure the PSoC and SRAM are powered off of the external power supply as before. Use PSoC project template found in the files directory of the lab web page as a starting point. Review the [Chip] view and take note of all user modules, their configuration, and how a Counter8 user module named DelSigClock is used to make a custom DelSig ADC clock source. Also review the Pinout window and make a note of all named and configured ports. Construct two PSoC analog input protection circuits as shown below and connect them to pins named CHANNELA_IN and CHANNELB_IN respectively. This input protection circuit will prevent excessive input voltage from damaging the PSoC. It also superimposes a VDD/2 offset voltage on the input signals and eliminates the need for the function generator to have a DC offset. For proper operation, the function general amplitude should be limited to +/-VDD/2. You must understand how this circuit works and be able to explain it. ECE 381 Lab 11 – Data Acquisition System The following figure shows the equipment connections. It does not show the analog input protection circuits, the common ground connections, the external power supply, or RS-232. The stand-alone function generator and the Digi-Designer’s function generator are used to provide two unique signals for Channels A and B. Verify their voltages are less than +/-VDD/2 before connecting them to the input protection circuit and that the output frequency is within the Nyquist limit for the specified sampling rate. Requirements In order correctly display the stored waveforms on the oscilloscope, the PSoC must make a trigger pulse (from an initial Low state, make a rapid High-Low transition) on the external trigger input when the selected point in the stored waveform should be displayed. The oscilloscope must be configured for Falling-Edge, Normal Mode Triggering, on the External Trigger input. At startup, your application should offer the user a menu allowing them to specify the following parameters: The input channel (A or B, corresponding to pins named CHANNELA_IN or CHANNELB_IN) to be sampled and into which 8kB memory block the samples should be stored. The memory blocks to be sent to each of the two DACs when outputting samples. Once output is started, it should loop on these blocks until the user presses any key in the terminal window. You are allowed to let the system finish outputting the remaining samples in a block before stopping. Both DACs must reproduce their respective memory block simultaneously. You may optionally allow the user to specify that only one of the DACs produce output. The sampling rate to use: 1.25ksps, 1.5ksps, 1.875ksps, 2.5ksps, 3.125ksps, 3.75ksps, 6.25ksps, 7.5ksps, and 9.375ksps. The relative address within the 8kB blocks, at which, the PSoC will generate a trigger pulse for the oscilloscope. The address may be specified in either hex or decimal, however, invalid addresses should not be accepted. ECE 381 Lab 11 – Data Acquisition System Any invalid input should produce an error message. When sampling, the system must store samples in the SRAM at the specified sampling rate. When outputting samples, both DACs must update at the specified sampling rate. The output rate should be at the currently selected sampling rate and not at the same sampling rate that was used when they were stored. Testing Verify that your design meets all the requirements specified above. You must also verify that the sampling rate requirements for both the ADC and DAC are met.