Logic Minimization: Boolean Algebra & Karnaugh Maps

advertisement

Chapter 4

4.1

Logic Minimisation

Boolean Expressions and Definitions

Boolean Algebra uses certain notation and terms which must be known in order to

understand the principles and theories which are presented here. To begin with the following

definitions are commonly encountered :

a variable is a symbol, for example A , used to represent a logical quantity, whose value

can be 0 or 1.

the complement of a variable is the inverse of a variable and is represented by an over

bar, for example A .

a literal is a variable or the complement of a variable.

Addition and multiplication are used extensively in Boolean Algebra and the behaviour of

such operations is important. The previous chapter presented the algebraic representations of

the seven basic logic gates, and it was shown that the OR gate represents Boolean addition

and the AND gate represents Boolean multiplication. This is further expanded upon below.

Boolean Addition ( )

Boolean addition is equivalent to the OR operation; if any of the inputs are 1 then the output

is also 1. For example:

0+0+0

0+0+1

0+1+0

0+1+1

1+0+0

1+0+1

1+1+0

1+1+1

=

=

=

=

=

=

=

=

0

1

1

1

1

1

1

1

In Boolean algebra a sum term is a sum of literals. In a logic circuit a sum term is produced

by an OR operation with no AND operations involved, for example A B C D .

33

Boolean Multiplication ( )

Boolean multiplication is equivalent to the AND operation; if all of the inputs are 1 then the

output is 1. For example:

000

001

010

011

100

101

110

111

=

=

=

=

=

=

=

=

0

0

0

0

0

0

0

1

In Boolean algebra a product term is the product of literals. In a logic circuit a product term

is produced by an AND operation with no OR operations involved, for example ABC D .

4.2

The 3 Laws of Boolean Algebra

The 3 laws of Boolean algebra are :

1. the Commutative Laws

2. the Associative Laws

3. the Distributive Law

Each of these is examined in turn.

1. Commutative Laws

Commutative law of Addition

Commutative law of Multiplication

A B B A

AB BA

34

2. Associative Laws

Associative law of Addition

Associative law of Multiplication

A ( B C ) ( A B) C

A( BC ) ( AB )C

3. Distributive Law

Distributive Law

4.3

A( B C ) A B A C

The 12 Rules of Boolean Algebra

The 12 rules of Boolean algebra are :

1

A 0 A

2

A1 1

3

A 0 0

4

A 1 A

5

A A A

6

A A 1

7

A A A

8

A A 0

9

AA

10

A AB A

11

A AB A B

12

( A B )( A C ) A BC

Note that the variables A, B or C can represent a single variable or a combination of

variables.

35

4.4

DeMorgans’ Theorems

DeMorgans’ Theorems provide mathematical verification of the equivalency of the NAND

and negative input OR gates and the equivalency of the NOR and negative input AND gates

(see Chapter 3, section 3.9).

Theorem 1

AB A B

Theorem 2

A B A B

Theorem 1 states that the complement (inverse) of ANDed variables is the same as the

complement (inverse) of the variables ORed.

Theorem 2 states that the complement (inverse) of ORed variables is the same as the

complement (inverse) of the variables ANDed.

Once again A and B can represent a single variable or a combination of variables.

4.5

Simplification using Boolean Algebra

As has been indicated in Chapter 3 and mentioned again in this chapter Boolean expressions

can be represented by logic gates and vice-versa. In fact the purpose of studying Boolean

algebra is purely based on this fact. By representing a logic circuit as a set of Boolean

expressions it is possible to simplify those expressions using Boolean algebra and hence

produce a more efficient (in terms of gates) logic circuit. Simplification, therefore, is the goal

of using Boolean algebra.

Below is an example of the use of some of the rules of Boolean Algebra to simplify the

ALARM example encountered in the laboratory.

36

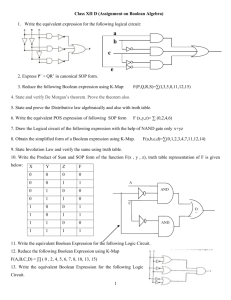

EXAMPLE – ALARM CIRCUIT (LABORATORY 1)

Truth Table

Inputs

ABC

000

001

010

011

100

101

110

111

Day

Monday

Tuesday

Wednesday

Thursday

Friday

Saturday

Sunday

Output

f

X

1

0

0

1

0

1

0

1. X = don’t care

The operation of the circuit can be described by the Boolean expression

f A B C A B C AB C

which can be implemented using the circuit below.

A’

f

B’

C’

A B C

37

In the above example input ABC = 000 is a ‘DON’T CARE’ or ‘CAN’T HAPPEN’

condition. In this case it is convenient to make the circuit output f = 1 for ABC = 000 , since

this results in a simpler circuit. Including this output, gives the revised Boolean circuit

expression

Don’t Care Term

f A' B' C ' A' B' C AB' C ' ABC '

A' B' ( C ' C ) AC ' ( B' B )

- Distributive Law

A' B' AC '

- Rule 6 & Rule 4

{ (A' B' )' .(AC ' )' }'

- De Morgan' s Theorem 2

which gives the simplified circuit below

f

B’

A B C

38

4.6 Logic Minimisation Using Karnaugh Maps

4.6.1 Introduction

When a logic circuit is represented as a truth table, the behaviour of the circuit can be

described in algebraic terms using a Boolean equation. It is often then desirable to minimise

the number of terms used to describe the output, ie simplify the Boolean equation of the

circuit. By doing this the complexity of the resultant underlying digital circuit is obviously

decreased. This in turn leads to simpler and cheaper design. We have already seen a simple

example where the laws of Boolean algebra can be used to do this, and this is generally the

case in any situation. Simplification will always occur when we can use the distributive law

to create terms of the form, eg, AB (C + C’), which simplifies to AB. Repeatedly doing this

as often as possible leads to progressive circuit simplification. However, the process is quite

tedious, even for relatively simple expressions. The diagrammatic method of Karnaugh

maps effectively provides a systematic approach for effectively achieving the same

minimisation process in a few simple steps.

4.6.2 Minterm Notation

Before going on to study Karnaugh maps, let us consider a short-hand notation for Boolean

expressions, which we have already seen are most often expressed in sum-of-products

(AND-OR) form. A short-hand form of the AND-OR representation is known as minterm

notation.

Expressions in standard SOP form can also be written in minterm expansion notation. For

example given the Standard SOP expression below, with the variables A,B,C,D :

X A B C D A B C D A B C D A B C D A B C D A B C D A B CD A B CD A B C D A B C D A B C D

0110

0100

0010

0000

1010

1000

0101

0001

0111

0011

1111

we can also write :

f ( A, B ,C , D ) m0 m1 m2 m3 m4 m5 m6 m7 m8 m10 m15

which can be further abbreviated to :

f ( A, B, C, D) m(0,1,2,3,4,5,6,7,8,10,15)

domain

minterms Standard SOP terms

This is referred to as the minterm expansion.

39

4.6.3 Don’t Care terms – Incompletely Specified functions

Sometimes when a digital circuit is specified some input combinations are not required or

cannot occur. This means that out of the total number of combinations available as inputs not

all are used. An example is an input that can go from 0 to 9. This requires 4 bits/variables to

represent all 10 combinations but totally 16 are possible. Hence 6 are unused. If the output is

X then we say that the function X is incompletely specified. The remaining 6 unused terms

are referred to as Don’t Care terms, and are represented by an X in a truth table. If we decide

that we desire an output of 1 when a 1,3,5,7 is detected and 0 otherwise then we can write

down the behaviour of the circuit as:

Truth Table

Inputs

ABCD

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

Output

X

0

1

0

1

0

1

0

1

0

0

X

X

X

X

X

X

Minterm Expansion

f ( A, B ,C , D ) m( 1,3 ,5 ,7 ) d ( 10 ,11,12 ,13 ,14 ,15 )

4.6.4 Karnaugh Maps

A Karnaugh map is similar to a truth table in that it presents all of the possible values of the

input variables and the resultant output for each value. Karnaugh maps are organised into

cells. The map is arranged so that each cell is only one bit different from any adjacent cell,

hence gray scale axes are used. This also allows the cells in the Karnaugh map to wrap

around. This will be made clear with several examples. The number of cells required for each

Karnaugh map is equal to the total number of combinations possible for the given number of

40

input variables, i.e. 2n where n is the number of input variables. This is often referred to as

the level of the Karnaugh map. For example a 4-level Karnaugh map will have 24 = 16 cells.

Karnaugh maps are only used from 2 to 6 levels, but we will consider only 2, 3 and 4

variable maps here. Each level of Karnaugh map will be looked at in turn to illustrate how

they are used, but before that an overview of how each level of Karnaugh map is drawn will

be given. The minterm expansion numbers are placed in the appropriate cells, hence if a

minterm expansion for the expression is given populating the Karnaugh map is simple. This

can be referred back to later.

A

0

0

1

0

1

2

1

3

A

CD

10

0

0

1

3

2

1

4

5

7

6

C

00

01

11

10

00

0

1

3

2

01

4

5

7

6

10

11

3–Level Karnaugh Map

2–Level Karnaugh Map

A

01

C

A=1

11

00

A

B=1

AB

B

BC

B

12 13 15 14

8

4–Level

B Karnaugh Map

9 11 10

D

For each level of Karnaugh map numbers have been entered into the cells to indicate the

actual bit code that it represents, for example 10 = 1010 (for a 4-level Karnaugh map),

which in turn equals A B' CD' . It should be clear at this stage that each cell represents a

standard SOP term (or minterm).

This is the key to drawing Karnaugh maps. The digital circuit to be analysed and minimised

is first described in SOP form, or as a minterm expansion. This must be the case. From

this the Karnaugh map can be populated with 1s as the SOP expression indicates, the

remainder will be 0s or Xs (the Karnaugh maps can also be populated with Don’t Care terms

(represented by an X) if this is appropriate; the advantage of these is that they can be treated

as either 1s or 0s depending upon what is the most convenient).

41

Once the Karnaugh map has been populated with 1s, 0s and Xs as specified the only task that

remains is to group adjacent terms of the same state (usually 1) in groups of 2 raised to

any rational power, i.e. 1, 2, 4, 8, 16, 32, 64 and so on. The larger the group the simpler the

final expression. It is also possible for groups to overlap. This is often done to achieve a

larger group size, hence simplifying the final expression.

EXAMPLE : Simplify the following equation using a K-map (Karnaugh-map):

X A BC D A BC D A B C D A B C D AB C D AB C D A BCD A B CD A BC D A B C D ABC D

m6

m4

m2

m0

m10

m8

m5

m1

m7

m3

m15

SOLUTION : Draw the K-map and minimise.

CD

AB

C

00

00

1

01

1

11

0

10

1

A

01

0

4

12

8

1

1

11

1

5

13

0

0

9

1

1

10

3

7

15

1

11

0

1

1

2

6

14

0

B

10

1

D

X B D A BC D

The equation is determined by looking at each region on the K-map and deciding which part

the group belongs to. For example, looking at the red highlighted group we see that it is

inside the B region (the yellow, orange and red areas on the diagram below), but the group is

not big enough to fill the entire B region so we look to see where else it lies. If we look again

we see that it also lies in the C region (the orange and red part of the B region), but not in all

of the C region that occurs inside the B region. Looking again we see that as well as lying in

the B region and the C region it also lies in the D region (the red part of the B region). A has

no effect as it lies in both A and A .

42

CD

AB

C

00

01

11

10

00

0

1

3

2

01

4

5

7

6

11

A

10

B

12 13 15 14

8

9 11 10

D

The remaining terms are similarly determined. One thing of importance to note is that (as

was mentioned earlier) the groups can wrap around the Karnaugh map because every cell is

adjacent to the next, including at the edges. If we look at the four SOP terms that make up the

blue region ( B D ) we find that they are adjacent. The following table shows this.

0000

0010

1010

1000

The red bits show which of the bits change, the grey bits show B and D .

The technique of looking for the appropriate regions on the Karnaugh map can also be

applied to populating it as the next example shows.

EXAMPLE : Simplify the following equation using a K-map (Karnaugh-map):

X ABC D A B C D B C B C D

SOLUTION : Draw the K-map and minimise.

CD

AB

C

00

01

11

10

00

1

1

1

1

01

0

0

0

0

11

0

0

0

1

10

1

1

1

0

A

B

D

43

X ABC D A B B C B D

The remainder of this topic uses examples to illustrate a variety of points about Karnaugh

map minimisation.

EXAMPLE : A digital system has 10 possible input combinations, that is from 0 to 9 in binary.

When a 5, 6, 7 or 8 is detected the output is 1, otherwise 0. If the inputs are

labelled from A to D, with A being the most significant bit then the output X can

be described as :

X A BC D A BC D A BC D AB C D

m5

m6

m7

m8

The SOP terms from 10 to 15 are not required and are Don’t Care terms.

SOLUTION : Draw the K-map and minimise.

CD

AB

C

00

01

0

00

0

01

0

11

X

10

1

4

12

A

8

0

1

11

1

5

13

X

0

9

0

1

10

3

7

15

X

11

X

2

0

6

1

14

X

B

10

X

D

X AD BC B D

44

EXAMPLE : Minimise the expression given below using a suitable Karnaugh map :

X A BC A BC A B C AB C

m2

m3

m1

m4

SOLUTION : Draw the K-map and minimise.

C

B

BC

00

A

0

A

1

0

1

01

0

4

1

0

11

1

1

5

0

AB

10

3

7

C

1

0

0

1

2

00

0

1

6

01

1

1

11

0

0

10

1

0

A

C

B

X A B A C AB C

Example : Laboratory Alarm Enable / Disable Circuit

The Boolean equation of the circuit is

f A B C A B C AB C

and there is a don’t care term

fd A B C

Therefore we can write

f ( A, B ,C ) m( 1,4 ,6 ) d ( 0 )

The Karnaugh Map is

00

A

X A B AC

B

BC

A

0

x

1

1

01

0

4

1

0

11

1

5

0

0

10

3

7

0

1

2

6

C

45

CD

CD

C

AB

00

01

11

AB

10

0

1

3

2

4

5

7

6

12

13

15

14

8

9

11

10

00

01

B

0

1

3

2

4

5

7

6

12

13

15

14

8

9

11

10

A

10

10

D

D

CD

CD

C

01

11

C

AB

10

00

0

1

3

2

00

4

5

7

6

01

12

13

15

14

8

9

11

10

00

01

B

11

A

01

A

1

3

2

4

5

7

6

12

13

15

14

8

9

11

10

00

01

1

D

11

3

CD

C

AB

10

00

2

00

01

11

10

0

1

3

2

4

5

7

6

12

13

15

14

8

9

11

10

00

4

5

7

6

01

01

12

13

15

14

B

11

A

B

10

C

0

10

0

D

CD

11

11

10

AB

B

11

11

00

10

01

01

AB

11

00

00

A

C

B

11

8

9

11

10

10

A

10

D

D

4-Level Karnaugh Map Templates

46