ARM7 Architecture: ISA, Registers, Instructions, and Addressing

advertisement

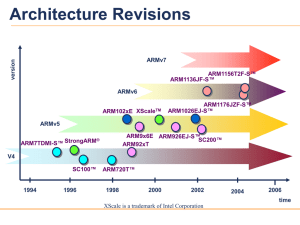

ARM versions

• ARM architecture has been extended over

several versions.

• We will concentrate on ARM7.

The Slides revised from “Computer from

Components”, Morgan Kaufman

ARM ISA

• All instructions are 32-bit long (not include

Thumb)

• Register and memory word are 32-bit

• Memory address is 32-bit

• Byte addressed

• Can be configured at power-up as either

little- or bit-endian mode

Note: There is a 64-bit ARM ISA

© 2000 Morgan

Kaufman

Overheads for Computers as

Components

ARM Registers

r0

r1

r2

r3

r4

r5

r6

r7

r8

r9

r10

r11

r12

r13 (SP)

r14 (LR)

r15 (PC)

0

31

CPSR

NZCV

CPSR: Current

Program Status Register

Status bits

• Every arithmetic, logical, or shifting

operation sets CPSR bits:

– N (negative), Z (zero), C (carry), V (overflow).

• Examples:

– -1 + 1 = 0: NZCV = 0110.

– 231-1+1 = -231: NZCV = 1001.

ARM data instructions

• Basic format:

ADD r0,r1,r2

– Computes r1+r2, stores in r0.

• Immediate operand:

ADD r0,r1,#2

– Computes r1+2, stores in r0.

ARM data instructions

• ADD, ADC : add (w.

carry)

• SUB, SBC : subtract

(w. carry)

• RSB, RSC : reverse

subtract (w. carry)

• MUL, MLA : multiply

(and accumulate)

© 2000 Morgan

Kaufman

• AND, ORR, EOR

• BIC : bit clear

• LSL, LSR : logical shift

left/right

• ASL, ASR : arithmetic

shift left/right

• ROR : rotate right

• RRX : rotate right

extended with C

Overheads for Computers as

Components

Load/store instructions

• LDR, LDRH, LDRB : load (half-word, byte)

• STR, STRH, STRB : store (half-word, byte)

Address modes

• Register indirect : LDR r0,[r1]

• With two registers : LDR r0,[r1,r2]

• With 2nd register negated:

LDR r0,[r1,-r2]

• With 2nd register shifted:

LDR r0,[r1,-r2,LSL#2]

• with a base register and 12-bit offset:

LDR r0,[r1,#4]

Address modes

• Register indirect : LDR r0,[r1]

• With two registers : LDR r0,[r1,r2]

• With 2nd register negated:

LDR r0,[r1,-r2]

• With 2nd register shifted:

LDR r0,[r1,-r2,LSL#2]

• with a base register and 12-bit offset:

LDR r0,[r1,#4]

LDR and STR as pseudoinstructions

• LDR and STR may also be pseudo-instructions

LDR r1, label

STD r1, label

• R15/PC is used as the based register, and label

is encode as its offset to PC

• They work if and only if label is within [-4095,

+4095] of PC

Array Access

• Assume X in r0, i in r1, a in r2, all int type

a = X[0];

LDR r2, [r1]

a = X[2];

LDR r2, [r1,#8]

a = X[i];

LDR r2, [r0,r1,LSL #2]

LSL: Logic shift left

Example: C assignments

• C:

c = a + b;

• Assembler:

LDR

LDR

ADD

STR

r0, a

r1, b

r3,r0,r1

r3, c

;

;

;

;

get value of a

get value of b

compute a+b

c = a+b

ARM Condition and Branch

• All instructions can be conditionally

executed, testing CPSR:

– EQ, NE, CS, CC, MI, PL, VS, VC, HI,

LS, GE, LT, GT, LE

– Example, execute if EQ: ADDEQ r1, r2, r3

• Branch operation:

B #100

– Can be performed conditionally

– Example: BEQ Branch if equal

– BEQ is the B instruction with condition code EQ

Example: if statement

if (a > b) { c = a; } else { c = b; }

; compute and test condition

LDR r0, a

; get value of a

LDR r1, b

; get value for b

CMP r0,r1

; compare a < b

BLE fblock

STR r0, c

B endif

else:

STR r1, c

endif:

; if a <= b, branch to else

; c = a

; c = b

Conditional Instruction

Implementation

if (a > b) { c = a; } else { c = b; }

; compute and test condition

LDR r0, a

; get value of a

LDR r1, b

; get value for b

CMP r0,r1

; compare a < b

STRGT r0, c

STRLE r1, c

; if GT, c = a

; if LE, c = b

ARM subroutine linkage

• Branch and link instruction:

BL foo

– Copies current PC to r14.

– Equivalent to MIPS jal

• To return from subroutine:

MOV r15,r14

– r15 is the PC in MIPS

ARM Call Convention

In MIPS terms

•r0 – r3: Parameters and return value, also

temporary

•r4 – r8, r10, r11: Saved temporary

•r9: Usage is Platform-dependent

•r12: Temporary

•r13: Stack pointer, preserved

•r14: Link register

•r15: The program counter

Extra Slides

ARM ADR pseudo-op

• ADR and ADRL pseudo-op generate

instruction required to calculate address

• ADRL for long-range

ADR r1, FOO ; get the addr for FOO

LDR r2, [r1] ; load FOO to r1

ARM move instructions

• MOV, MVN : move (negated)

MOV r0, r1 ; sets r0 to r1

ARM comparison

instructions

•

•

•

•

•

CMP : compare

CMN : negated compare

TST : bit-wise AND

TEQ : bit-wise XOR

These instructions set only the NZCV bits of

CPSR.

MIPS only has SLT, and BEQ/BNE takes two

register operands

Additional addressing

modes

• Base-plus-offset addressing:

LDR r0,[r1,#16]

– Loads from location r1+16

• Auto-indexing increments base register:

LDR r0,[r1,#16]!

• Post-indexing fetches, then does offset:

LDR r0,[r1],#16

– Loads r0 from r1, then adds 16 to r1.