here

advertisement

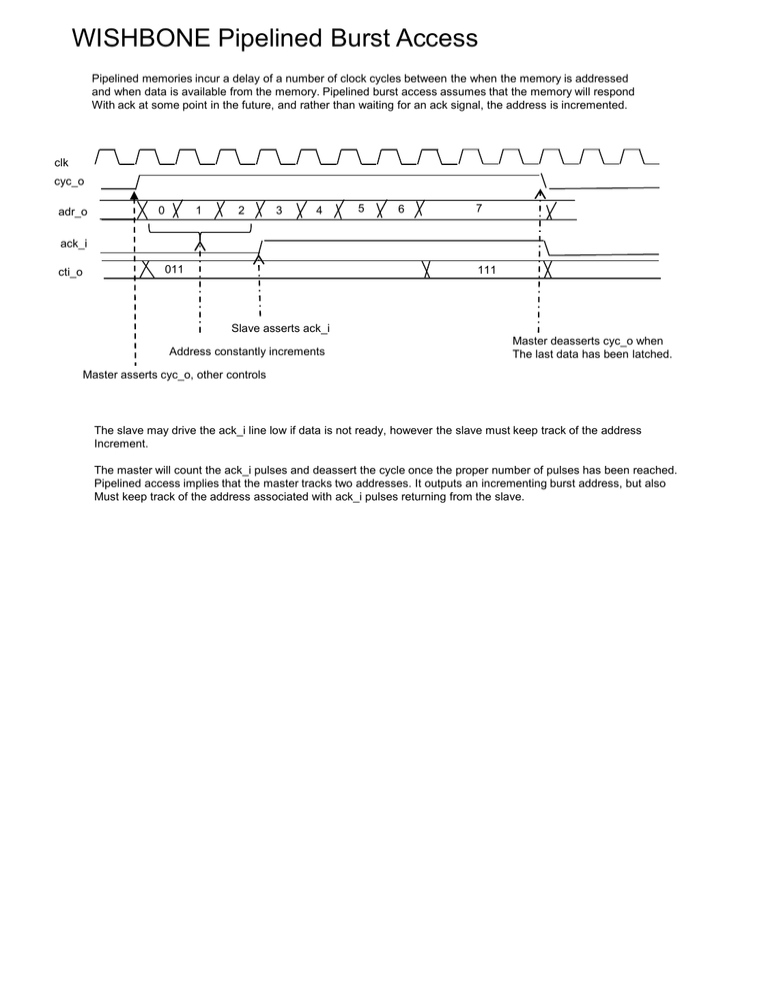

WISHBONE Pipelined Burst Access Pipelined memories incur a delay of a number of clock cycles between the when the memory is addressed and when data is available from the memory. Pipelined burst access assumes that the memory will respond With ack at some point in the future, and rather than waiting for an ack signal, the address is incremented. clk cyc_o adr_o 0 1 2 3 4 5 6 7 ack_i cti_o 011 111 Slave asserts ack_i Address constantly increments Master deasserts cyc_o when The last data has been latched. Master asserts cyc_o, other controls The slave may drive the ack_i line low if data is not ready, however the slave must keep track of the address Increment. The master will count the ack_i pulses and deassert the cycle once the proper number of pulses has been reached. Pipelined access implies that the master tracks two addresses. It outputs an incrementing burst address, but also Must keep track of the address associated with ack_i pulses returning from the slave.