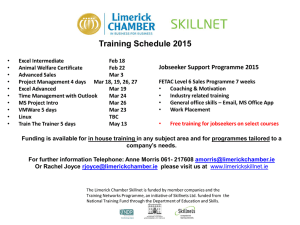

Fetch-Decode-Execute

advertisement

Computer Architecture and the Fetch-Execute Cycle The Fetch-Decode-ExecuteReset Cycle Learning Objectives Describe in simple terms the fetch / decode / execute / reset cycle and the effects of the stages of the cycle on specific registers. The Fetch-Decode-ExecuteReset Cycle The following is an algorithm in diagrammatic form that shows the steps in the cycle. It is the control unit which controls and synchronises this cycle. Loads / copies / places / passes, decodes and executes. At the end the cycle is reset and the algorithm repeated. Key for following slides: PC / SQR Program Counter / Sequence Control Register MAR Memory Address Register MDR / MBR Memory Data Register / Memory Buffer Register CIR Current Instruction Register Fetch Memory CPU PC incremented by 1 of address of PC Copy next instruction MAR Copy of instruction in memory address held in MAR MDR Instruction CIR Decode PC CPU MAR MDR CIR Split instruction into operation code & address if present. Then decode operation code. Execute CPU PC Execute instruction (What is involved in this depends on the instruction being executed - demonstrated on the following slides). MAR MDR CIR Click an instruction or move on to see each instruction in turn. Jump Input / Load (number directly) Input / Load (from memory) Store Add (a number directly) Add (a number from memory) Output (directly from accumulator) Output (from memory) Jump instruction Execute Diagram Execute Jump PC CPU MAR MDR CIR Execute Jump CPU Copy of address part instruction (address to jump to). PC MAR MDR CIR Back to list of instructions Input / Load (number directly) into accumulator instruction Execute Diagram Execute Input / Load (number directly) into accumulator CPU PC MAR MDR Accumulator Number inputted / to be loaded. CIR Back to list of instructions Reason for the CIR & MDR As you can see the MDR is used to store the number inputted / to be loaded during the execution of this Input / Load instruction. Therefore, if there was no CIR register to hold the Input / Load instruction and as no register can hold more than one “thing” at a time the control unit would “lose” the Input / Load instruction. i.e. It would no longer “know” what it was supposed to do. You will find that the contents of the MDR may be modified for similar reasons during other later instructions. Back to list of instructions Load (from memory) instruction Execute Diagram Execute Load (from memory) PC CPU MAR Memory Copy of data in address held in MAR MDR Accumulator CIR Back to list of instructions Reason for the PC & MAR As you can see the MAR is now used to store the address part of instruction during the execution of this Load (from memory) instruction. Therefore if there was no MAR register the PC would be used to hold this address so the control unit would no longer know the correct address of the next instruction. You will find that the contents of the MAR may be modified for similar reasons during other later instructions. Back to list of instructions Store instruction Execute Diagram Assume data has either been inputted, loaded (directly or from memory) or a calculation has been performed. Any of the above will mean there is data in the accumulator and it is this data that will be stored. Execute CPU Store PC MAR Memory Copy of data in MDR stored in memory address held in MAR MDR Accumulator CIR Back to list of instructions Add (a number directly) instruction Execute Diagram Assume a number has already been inputted or loaded (directly or from memory) into the accumulator. Execute Add (a number directly) CPU PC MAR MDR ALU Accumulator NB. The ALU now does the arithmetic. Accumulator value is now the result of the addition. i.e. Accumulator = Accumulator + contents of MDR Number to be added. CIR Back to list of instructions Add (a number from memory) instruction Execute Diagram (Assume a number has already been inputted or loaded into the accumulator.) Execute Add (from memory) PC CPU MAR Memory Copy of number in memory address held in MAR MDR ALU Accumulator NB. The ALU now does the arithmetic. Accumulator value is now the result of the addition. i.e. Accumulator = Accumulator + contents of MDR CIR Back to list of instructions Output (directly from accumulator) instruction Execute Diagram Execute Output (directly from accumulator) CPU PC MAR Output data in accumulator Accumulator MDR CIR Back to list of instructions Output (from memory) instruction Execute Diagram Execute Output (from memory) Memory CPU MAR PC Output data in accumulator Accumulator Copy of data in memory address held in MAR MDR CIR Back to list of instructions Reset CPU PC Cycle is reset (restarted) by passing control back to the PC. Fetch – Decode - Execute – Reset Cycle in writing The following slides describe the cycle in writing. 1. Load the address of next instruction in the PC into the MAR. So that the control unit can fetch the instruction from the right part of the memory. 2. Copy the instruction/data that is in the memory address given by the MAR into the MDR. Fetch MDR is used whenever anything is to go from the CPU to main memory, or vice versa. 3. Increment the PC by 1. So that it contains the address of the next instruction, assuming that the instructions are in consecutive locations. 4. Load the instruction/data that is now in the MDR into the CIR. Thus the next instruction is copied from memory -> MDR > CIR. 5. Contents of CIR split into operation code and address if present e.g. store, add or jump Decode instructions. 6. Decode the instruction that is in the CIR. 6. Execute the instruction but what is involved in this depends on the instruction being executed (there are several different instructions you need to know about). If the instruction is a jump instruction then Execute Load the address part of the instruction in the CIR into the PC. If the instruction is an input / load (directly) instruction then take data input and place in accumulator. If the instruction is a load (from memory) instruction. Copy address part of the instruction (to load from) in the CIR into MAR. Copy data from memory address held in MAR to MDR. Copy data in MDR into accumulator. If the instruction is a store instruction then: Copy address part of the instruction (to store in) in the CIR into MAR. Copy data in accumulator to MDR. Copy data in MDR into memory address held in MAR. If the instruction is an add instruction then: Execute Copy address part of the instruction (of number to add) in the CIR into MAR. Copy number from memory address held in MAR into MDR. Add number in MDR to number in accumulator (accumulator will now hold the result). If the instruction is an output (directly from accumulator) then output number in accumulator. If the instruction is an output (from memory) instruction then: Execute Reset 7. Copy address part of part of the instruction (of data to output) in CIR into MAR. Output contents of MDR. Cycle is reset (restarted) by passing control back to the PC (step 1). Plenary Contents of PC loaded into MAR PC is incremented Contents of address stored in MAR loaded into MDR Contents of MDR loaded into CIR Instruction in CIR is decoded. PC (program counter) stores the address of the next instruction to be executed. MAR (memory address register) holds the address in memory that is currently being used MDR (memory data register) holds the data (or instruction) that is being stored in the address accessed by the MAR. CIR (current instruction register) holds the instruction which is currently being executed.