Internal Memory

advertisement

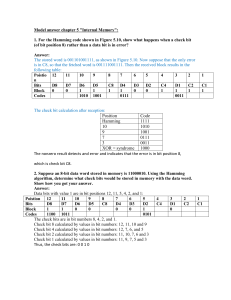

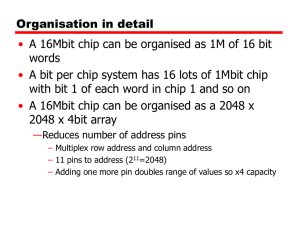

Computer Engineering II 4th year, Communications Engineering Winter 2014 Dr. Tamer Samy Gaafar Dept. of Computer & Systems Engineering Course Web Page http://www.tsgaafar.faculty.zu.edu.eg Announcements • Eng. Mohamed Atef will take the last 50 minutes of today’s class to cover the material required for Lab1. • Lab/Assignment Groups are posted or not?. • Lab1 is now posted. • Before your lab day, get prepared by reading the posted material very well so that you don’t waste much of your lab time trying to figure out what is going on. • Today’s lecture and lab presentation are posted. Lecture 2 Chapter 5. Internal Memory Technology (Cont.) 4 x 4 DRAM Typical 16 Mb DRAM (4M x 4) • • • • Logically, 4 square arrays of 2048 x 2048 elements. Each horizontal line connects to the Select terminal of each cell in its row. Each vertical line connects to the Data in/Sense terminal of each cell in its column. Reduces number of address pins — Multiplex row address and column address — 11 pins to address (211=2048) — Adding one more pin doubles range of values so x4 capacity Refreshing • • • • Refresh circuit included on chip. Disable chip. Count through rows. Data is read out and written back into the same location each cell is refreshed. • Takes time. • Slows down apparent performance. Chip Packaging • • • • 8-Mbit EPROM chip, 1M x 8. One-word-per-chip package. Address: A0-A19, Data: D0-D7 Vcc; power, Vss: ground, CE: chip enable, Vpp: programming voltage. • • • • • 16-Mbit DRAM, 4M x 4. Updatable data pins in/out. WE: Write Enable OE: Output Enable NC: No Connect even # of pins Module Organization 256 k byte memory • Available: 256 k x 1-bit chips Module Organization (2) 1 M byte memory • Available: 256 k x 1-bit chips Error Correction • Semiconductor memory is subject to errors. • Hard Failure —Permanent physical defect. —Memory cells cannot store data: stuck at 0 or 1, or switching. —Caused by harsh environments, manufacturing defects, or wear. • Soft Error —Random, non-destructive event that alters contents of one or more memory cells. —No permanent damage to memory. —Caused by power supply problems or alpha particles. • Detected/corrected using Hamming error correcting code. Error-Correcting Code Function Syndrome word Hamming Error-Correcting Code Data bits: 1110 A 1 1 0 1 Discrepancies Parity bits B 1 0 0 0 C Chosen so that total number of 1s in each circle is even. By checking the parity bits, discrepancies are found error can be easily found and corrected. How many check bits to use? • The comparison logic receives as input two K-bit values. • A bit-by-bit comparison is done by taking the XOR of the two inputs syndrome word. • Each bit of the syndrome word is 0 if there was a match in that position, otherwise, it is 1. • Syndrome word is K bits wide range 0 : 2K -1. • The value 0 indicates no error 2K -1 are left to indicate which bit was in error. • 2K -1 ≥ M + K Hamming Code 2K - 1 ≥ M + K 2K ≥ 9+K K = 4 1 0 0 1 1 0 1 0 12 11 10 9 8 7 6 5 4 3 Data bits 2 1 0 1 0 1 ? 1 0 1 1 0 0 1 ? ? 1 ? 0 1 0 Bit position 8 1 2 4 1 1 0 0 =? 1: 0 Bit position 8: 2: 4: 1 Hamming Code (2) 12 11 10 9 8 7 6 5 4 3 2 1 1 0 0 0 1 ? 0 1 0 1 ? 1 0 1 ? 1 ? • • • • • • • Assume error in bit 9. Recompute the check bits. Bit 1 = 0 (error). Bit 2 = 1. Bit 4 = 1. Bit 8 = 1 (error). Error is in bit position = 1 + 8 = 9 flip it (correction). Reading Material • Stallings, chapter 5, pages 164-173.