More Examples Dataflow/Behavioral Modeling

advertisement

More Examples

Dataflow/Behavioral Modeling

Section 4.12

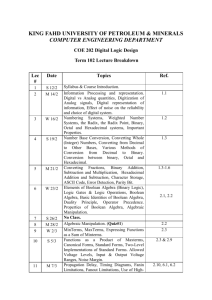

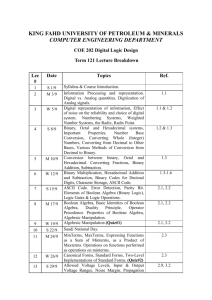

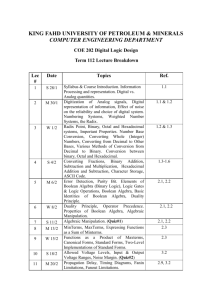

Schedule

14

15

L

16

17

L

N/A

N/A

N/A

18

19

L

3/3

3/5

3/6

3/10

3/12

3/13

3/17

3/19

3/20

3/24

3/26

3/27

Monday

Wednesday

Thursday

Monday

Wednesday

Thursday

Monday

Wednesday

Thursday

Monday

Wednesday

Thursday

More example of data flow versus behavior.

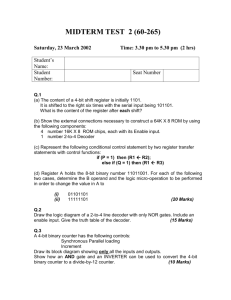

Test 1

Random number generator, mixed signal scope

Latches (1)

Flip-flops,

Flip-flops, D-latch,

Spring break

Spring break

Spring break

Analysis of clocked sequential circuit (1),

Analysis of clocked sequential circuit (2)

Clocked sequential circuit

Assign course project: hamming decoder.

Homework

• Hw2, hw2 & labs have been graded.

• Preview the lecture materials before

the lab.

Verilog Modeling

• Verilog Modeling Styles

– Gate-Level Modeling

– Dataflow Modeling

– Behavioral Modeling

Data Flow Modeling

Data flow modeling of a combinational logic uses a number of operators

that act on operands to produce desired results.

The keyword assign is used frequently in the dataflow modeling.

Behavior Modeling

• Behavioral modeling represents the digital circuits at a functional

and algorithmic level. It is used mostly to describe sequential

circuits, but can also be used to describe combinational circuits.

• Behavioral description use the keyword always. The event control

expression

• Specifies when the statements will execute.

• The target output statement must be of reg data type.

More Examples of Dataflow

Verilog HDL Operators

A and B are both 4-bit binary numbers.

A_gt_B is a logic 1 if A is greater than B.

A_lt_B is a logic 1 if A is less than B.

A_eq_B is a logic 1 if A is equal to B.

A==B is not the same as A=B.

Partial Test Bench for

mag_compare.v

Use concatenation to form a

4-bit array called B.

Output

Four-Bit Adder Example

{C4,S0, S1, S2, S3)=5-bit binary number

{A0, A1, A2, A3)=4-bit binary number

{B0, B1, B2, B3)=4-bit binary number

C0 is a 1-bit binary number

Four-Bit Adder Output

More Examples of Behavioral

Modeling

4-to-1 MUX

8-to-1 Mux

if and else example

8-to-1 MUX