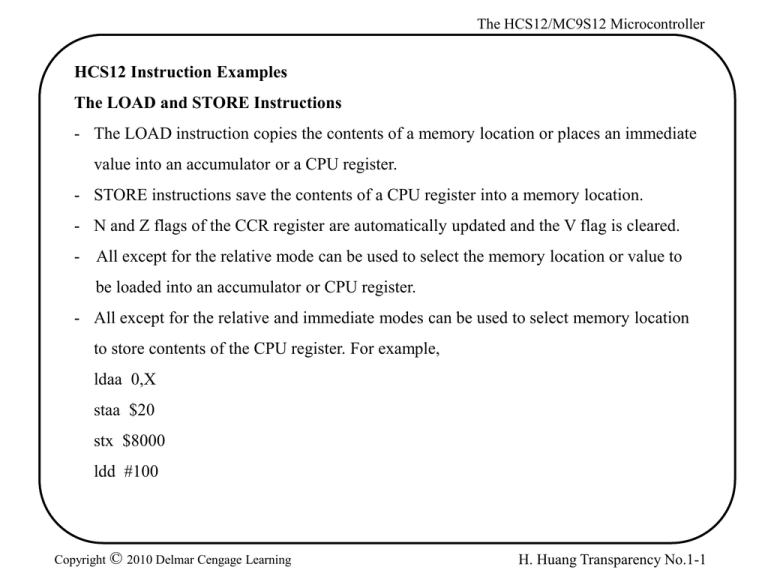

The HCS12/MC9S12 Microcontroller

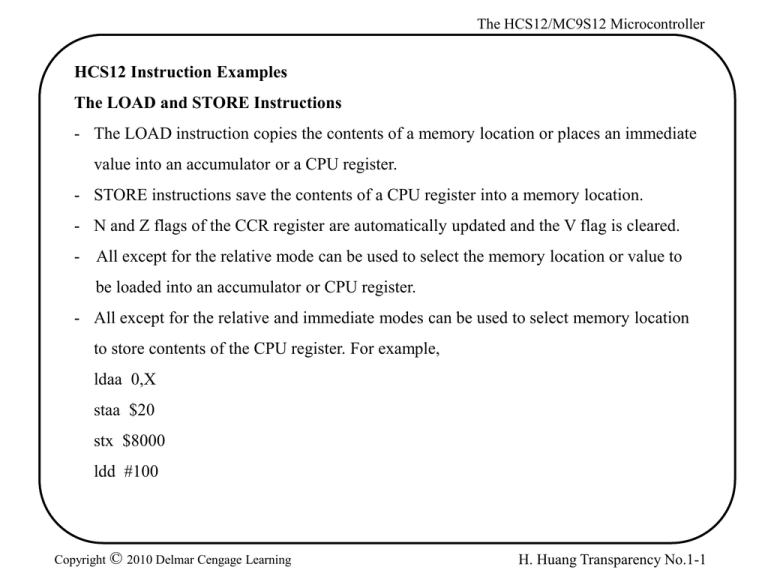

HCS12 Instruction Examples

The LOAD and STORE Instructions

- The LOAD instruction copies the contents of a memory location or places an immediate

value into an accumulator or a CPU register.

- STORE instructions save the contents of a CPU register into a memory location.

- N and Z flags of the CCR register are automatically updated and the V flag is cleared.

- All except for the relative mode can be used to select the memory location or value to

be loaded into an accumulator or CPU register.

- All except for the relative and immediate modes can be used to select memory location

to store contents of the CPU register. For example,

ldaa 0,X

staa $20

stx $8000

ldd #100

Copyright © 2010 Delmar Cengage Learning

H. Huang Transparency No.1-1

The HCS12/MC9S12 Microcontroller

Table 1.4 Load and store instructions

Load Instructions

Mnemonic

Function

Operation

ldaa <opr>

ldab <opr>

ldd <opr>

lds <opr>

ldx <opr>

ldy <opr>

leas <opr>

leax <opr>

leay <opr>

Load A

Load B

Load D

Load SP

Load index register X

Load index register Y

Load effective address into SP

Load effective address into X

Load efective address into Y

A ¬ [opr]

B ¬ [opr]

A:B ¬ [opr]:[opr+1]

SP ¬ [opr]:[opr+1]

X ¬ [opr]:[opr+1]

Y ¬ [opr]:[opr+1]

SP ¬ effective address

X ¬ effective address

Y ¬ effective address

Store Instructions

Mnemonic

Function

staa <opr>

stab <opr>

std <opr>

sts <opr>

stx <opr>

sty <opr>

Store A in a memory location

Store B in a memory location

Store D in a memory location

Store SP in a memory location

Store X in a memory location

Store Y in a memory location

Copyright © 2010 Delmar Cengage Learning

Operation

m[opr] ¬ [A]

m[opr] ¬ [B]

m[opr]:m[opr+1] ¬ [A]:[B]

m[opr]:m[opr+1] ¬ [SP]

m[opr]:m[opr+1] ¬ [X]

m[opr]:m[opr+1] ¬ [Y]

H. Huang Transparency No.1-2

The HCS12/MC9S12 Microcontroller

Transfer and Exchange Instructions

- Transfer instructions copy the contents of a CPU register or accumulator into another

CPU register or accumulator.

- TFR is the universal transfer instruction, but other mnemonics are accepted for

compatibility with the 68HC11.

- The TAB and TBA instructions affect the N, Z, and V condition code bits.

- The TFR instruction does not affect any condition code bits. For example,

TFR D,X

; [D] X

TFR A,B

; [A] B

TFR A,X

assigned to X

TFR X,A

; sign-extended of[A] X ; A is signed extended to 16-bit and

; X[7:0] A

Copyright © 2010 Delmar Cengage Learning

; lower 8 bits copied to A

H. Huang Transparency No.1-3

The HCS12/MC9S12 Microcontroller

- The EXG instruction exchanges the contents of a pair of registers or accumulators. For

example,

exg

A, B

exg

D,X

exg

A,X

; A ¬ X[7:0], X ¬ $00:[A]

exg

X,B

; X ¬ $00:[B], B ¬ X[7:0]

- The SEX instruction sign-extend an 8-bit two’s complement number into a 16-bit

number so that it can be used in 16-bit signed operations. For example,

SEX A,X

Copyright © 2010 Delmar Cengage Learning

H. Huang Transparency No.1-4

The HCS12/MC9S12 Microcontroller

Move Instructions

- These instructions move data bytes or words from a source to a destination in memory.

- Six combinations of immediate, extended, and index addressing modes are allowed to

specify the source and destination addresses:

IMM EXT,

IMM IDX,

EXT EXT,

EXT IDX,

IDX EXT,

IDX IDX

- For example,

movb

$100,$800

movw 0,X, 0,Y

Table 1.6 Move instructions

Transfer Instructions

Mnemonic

Function

movb <src>, <dest>

movw <src>, <dest>

Move byte (8-bit)

Move word (16-bit)

Copyright © 2010 Delmar Cengage Learning

Operation

dest ¬ [src]

dest ¬ [src]

H. Huang Transparency No.1-5

The HCS12/MC9S12 Microcontroller

Add and Subtract Instructions

- These instructions perform fundamental arithmetic operations.

- The destinations of these instructions are always a CPU register or accumulator.

- There are two-operand and three-operand versions of these instructions.

- Three-operand ADD or SUB instructions always include the C flag as one of the

operand.

- Three-operand ADD or SUB instructions are used to perform multi-precision addition

or subtraction.

- For example,

adda $1000

; A [A] + [$1000]

adca $1000

; A [A] + [$1000] + C

suba $1002

; A [A] - [$1002]

sbca $1000

; A [A] - [$1000] - C

Copyright © 2010 Delmar Cengage Learning

H. Huang Transparency No.1-6

The HCS12/MC9S12 Microcontroller

Table 1.7 Add and subtract instructions

Add Instructions

Mnemonic

aba

abx

aby

adca <opr>

adcb <opr>

adda <opr>

addb <opr>

addd <opr>

Function

Add B to A

Add B to X

Add B to Y

Add with carry to A

Add with carry to B

Add without carry to A

Add without carry to B

Add without carry to D

Operation

A ¬ [A] + [B]

X ¬ [X] + [B]

Y ¬ [Y] + [B]

A ¬ [A] + [opr] + C

B ¬ [B] + [opr] + C

A ¬ [A] + [opr]

B ¬ [B] + [opr]

D ¬ [D] + [opr]

Subtract Instructions

Mnemonic

sba

sbca <opr>

sbcb <opr>

suba <opr>

subb <opr>

subd <opr>

Function

Subtract B from A

Subtract with borrow from A

Subtract with borrow from B

Subtract memory from A

Subtract memory from B

Subtract memory from D

Copyright © 2010 Delmar Cengage Learning

Operation

A ¬ [A] - [B]

A ¬ [A] - [opr] - C

B ¬ [B] - [opr] - C

A ¬ [A] - [opr]

B ¬ [B] - [opr]

D ¬ [D] - [opr]

H. Huang Transparency No.1-7

The HCS12/MC9S12 Microcontroller

*

Example

Write an instruction sequence to add 3 to the memory locations at $10 and $15FA.

Solution:

We have to load the contents of the memory locations to registers, add 3, and write back the

results to the memory locations. (A memory location can’t be a destination of an ADD

instruction)

ldaa $10

; [A][$10]

adda #3

; A[A]+3

staa $10

;[$10][A]

ldaa $15FA

; [A][$15FA]

adda #3

; A[A]+3

staa $15FA

;[$15FA][A]

Copyright © 2010 Delmar Cengage Learning

H. Huang Transparency No.1-8

The HCS12/MC9S12 Microcontroller

Instruction Execution Cycle

- One or more read cycles to fetch instruction opcode bytes and addressing information.

- One or more read cycles to fetch the memory operand(s) (optional).

- Perform the operation specified by the opcode.

- One or more write cycles to write back the result to either a register or a memory location

(optional).

Instruction Queue

- The HCS12 executes one instruction at a time and many instructions take several clock

cycles to complete.

- When the CPU is performing the operation, it does not need to access memory.

- The HCS12 pre-fetches instructions when the CPU is not accessing memory to speedup

the instruction execution process.

- There are two 16-bit queue stages and one 16-bit buffer. Unless buffering is required,

program information is first queued in stage 1, and then advanced to stage 2 for

execution.

Copyright © 2010 Delmar Cengage Learning

H. Huang Transparency No.1-9