Applications of Diodes

advertisement

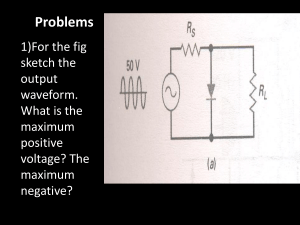

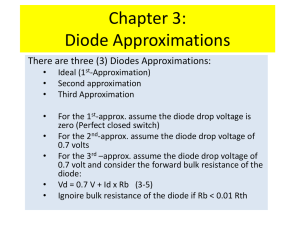

Diode in Digital Logic Design Section 3.1-3.3 Schedule # 1 L Date 1/14 1/14 Day Tuesday Tuesday 2 1/16 Thursday 3 L 1/21 1/21 Tuesday Tuesday 4 5 1/23 1/28 Thursday Tuesday L 6 1/28 1/30 Tuesday Thursday 7 L 8 2/4 2/4 2/6 Tuesday Tuesday Thursday Topic Diagnostic Test Lab protocol, cleaning procedure, Linus/Cadence intro Fundamental concepts from Electric Circuits Basic device physics I-V characteristics of a diode (Simulation) Drift/Diffusion current Physics of PN junction diode Section I-V Curve of a diode Diode models, application of diodes in digital logic,review Test #1 Diode Logic Class Canceled! 2.3 3.1-3.3 (Highlights) 2.1 2.2-2.3 Outline • Review • Diode Model • Applications of Diodes in Digital Logic – OR2 – AND2 Different ways of Crossing PN Junction Diffusion Diffusion np=ni2 Drift Drift Majority carriers cross the pn junction via diffusion (because you have the gradient) Minority carriers cross the pn junction via drift( because you have the E, not the gradient) Reverse Biased Diode Reverse: Connect the + terminal to the n side. Depletion region widens. Therefore, stronger E. E Minority carrier to cross the PN junction easily through drift. Current is composed mostly of drift current contributed by minority carriers. np to the left and pn to the right. Current from n side to p side, the current is negative. Forward Biased Diode Depletion region shrinks due to charges from the battery. The electric field is weaker. Majority carrier can cross via diffusion; Greater diffusion current. Current flows from P side to N side IS=Reverse Saturation=leakage current Diode Models (Ideal model) (Exponential model) (Constant voltage model) Choosing a Diode Model Use the ideal model to develop a quick, rough understanding of a circuit. If the ideal model is not adequate, uses the constant voltage model, which is sufficient for most cases. Occasionally, we will use the exponential model Ideal Model of a Diode (ideal model) (exponential model) An ideal diode will turn on even for the slightest forward bias voltage. (VD≥0) An ideal diode will turn off even for the slightest reverse bias voltage. (VD<0) Behavior of Ideal Diode Ideal diode: Vanode>Vcathode: Diode is on Vanode<Vcathode: Diode is off An ideal current experieincing Vanode=Vcathode, carries no current I/V Characteristics A short--can’t get a An Open—can’t get V to develop across a diode.a current to flow. A diode Vanode>Vcathode: Diode is on Vanode<Vcathode: Diode is off An ideal current experieincing Vanode=Vcathode, carries no current In practice, consider a slightly positive or negative voltage to determine the response of a diode. Example 1: An OR Gate Realized By Diodes “0”=0 V “0”=0 V Assume that “1”=3 V “0”=0 V Assume “ideal” diode Exercise 1: An OR Gate Realized By Diodes “1”=3V “0”=3 V Assume that “1”=3 V “0”=0 V Assume “ideal” diode What is Vout? Exercise 2: An OR Gate Realized By Diodes “1”=3V “1”=3 V Assume that “1”=3 V “0”=0 V Assume “ideal” diode What is Vout? Analysis of an OR Gate Observations: 1. If D1 is on, VA=VOUT and VOUT=“1” 2. If D2 is on, VB=VOUT and VOUT=“1”. 3. VOUT is 0 if and only if D1 and D2 are “0” This is an OR gate. Logic 1=3 V Logic 0=0V Cadence Simulation of an OR Gate VA=3 V VB=3 V VOUT=2.459 V≈3V Cadence Simulation of an OR Gate VA=3 V VB=0 V VOUT=2.424 V≈3V Cadence Simulation of an OR Gate VA=0 V VB=0 V VOUT=0 V Constant Voltage Model If VD is less than VD, On, the diode behaves like an open circuit. The diode will behave like an open circuit for VD=VD,on Cadence Simulation of an OR Gate VA=3 V If we assume a turn on voltage VB=0 V of 0.6 V, we are not off by too VOUT=2.424 V much. Constant voltage model: 3V-0.6V=2.4 V Grid Control Export Image Option File→Export Image In Class Exercise What kind of gate is this? Please assume ideal diode model. Cadence Simulation of an AND Gate VA=3 V VB=3 V VOUT=3 V In Class Exercise Assume that VA=“1”=3V, VB=“0”=0V Please assume constant voltage model. What is the output voltage? Cadence Simulation of an AND Gate VA=3 V VB=0 V VOUT=0.575 V

![Semiconductor Theory and LEDs []](http://s2.studylib.net/store/data/005344282_1-002e940341a06a118163153cc1e4e06f-300x300.png)