Dual-Band CMOS LNA Design for WLAN: Noise & Impedance Matching

advertisement

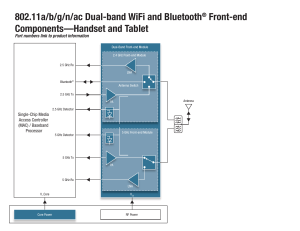

JOURNAL OF SEMICONDUCTOR TECHNOLOGY AND SCIENCE, VOL. 21, NO. 5, OCTOBER, 2021 https://doi.org/10.5573/JSTS.2021.21.5.356 ISSN(Print) 1598-1657 ISSN(Online) 2233-4866 A Concurrent Dual-band CMOS Partial Feedback LNA with Noise and Input Impedance Matching Optimization for Advanced WLAN Applications Dong-Myeong Kim1, Euibong Yang2, and Donggu Im1 Abstract—A concurrent dual-band CMOS partial feedback LNA optimizing noise and input reflection coefficient (S11) at both 2.4 and 5.2 GHz frequency bands is designed using a 65-nm CMOS process for advanced WLAN applications. The inverter-based input transconductance stage directly drives two parallel cascode transistors with 2.4 and 5.2 GHz LC loads, and the output signals splitting into two resonators are combined through a complementary source follower (CSF). Based on an analytical study on the optimum noise impedance (Zopt) and minimum noise figure (NFmin) of the proposed concurrent LNA circuit topology, the concurrent dual-band input matching network is designed in order to achieve low noise figure (NF) around NFmin at both operating frequencies. By employing a partial resistive feedback between 2.4 GHz LC resonator and input transconductance stage through a CSF, an imperfect S11 of the proposed LNA at 2.4 GHz is improved at the expense of a slight increase of NF. In the simulation, the designed LNA achieved forward gain (S21) of 14 and 15.5 dB, NF of 1.6 and 2.2 dB, and S11 of -11.2 and -10.3 dB at 2.4 and 5.2 GHz, respectively. The power consumption of the designed LNA is 7.7 mW from a 1.2 V supply voltage. Manuscript received Aug. 23, 2021; reviewed Sep. 3, 2021; accepted Sep. 8, 2021 1 Division of Electronic Engineering, Jeonbuk National University, Jollabuk-do 561-756, Korea. 2 Samsung Electronics System LSI, 1-1, Samsungjeonja-ro, Hwaseong-si, Gyeonggi-do 474-1, Korea. E-mail : dgim@jbnu.ac.kr Index Terms—CMOS, complementary source follower, concurrent, dual-band, feedback, minimum noise figure, noise figure, noise matching, optimum noise impedance, WLAN I. INTRODUCTION The most recent and interesting evolution of the modern RF transceiver is toward a low-cost single-chip CMOS radio supporting multiband (MB), multimode (MM), and multi-standard (MS). With the explosive growth of WiFi, which is considered to be the most promising wireless technology for the Internet of Things (IoT), the wireless local area network (WLAN) system also requires a highly integrated CMOS transceiver supporting MB/MM with low cost. Many studies have reported single-chip 2.4/5.2 GHz dual-band CMOS transceivers for IEEE 802.11a/b/g WLAN applications [1-3]. Recently, the demand for higher data-rates for the broadband WLAN system has driven a new standard of IEEE 802.11ax to adopt methods to increase the channel bandwidth by concurrent reception and carrier aggregation, and it brings new technical challenges for transceiver design because more signals in intra-bands or inter-bands will be processed simultaneously [4]. Contrast to the conventional receiver architectures where simultaneous reception at two different frequencies can only be performed by building two independent signal paths, the concurrent 2.4/5.2 GHz dual-band receiver architecture of Fig. 1 including this work employs a noncontinuous carrier aggregation technique reported in the long term evolution (LTE) receiver of [5], and as a result, JOURNAL OF SEMICONDUCTOR TECHNOLOGY AND SCIENCE, VOL. 21, NO. 5, OCTOBER, 2021 2.4GHz / 5.2GHz I/Q Mixer IF Filter Image Rejection Mixer LPF VGA I CH#1 1 1 2 2.4G 5.2G I Q fLO1 fLO2 I Q Q I CH#2 Concurrent Dual-Band LNA 2 Q Fig. 1. An architecture for concurrent 2.4/5.2 GHz dual-band receiver employing non-continuous carrier aggregation technique reported in the long term evolution (LTE) receiver of [5]. enables simultaneous operation at two different frequencies without dissipating twice as much power or a significant increase in hardware complexity. However, because the double quadrature image rejection mixer stage for the carrier aggregation causes a higher noise floor in comparison with the conventional low-IF/zero-IF receiver, a low noise LNA with sufficiently high gain at two frequency bands is required for high sensitivity performance. In addition, it is better to provide a good outof-band (OOB) rejection characteristic in order to handle strong interferes. In this paper, a concurrent dual-band CMOS partial feedback LNA is designed for advanced WLAN applications supporting concurrent reception and carrier aggregation. This is the first suggestion of concurrent dual-band LNA optimizing noise and input reflection coefficient (S11) at both 2.4 and 5.2 GHz frequency bands through an input noise matching network and a partial feedback. Section II describes a circuit design of the proposed concurrent dual-band LNA, including an analytical study on its optimum noise impedance (Zopt), minimum noise figure (NFmin), and concurrent input noise matching network. In addition, a partial feedbackbased noise and S11 optimization technique at both 2.4 and 5.2 GHz frequency bands is presented. Section III reports the simulation results of the proposed LNA, followed by the conclusion in Section IV. II. DESIGN OF 2.4/5.2 GHZ CONCURRENT DUAL-BAND LNA There are several LNA design approaches for concurrent reception and carrier aggregation applications, including parallel, concurrent, or wideband LNAs. Parallel LNAs are implemented by placing several 357 individual narrowband LNAs for each band. The out-ofband attenuation characteristic from the input matching network relaxes the linearity burden of the RF front-end, but the complexity and occupied silicon area grow rapidly as the number of frequency bands increases. For the wideband LNA, many standards are supported in a wide frequency range with low complexity and small silicon area. However, its noise performance is much poorer than that in parallel LNAs and the higher linearity is required due to no OOB rejection characteristic. The concurrent LNA is a compromise solution between parallel LNAs and wideband LNA. Many studies have reported concurrent multi-band LNAs in CMOS [6-9]. Most of them adopted an inductively degenerated common-source (CS) topology with concurrent dual-band input matching networks. Unfortunately, all of them consumed a large silicon area due to many on-chip spiral inductors besides an external input matching network and suffered from higher noise figure caused by on-chip source degeneration inductor at higher frequencies. In addition, it is almost impossible to support wideband operation through the reconfiguration of LNA core and board components for customerspecific applications. Fig. 2 shows the schematic of the proposed concurrent dual-band LNA. The inverter-based input transconductance stage (M1n and M1p) directly drives two parallel cascode transistors (M2n) with 2.4 and 5.2 GHz LC loads, and the output signals splitting into two resonators are combined through a complementary source follower 2 (CSF2, M4n and M4p). At this figure, the CSF1 (M3n and M3p) for partial feedback at only 2.4 GHz becomes disabled. The complementary circuit configuration enhances the effective transconductance of the input stage and output buffer by current reuse, and provides more linear feedback operation with low second-order and third-order harmonic distortion in designing a voltage-mode feedback buffer amplifier for the feedback operation [10]. The cascode transistors isolate two LC resonators and greatly reduce the Miller capacitance of the input stage. Because the LNA determines the NF and S11 performance of the whole receiver, the simultaneous noise and input impedance matching (SNIM) technique is highly required for the LNA. It is well known that SNIM is a condition that the input impedance (Zin) and 358 DONG-MYEONG KIM et al : A CONCURRENT DUAL-BAND CMOS PARTIAL FEEDBACK LNA WITH NOISE AND INPUT … Fig. 3. Simplified schematic for calculation of Zopt and NFmin at 2.4 and 5.2 GHz frequency bands. The dominant noise sources of Vn,Rg, In,1n, In,1p, and In,2n are only considered for the calculation. Vn,Rg denotes the noise voltage from the distributed gate resistance (Rg) of M1n and M1p, and In,1n, In,1p, and In,2n are the channel thermal noise current by M1n, M1p, and M2n, respectively. where Rgsh is the sheet resistance of poly gate and Wf, Lf, and Nf denote the finger width, channel length, and number of fingers of the MOSFET, respectively [12]. From [12], Zopt and NFmin of the two-port network in terms of its noise correlation matrix entries C11, C12, C21, and C22 are calculated as Fig. 2. Schematic of the proposed concurrent dual-band LNA. At this figure, the complementary source follower 1 (CSF1) for partial feedback at only 2.4 GHz is disabled. RB (= 100 kΩ) and CB (= 5 pF) denote the high-value resistor for dc bias injection and ac-coupling capacitor, respectively. The channel length of all MOSFETs is 65 nm. (Zopt*) of the amplifier are the conjugated to Zopt simultaneously matched to the source impedance through the matching network [11]. Therefore, firstly, it is important to analyze Zopt, NFmin, and Zin of the proposed LNA of Fig. 2 at both 2.4 and 5.2 GHz frequency bands for the SNIM. 1. Analysis of Optimum Noise Impedance (Zopt) and Minimum Noise Figure (NFmin), and Input Impedance (Zin) Fig. 3 shows the simplified schematic for calculation of Zopt and NFmin at 2.4 and 5.2 GHz frequency bands. Because the noise contribution from the CSF output buffer is small, the dominant noise sources of Vn,Rg, In,1n, In,1p, and In,2n are only considered for the calculation. Vn,Rg denotes the noise voltage from the distributed gate resistance (Rg) of M1n and M1p, and it is given by Vn2,Rg = 4kTRg , where Rg ≈ RgshW f 3L f N f , (1) 1 2 2 ⎡C ⎛ Im ( C12 ) ⎞ ⎤ Im ( C12 ) 1 = Gopt + jBopt = ⎢ 22 − ⎜ ⎟ ⎥ +j Z opt C11 ⎢⎣ C11 ⎝ C11 ⎠ ⎥⎦ NFmin = 1 + 2 ⎡⎣ Re ( C12 ) + ( C11 ⋅ Gopt ) ⎤⎦ , (2) (3) where the matrix entries of the proposed LNA are given by (4), (5), and (6) as functions of channel thermal noise current (In,1n, In,1p, and In,2n), distributed gate resistance (Rg), and Y-parameters of the LNA of Fig. 2 in case of ignoring the induced gate noise of MOSFET. C11 = Rn = Rg + I n2,1n + I n2,1 p + I n2,2 n + I n2,2 n 4kT Y21 2 C21 = C12* = Y11 ⋅ ( Rn − Rg ) C22 = Y11 ⋅ ( Rn − Rg ) . 2 (4) (5) (6) Fig. 4 shows the simulated Zopt, NFmin, and noise circle of the proposed LNA at 2.4 and 5.2 GHz frequency bands on a smith chart. The simulated noise circle was represented by a gradient color scheme. The simulated NFmin at 2.4 and 5.2 GHz are 0.8 and 1.6 dB, respectively, and the NF of the LNA increases by 0.25 dB than NFmin JOURNAL OF SEMICONDUCTOR TECHNOLOGY AND SCIENCE, VOL. 21, NO. 5, OCTOBER, 2021 Zopt_Cal Zopt_Sim 1.0j 0.5j 359 2.0j 0.2j 5.0j 0.2 0.5 1.0 2.0 5.0 -0.2j -5.0j -0.5j -2.0j -1.0j (a) Fig. 4. Simulated Zopt, NFmin, and noise circle (NC) of the proposed LNA at 2.4 and 5.2 GHz frequency bands on a smith chart. The simulated noise circle was represented by a gradient color scheme. The calculated Zopt was marked with a red star for the comparison with the simulation one marked with a blue star. at the outermost noise circle shown in Fig. 4. The calculated Zopt was marked with a red star for the comparison with the simulation one marked with a blue star. From (2) and (3), Zopt and NFmin of the LNA are calculated as 50+j156 Ω and 0.52 dB at 2.4 GHz and 26.5+j52 Ω and 1.55 dB at 5.2 GHz, respectively. The calculated results are well matched to the simulated Zopt and NFmin at both frequency bands. 2. Design of 2.4/5.2 GHz Concurrent Dual-band LNA It is well known that the cascode inductively degenerated CS LNA employing an additional gate-tosource capacitor can match Zin* with Zopt, and as a result, provide the SNIM without the degradation of NFmin at a given single operating frequency for all power dissipation levels. However, unfortunately, it is very difficult to obtain SNIM at concurrent dual-band operating frequencies, and its NF increases abruptly at the frequencies away from Zopt because a large additional gate-to-source capacitor severely decreases the effective cutoff frequency of the input transistor [11]. In Fig. 5, the calculated and simulated complex conjugate of Zin of the proposed LNA at 2.4 and 5.2 GHz are marked with triangle symbol. The proposed LNA shows the inherent mismatch between Zin* with Zopt, and it typically requires compromise between the noise and input impedance matching performance. Considering the mismatch in Zopt directly degrades the NF of the LNA (b) Fig. 5. (a) Calculated and simulated Zopt and complex conjugate of Zin of the proposed LNA at 2.4 and 5.2 GHz frequency bands and the impedance trajectory of Zb which is the impedance looked back to the LNA through the input matching network, (b) designed concurrent dual-band input matching network. and is considered more severe than that in Zin* because some amounts of the mismatch in Zin* are allowed on the LNA performance, it is desirable to make Zb, which is the impedance looked back to the LNA through the input matching network, have an impedance trajectory as close as possible to Zopt at 2.4 and 5.2 GHz frequencies while achieving S11 of less than -10 dB. Fig. 5 shows the designed concurrent dual-band input impedance matching network and simulated impedance trajectory of Zb. The symbol ‘X’ indicates the impedance point of Zb at 2.4 and 5.2 GHz frequencies. In the simulation, the lumped-element spice model for on-board components and bond-wire was used to consider the finite quality factor (Q-factor) and some parasitic elements. As shown in Fig. 5(a) and 6, the impedance trajectory of Zb passes through the midpoint between Zin* with Zopt at 5.2 GHz frequency and as a result the LNA can achieve low NF of 2 dB (around NFmin of 1.6 dB) with S11 of less than -10 dB. It is the best way to make an impedance trajectory of Zb pass through the midpoint between Zin* with Zopt at 2.4 GHz frequency using an identical input matching network, but it requires a large 360 DONG-MYEONG KIM et al : A CONCURRENT DUAL-BAND CMOS PARTIAL FEEDBACK LNA WITH NOISE AND INPUT … 20 NF NFmin S11 15 10 dB 5 0 -5 -10 2 3 4 5 6 Frequency (GHz) Fig. 6. Simulated NFmin, NF, and S11 of the proposed LNA with concurrent dual-band input matching network of Fig. 5(b). Fig. 7. Schematic of the proposed concurrent dual-band partial feedback LNA. At this figure, the complementary source follower 1 (CSF1) for partial feedback at only 2.4 GHz is enabled. The 2.4 GHz feedback path is marked with blue line. 1.0j Matching S11 24/5.2GHz Spot 0.5j Zin*_Sim Zin*_Sim (with PFB) Zopt_Sim Zopt_Sim 0.2j (with PFB) number of on-board components in designing the input matching network. Based on the same input matching network of Fig. 5(b), the LNA achieves low NF of 1.2 dB (around NFmin of 0.8 dB) at 2.4 GHz frequency. However, the S11 performance of the LNA is very poor. The discrepancy between NF and NFmin at both frequencies comes from finite Q-factor of on-board components and bond-wire. 2.0j 5.2GHz 5.0j 2.4GHz 0.2 0.5 1.0 2.0 5.0 -5.0j -0.2j -0.5j Fig. 8. Simulated Zopt and Zin* of the LNA at 2.4 and 5.2 GHz frequency bands with and without partial feedback and the impedance trajectory of Zb through the matching network of Fig. 5(b). PFB means a partial feedback. 1.6 2.4 1.4 2.2 1.2 2.0 dB Fig. 7 shows the proposed concurrent dual-band LNA employing partial feedback to improve poor S11 performance at 2.4 GHz. Compared to the LNA of Fig. 2, the CSF1 for partial feedback at only 2.4 GHz is enabled by closing the switches for dc bias injection. Eventually, the output of 2.4 GHz LC resonator becomes connected to the input of the LNA through CSF1 and feedback resistor RF. As shown in Fig. 8, the partial feedback increases real part of Zin, shifts Zin* with Zopt of the LNA, and makes the impedance trajectory of Zb pass through the midpoint between them at 2.4 GHz frequency, while it causes negligible effects on 5.2 GHz reception. One major drawback is the degradation of NFmin at 2.4 GHz caused by the thermal noise generated from RF, but this will not be an issue in terms of dual-band receiver performance because NFmin at 2.4 GHz is much lower than NFmin at 5.2 GHz and this allows the LNA some degradation of NF at 2.4 GHz frequency. As shown in Fig. 9, the partial feedback degrades NFmin of the LNA by 0.5 dB at 2.4 GHz and by 0.3 dB at 5.2 GHz, respectively. -2.0j -1.0j dB 3. Noise and Input Impedance Matching Optimization Utilizing Partial Feedback 1.0 0.8 0.6 NFmin (with PFB) NFmin 2.2 2.3 2.4 2.5 2.6 Frequency (GHz) 2.7 2.8 NFmin (with PFB) NFmin 1.8 1.6 1.4 4.9 5.0 5.1 5.2 5.3 5.4 5.5 5.6 Frequency (GHz) Fig. 9. Comparison of NFmin of the LNA with and without partial feedback. PFB means a partial feedback. III. SIMULATION RESULTS The proposed LNA was designed using a 65-nm CMOS technology. It consumes a total current of 6.4 mA (excluding output buffer of CSF2) from a 1.2 V supply voltage. Fig. 10 shows the simulated NFmin, NF, forward gain (S21), and S11 of the complete concurrent dual-band LNA employing partial feedback and concurrent dual- 20 10 16 0 12 S21 S11 NF NFmin -10 8 4 -30 0 2 3 4 5 6 7 0 -20 -40 -60 -80 1st Order freq = 2.404G 3rd Order freq = 2.402G -100 -20 1 361 20 Pout(dBm) 20 NF (dB) S11&S21 (dB) JOURNAL OF SEMICONDUCTOR TECHNOLOGY AND SCIENCE, VOL. 21, NO. 5, OCTOBER, 2021 -120 -40 -30 10 12 S11 (dB) 5 8 -5 6 -10 4 -15 2 3 4 5 6 7 -20 -40 -60 -80 10 0 0 1st Order freq = 5.204G 3rd Order freq = 5.202G -100 -40 NF (dB) S11 NF NFmin 2 0 20 Pout(dBm) Fig. 10. Simulated NFmin, NF, forward gain (S21), and S11 of the proposed concurrent dual-band LNA employing partial feedback and concurrent dual-band input matching network of Fig. 5(b). 1 -10 (a) Frequency (GHz) -20 -20 Pin(dBm) -30 -20 -10 0 Pin(dBm) (b) Fig. 12. Simulated third-order input-referred intercept point (IIP3) of the complete LNA at (a) 2.4 GHz, (b) 5.2 GHz. 0 Frequency (GHz) Fig. 11. NFmin, NF, and S11 of the proposed concurrent dualband LNA with and without the partial feedback. The blank and solid symbols denote the simulation results with and without the partial feedback respectively. band input matching network of Fig. 5(b). As predicted, S11 of less than -10 dB is achieved at both 2.4 and 5.2 GHz frequencies. The simulated NF of the complete LNA at 2.4 and 5.2 GHz frequencies are 1.6 and 2.2 dB, respectively, and both of them are near around NFmin. In case of S21, the LNA shows a forward gain of greater than 14 dB at both frequencies. Fig. 11 presents the simulated NFmin, NF, and S11 of the proposed concurrent dual-band LNA with and without the partial feedback. The input impedance matching at dual frequency bands can be achieved through the partial feedback with nearly the same NF. Fig. 12(a) and (b) show the simulated third-order input-referred intercept point (IIP3) of the complete LNA at 2.4 and 5.2 GHz frequencies. Two-tone test was performed at both frequency bands in the simulation, and the tone spacing was 2 MHz. The simulated IIP3 of the complete LNA at 2.4 and 5.2 GHz frequencies are -3.7 and -9.3 dBm, respectively. Table 1 summarizes and compares the performance of the proposed concurrent dual-band LNA against other previous works. Due to a partial feedback-based noise and S11 optimization technique at both 2.4 and 5.2 GHz frequencies, the proposed concurrent dual-band LNA shows lower NF near around NFmin compared to other previous works while showing comparable linearity and power dissipation. To compare the performances of the LNAs, the figure-of-merit (FoM) is defined by [13] FoM = Freq[GHz] ⋅ Gain[abs] ⋅ IIP3[mW] . (NF[abs]-1) ⋅ PDC [mW] (7) IV. CONCLUSIONS The concurrent dual-band CMOS LNA optimizing noise and S11 at both 2.4 and 5.2 GHz frequencies through an input noise matching network and a partial feedback was firstly demonstrated through the simulation for advanced WLAN applications. The proposed LNA 362 DONG-MYEONG KIM et al : A CONCURRENT DUAL-BAND CMOS PARTIAL FEEDBACK LNA WITH NOISE AND INPUT … Table 1. Performance Summary and Comparison *[6] **[7] **[8] *[9] Frequency (GHz) 2.4 / 5.2 2.45 / 6 2.4 / 5.2 2.4 / 5.2 *This Work 2.4 / 5.2 S21 (dB) 21.0 / 12.5 9.4 / 18.9 12.9 / 8.2 19.3 / 17.5 14.0 / 15.5 NF (dB) 2.5 / 2.4 2.8 / 3.8 3.7 / 3.7 3.2 / 3.3 1.6 / 2.2 S11 (dB) -12.7 / -17.4 -12.6 / -21.0 -13.1 / -10.5 -16.8 / -19.4 -11.2 / -10.3 IIP3 (dBm) N/A -4.3 / -5.6 -4.0 / -1.0 -20.1 / -18.1 -3.7 / -9.3 Power Consumption (mW) 10 @ 1.8 V 2.8 @ 1.2 V 7.6 @ 1.0 V 2.4 @ 1.2 V 7.7 @ 1.2 V Process Technology (CMOS) 180-nm 130-nm 180-nm 130-nm 65-nm FoM N/A 3.1 / 32.8 1.8 / 2.7 0.8 / 1.7 7.5 / 4.3 * Simulation results, ** Measurement results achieved low NF (near around NFmin) with sufficiently high gain and good input impedance matching performance at both frequencies while supporting various modes of narrowband, concurrent dual-band, and wideband easily through hardware reconfigurability. [3] ACKNOWLEDGMENTS This paper was supported by research funds of Jeonbuk National University in 2021. This work was also supported by the National Research Foundation of Korea (NRF) grant funded by the Korea government(MSIT)(No. 2021R1A4A1032234), Korea and by the Institute of Information and Communications Technology Promotion (IITP) grant funded by the Korea government (MSIT) under Grant 2018-0-01461. The circuit simulation and EDA tool were supported by the IC Design Education Center (IDEC), Korea. REFERENCES [1] [2] M. Zargari, M. Terrovitis, S. H. -M. Jen, B. J. Kaczynski, MeeLan Lee, M. P. Mack, S. S. Mehta, S. Mendis, K. Onodera, H. Samavati, W. W. Si, K. Singh, A. Tabatabaei, D. Weber, D. K. Su, and B. A. Wooley, “A single-chip dual-band tri-mode CMOS transceiver for IEEE 802.11a/b/g wireless LAN,” IEEE J. Solid-State Circuits, vol. 39, no. 12, pp. 2239-2249, Dec. 2004. T. Maeda, N. Matsuno, S. Hori, T. Yamase, T. Tokairin, K. Yanagisawa, H. Yano, R. Walkington, K. Numata, N. Yoshida, Y. Takahashi, and H. Hida, “A low-power dual-band triple-mode WLAN [4] [5] [6] [7] [8] CMOS transceiver,” IEEE J. Solid-State Circuits, vol. 41, no. 11, pp. 2481-2490, Nov. 2006. S. Gross, T. Maimon, F. Cossoy, M. Ruberto, G. Normatov, A. Rivkind, N. Telzhensky, R. Banin, O. Ashckenazi, A. Ben-Bassat, S. Zaguri, G. Hara, M. Zajac, N. shahar, S. Shahaf, H. Yousef, E. Mor, Y. Eliat, A. Nazimov, Z. Beer, A. Fridman, and O. Degani, “Dual-band CMOS transceiver with highly integrated front-end for 450Mb/s 802.11 n systems,” in Proc. IEEE RFIC, Anaheim, CA, USA, May. 2010, pp. 431-434. X. Yi, K. Yang, Z. Liang, B. Liu, K. Devrishi, C.C. Boon, C. Li, G. Feng, D. Regev, S. Shilo, F. Meng, H. Liu, J. Sun, G. Hu, and Y. Miao, “A 65nm CMOS carrier-aggregation transceiver for IEEE 802.11 WLAN applications,” in Proc. IEEE RFIC, San Francisco, CA, USA, May. 2016, pp. 67-70. S. Hwu, and B. Razavi, “An RF receiver for intraband carrier aggregation,” IEEE J. Solid-State Circuits, vol. 50, no. 4, pp. 946-961, April. 2006. E. Kargaran, and B. Madadi, “Design of a novel dual-band concurrent CMOS LNA with current reuse topology,” in Proc. IEEE ICNIT, Manila, Philippines, June. 2010, pp. 386-388. N. Neihart, J. Brown, and X. Yu, “A dual-band 2.45/6 GHz CMOS LNA utilizing a dual-resonant transformer-based matching network,” IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 59, no. 8, pp. 1743-1751, Aug. 2012. Y. H, S. Wang, P. Chen, Y. Hwang, and J. Chen, “A concurrent dual-band 2.4/5.2 GHz low-noise amplifier using gain enhanced techniques,” in Proc. IEEE APEMC, Taipei, Taiwan, May. 2015, pp. 231-234. JOURNAL OF SEMICONDUCTOR TECHNOLOGY AND SCIENCE, VOL. 21, NO. 5, OCTOBER, 2021 [9] S. Sattar, and T. Zulkifli, “A 2.4/5.2-GHz Concurrent Dual-Band CMOS Low Noise Amplifier,” IEEE Access, vol. 5, pp. 21148-21156, Sept. 2017. [10] D. Im, “A +9-dBm output P1 dB active feedback CMOS wideband LNA for SAW-less receivers,” IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 60, no. 7, pp. 377-381, Jul. 2013. [11] T. Nguyen, C. Kim, and G. Ihm, “CMOS low-noise amplifier design optimization techniques,” IEEE Trans. Microw. Theory Techn., vol. 54, no. 7, pp. 3155-3156, July. 2006. [12] S. Asgaran, M. Deen, C. Chen, G. Rezvani, Y. Kamali, and Y. Kiyota, “Analytical Determination of MOSFET's High-Frequency Noise Parameters From NF50 Measurements and Its Application in RFIC Design,” IEEE J. Solid-State Circuits, vol. 42, no. 5, pp. 1034-1043, May. 2007. [13] A. Taibi, A. Slimane, M. T. Belaroussi, S. A. Tedjini, and M. Trabelsi, “Low power and high linear reconfigurable CMOS LNA for multistandard wireless applications,” in Proc. IEEE ICM, Beirut, Lebanon, Dec. 2013. Dongmyeong Kim received the B.S. and M.S. degrees in division of electronic engineering from the Jeonbuk National University (JBNU), Jeonju, Korea, in 2019, and 2021, respectively. He is currently working toward the Ph.D. degree in division of electronic engineering at JBNU. His research during Ph.D. course has focused on highly linear sub-1dB NF low noise amplifiers (LNAs) and reconfigurable power amplifiers (PAs) in CMOS. 363 Euibong Yang received the B.S. degree in electronic engineering from the Jeonbuk National University (JBNU), Jeonju, South Korea, in 2016, and the M.S. degree in electrical engineering and computer science from the Gwangju Institute of Science and Technology (GIST), Gwangju, Korea, in 2018. In 2018, he joined Samsung Electronics Co., Ltd., Hwaseong, South Korea, where he is currently Engineer. His current research interests include the field of RF and analog circuit designs including design and analysis of cellular RFIC. Donggu Im received the B.S., M.S., and Ph.D. degrees in electrical engineering and computer science from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, Korea, in 2004, 2006, and 2012, respectively. From 2006 to 2009, he was an Associate Research Engineer with LG Electronics, Seoul, Korea, where he was involved in the development of universal analog and digital TV receiver ICs. From 2012 to 2013, he was a Post-Doctoral Researcher with KAIST, where he was involved in the development of the first RF SOI CMOS technology in Korea with SOI business team in National NanoFab Center (NNFC), Daejeon, Korea. In 2013, he joined the Texas Analog Center of Excellence (TxACE), Department of Electrical Engineering, University of Texas at Dallas, as a Research Associate, where he developed ultra-low-power CMOS radios with adaptive impedance tuning circuits. In 2014, he joined the Division of Electronic Engineering, Jeonbuk National University, Jeollabuk-do, Korea, and is now an Associate Professor. His research interests are CMOS analog/RF/ mm-wave ICs and system design.