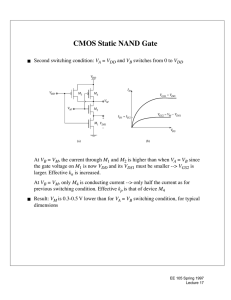

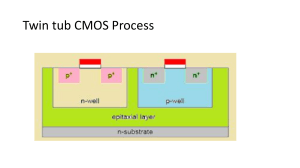

Introduction to Digital System Design Module 1-D Logic Signals and CMOS Logic Circuits © 2020, Rick. All Rights Reserved. Redistribution Prohibited. Reading Assignment: DDPP 4th Ed. pp. 79-96, 141-148; 5th Ed. pp. 8-25, 790-796 DDSwSV Chapter 5, Gates Learning Objective: Define the switching threshold of a logic gate and identify the voltage ranges typically associated with a “logic high” and a “logic low” ● Define assertion level and describe the difference between a positive logic convention and a negative logic convention ● Describe the operation of basic logic gates (NOT, NAND, NOR) constructed using N- and P-channel MOSFETs and draw their circuit diagrams ● Define “fighting” among gate outputs wired together and describe its consequence ● Define logic gate fan-in and describe the basis for its practical limit ● 2 Outline: ● Logic signals and assertion levels ● CMOS logic circuits ● Inverter (NOT) ● NAND ● NOR ● Fighting ● Fan-in 3 Logic Signals ● A logic value, 0 or 1, is often referred to as a binary digit or bit ● The words “LOW” and “HIGH” are often used in place of “0” and “1” to refer to logic signals – LOW - a signal in the range of “lower” voltages (e.g., 0 - 1.5 volts for 5V CMOS logic), which is interpreted as a logic 0 5V Logic Levels 5.0 3.5 1.5 – HIGH - a signal in the range of “higher” voltages (e.g., 3.5 - 5.0 volts for 5V CMOS logic), which is interpreted as a logic 1 0.0 100% HIGH undefined, indeterminate ???? LOW 70% 30% 0% 4 Using Different Voltages ● 5V was the typical power supply voltage level of digital logic systems for decades. ● Modern systems no longer run at 5V. ● 3.3V is becoming more typical, so that is what we will use for ECE 270 (and ECE 362). ● The interpreted logic levels are based on a rule of thumb of 30% and 70% of VDD. 5 Logic Signals Using Different Voltages ● When using different voltages for logic chips, the percent rule stays the same: 5V Logic Levels 5.0 3.5 1.5 0.0 100% HIGH undefined, indeterminate ???? LOW 70% 30% 0% 3.3V Logic Levels 1.8V Logic Levels 3.3 1.8 2.3 1.0 0.0 100% HIGH undefined, indeterminate ???? LOW 70% 30% 0% 1.25 0.54 0.0 100% HIGH undefined, indeterminate ???? LOW 70% 30% 0% 6 Positive Logic Convention ● The assignment of 0 and 1 to LOW and HIGH, respectively, is referred to as a positive logic convention (or simply “positive logic”) – a positive logic signal that is asserted is in the HIGH state, and is therefore referred to as an “active high” signal – a positive logic signal that is negated is in the LOW state 7 Negative Logic Convention ● The opposite assignment (1 to LOW and 0 to HIGH) is referred to as a negative logic convention (or “negative logic”) – a negative logic signal that is asserted is in the LOW state, and is therefore referred to as an “active low” signal – a negative logic signal that is negated is in the HIGH state 8 Active low? ● You know what an inverter is. ● You might say: – The input of an inverter is active high. – The output of an inverter is active low. – When the inverter is “active”, the output is low. ● That’s not quite how we use the terms “active high” and “active low”, but it might help you understand. 9 Logic Families ● There are many ways to design a digital logic gate, from mechanical relays and vacuum tubes to microscopic transistors ● Complementary Metal-Oxide Semiconductor (CMOS) circuits – Called “complementary” because we put N- and P-channel MOSFETs on the same chip. – Now account for the vast majority of the worldwide Integrated Circuit (IC) market ● CMOS logic is both the most capable and the easiest to understand commercial digital logic technology 10 CMOS Logic ● Based on MOSFETs – Recall: this is a 3-terminal device that acts as a voltage-controlled resistance: VS VG VD – In digital logic applications, MOSFETs are operated so that their resistance is either very high (transistor is “off”) or very low (transistor is “on”). 11 N- and P-Channel MOSFETs ● In a P-Channel MOSFET: – Current only flows from S to D – A decrease in VGS → decrease in RDS. ● RDS is large when VGS = 0. ● RDS is small when VGS < 0. VGS + Source Current flow Gate Drain ● In an N-Channel MOSFET: – Current only flows from D to S – An increase in VGS → decrease in RDS. ● ● RDS is large when VGS = 0. RDS is small when VGS > 0. Drain Gate + VGS Current flow - Source 12 Two Complementary MOSFETs together ● As voltage on A goes VDD (+3.3V) S A B P-channel G D Current flow VOUT ● As voltage on B goes D G N-channel S VSS (Gnd) from 3.3V to 0V, the Pchannel MOSFET switches “on”. Current flow from 0V to 3.3V, the Nchannel MOSFET switches “on”. 13 “On” and “off” resistance ● Suppose resistances of each VDD (+3.3V) S A B P-channel G D MOSFET are: Current flow “on”: 75Ω ● “off”: 500,000Ω ● VOUT – N-Channel: D G – P-Channel: N-channel S VSS (Gnd) “on”: 25Ω ● “off”: 500,000Ω ● Current flow ● Voltage at V OUT is a voltage divider. 14 Example: Both transistors “on” ● Suppose A is low, and B is high: VDD (+3.3V) S 0V A G D 3.3V B P-channel – P-Channel RDS = “on”: 75Ω Current flow ● Voltage at V is: 3.3V * 25 / (25 + 75) = 0.825V VOUT OUT ● Total current flow is: D G – N-Channel RDS = “on”: 25Ω N-channel S VSS (Gnd) Current flow I = V/R = 3.3/(25+75) = 0.033A ● Total power is: P = V*I = 3.3 * 0.033 = 109mW 15 Example: Both transistors “off” ● Suppose A is high, and B is low: VDD (+3.3V) S P-channel 3.3V G A D 0V B – P-Channel RDS = “off”: .5MΩ Current flow ● Voltage at V is: 3.3V * .5 / (.5 + .5) = 1.65V VOUT OUT ● Total current flow is: D G – N-Channel RDS = “off”: .5MΩ N-channel S VSS (Gnd) Current flow I = V/R = 3.3/(.5 + .5) = 3.3μAA ● Total power is: P = V*I = 3.3 * 3.3μAA = 11μAW 16 Wire Both MOSFET Gates Together ● So far, the MOSFETs have resulted in a voltage divider with “interesting” values. ● When the MOSFET gates terminals are wired together, we see something useful. 17 Wire MOSFET gates together... ● When MOSFETs are VDD (+3.3V) S P-channel G D VIN Current flow VOUT wired together in this configuration, only one will be switched “on” at a time. D G N-channel S VSS (Gnd) Current flow 18 When VIN is high... ● Suppose V VDD (+3.3V) S 3.3V P-channel G D VIN Current flow is high: – P-Channel RDS = “off”: .5MΩ – N-Channel RDS = “on”: 25Ω ● Voltage at V is: 3.3V * 25 / (500025) = ~0V VOUT OUT ● Total current flow is: D G IN N-channel S VSS (Gnd) Current flow I = V/R = 3.3/(.5) = 6.7μAA ● Total power is: P = V*I = 3.3 * 6.7μAA = 22μAW 19 When VIN is low... ● Suppose V VDD (+3.3V) S 0V P-channel G D VIN is low: – P-Channel RDS = “on”: 75Ω Current flow – N-Channel RDS = “off”: .5MΩ ● Voltage at V is: 3.3V * 500000 / (500075) = ~3.3V VOUT OUT ● Total current flow is: D G IN N-channel S VSS (Gnd) Current flow I = V/R = 3.3/(.5) = 6.7μAA ● Total power is: P = V*I = 3.3 * 6.7μAA = 22μAW 20 This device is called an “inverter” ● Same thing as this VDD (+3.3V) S P-channel G D VIN Current flow VOUT ● This is the simplest logic D G symbol: N-channel S VSS (Gnd) Current flow gate to construct ● Now you know what it is made of. 21 Digital Logic Outputs: Push-Pull ● It is important to remember that normal digital outputs are always either high or low. – When an output is “low” it does not mean it is electrically disconnected or undriven. – A “high” output will “push” current out. (source) – A “low” output will “pull” current in. (sink) ● Such an output is a push-pull driver. 22 Primary Current Flows Through “on” MOSFET ● We can largely ignore VDD (+3.3V) S P-channel G 0V D VIN Current flow VOUT the “off” transistor current, and connect an external load. D G “off” N-channel 150Ω S VSS (Gnd) 23 Primary Current Flows Through “on” MOSFET ● We can largely ignore VDD (+3.3V) S G 3.3V P-channel “off” D VIN 150Ω VOUT the “off” transistor current, and connect an external load. D G N-channel S VSS (Gnd) Current flow 24 Simplified MOSFET Diagrams ● In practice, we use diagrams for MOSFETs that are simpler to draw by hand. S G G D D D G S S G From a logical standpoint, a P-channel MOSFET is a device that switches “on” when the gate voltage is “low”. That’s why we represent it with an inversion bubble on the gate. D S 25 Simplified inverter diagram VDD (+3.3V) Current flow VIN VOUT As long as we remember which direction the current must flow through a MOSFET, it’s common practice to omit the Gate, Source, and Drain labels too. Current flow VSS (Gnd) 26 Basic CMOS NAND Gate Pull-up “OR” G VDD S D Q1 G S D Q2 Z A G D Q3 S B G D S Consider the truth table: A B Q1 Q2 Q3 Q4 Z L L on on off off H L H on off off on H H L off on on off H H H off off on on L Q4 VSS Pull-down “AND” 27 Basic CMOS NOR Gate Pull-up “AND” A G VDD S D B G S D G D S Q1 Q2 Q3 VSS Z G Consider the truth table: A B Q1 Q2 Q3 Q4 Z L L on on off off H L H on off off on L H L off on on off L H H off off on on L D Q4 S Pull-down “OR” 28 Fan-in limitations ● Definition: The number of inputs a gate can have in a particular logic family is called the logic family’s fan-in ● CMOS gates with more than two inputs can be obtained by extending the “series-parallel” circuit designs (e.g., for NAND and NOR gates) illustrated previously ● In practice, the additive “on” resistance of series transistors limits the fan-in of CMOS gates to a relatively small number ● Gates with a large number of inputs can be made faster and smaller by cascading gates with fewer inputs 29 3-input CMOS NAND Gate VDD G S D G S D G S D Z A G D S B G D S C G The length of this chain of MOSFETs is the limiting factor for the number of inputs to the gate. D S VSS 30 Two Inverting Gates Make a Non-Inverting Gate ● To make a non-inverting gate, add an inverter to a “natural” CMOS gate. VDD G S G D S D A Z G D S G D S VSS 31 Why not have non-inverting gates? ● CMOS circuits can make inverting functions (NOT,NAND,NOR) easily. Non-inverting functions (AND,OR) cannot be realized as succinctly. – Sometimes clever, well-meaning students propose things like this for a non- inverting buffer, but it does not work well: G D S G S D If you’re curious why this does not work, remember that each MOSFET is switched on by VGS, but S is connected to the output, and we cannot know what its voltage will be. Both MOSFETs will be partially ON no matter what the input is. 32 A CMOS AND Gate = ● An AND gate is VDD G S D A G G S D G D S S D Z D S B G G D S a NAND gate with an inverter connected to its output. ● (And an OR gate is a NOR-NOT combination.) VSS 33 Remember: Outputs are “Push-Pull” ● An “OR” function is not produced by wiring two digital signals together. E.g.: F=(A*B)’ + (C*D)’ A The NAND gate outputs will either push high or pull low. B F C D If the NAND outputs don’t agree, the voltage level of F will be somewhere in between VDD and VSS. 34 Remember: Outputs are “Push-Pull” ● An “OR” function is not produced by wiring two digital signals together. E.g.: F=(A*B)’ + (C*D)’ P-Channel on resistance: 75Ω N-Channel on resistance: 25Ω high A low B F F voltage = VDD * 50 / (125) ??? high C high D 35