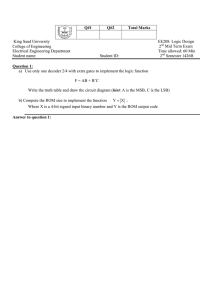

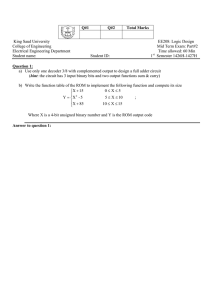

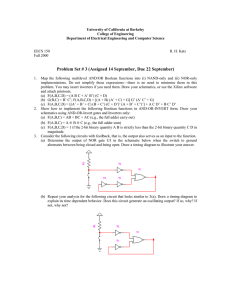

Examples for : Ex. Using PROM realize the following expressions. F1 (a, b, c) = ∑ m (0, 1, 3, 5, 7) F2 (a, b, c) = ∑ m (1, 2, 5, 6) Sol. : The given functions have three inputs. They generate 23 = 8 minterms and since there are two functions, there are two outputs. The functions can be realized as shown in Fig. 9.2.11. shows the block diagram and truth table of PROM. Design a combinational using a PROM. The circuit accepts 3-bit binary number and generates its equivalent Excess-3 code. Sol. : Let us derive the truth table for the given combination circuit. Table shows the truth table. • In practice when we are designing combinational circuits with PROM, it is not necessary to show the internal gate connections of fuses inside the unit, as shown in the Fig. This was shown for demonstration purpose only. The designer has to only specify the PROM (inputs and outputs) and its truth table, as shown in the Fig. 9.2.14. Design a combinational circuit using ROM. The circuit accepts 3-bit number and generates an output binary number equal to square of input number. Sol. PLA (Programmable Logic Array) PLA is similar to a PROM in concept; however it does not provide full decoding of the variables and does not generates all the minterms as in the PROM. The PLA replaces decoder by group of AND gates, each of which can be programmed to generate a product term of the input variables. In PLA, both AND and OR gates have fuses at the inputs, therefore in PLA both AND and OR gates are programmable. Fig. shows the block diagram of PLA. It consists of n-inputs, output buffer with m outputs, m product terms, m sum terms, input and output buffers. The product terms constitute a group of m AND gates and the sum terms constitute a group of m OR gates, called OR matrix. Fuses are inserted between all n-inputs and their complement values to each of the AND gates. Fuses are also provided between the outputs of the AND gates and the inputs of the OR gates. The third set of fuses in the output inverters allows the output function to be generated either in the AND-OR form or in the AND-OR-INVERT form. When inverter is bypassed by link we get AND-OR implementation. To get AND-OR-INVERTER implementation inverter link has to be disconnected. 1. Input Buffer • Input buffers are provided in the PLA to limit loading of the sources that drive the inputs. They also provide inverted and non-inverted form of inputs at its output. The Fig. 9.3.2 shows two ways of representing input buffer for single input. 2. Output Buffer The driving capacity of PLA is increased by providing buffers at the output. They are usually 1 IL compatible. The Fig. 9.3.3 shows the tri-state, 1 IL compatible output buffer. The output buffer may provide totem-pole, open collector or tri-state output. 3. Output through Flip-Flops For the implementation of sequential circuits we need memory elements, flip-flops and combinational circuitry for deriving the flip-flop inputs. To satisfy both the needs some PLAs are provided with flip-flop at each output, as shown in the Fig. 4. Implementation of Combination Circuit using PLA • Like ROM, PLA can be mask-programmable or field-programmable. With a maskprogrammable PLA, the user must submit a PLA program table to the manufacturer. This table is used by the vendor to produce a user-made PLA that has the required internal paths between inputs and outputs. A second type of PLA available is called a field-programmable logic array or FPLA. The FPLA can be programmed by the user by means of certain recommended procedures. FPLAs can be programmed with commercially available programmer units. • As mentioned earlier, user has to submit PLA program table to the manufacturers to get the user-made PLA. Let us study how to determine PLA program table with the help of example Examples for Understanding Ex. A combinational circuit is defined by the functions : F1 = ∑ m (3,5,7), F2 = ∑ m (4,5,7) Implement the circuit with a PLA having 3 inputs, 3 product terms and two outputs. Solution : Step 1 : Simplify the given Boolean functions The Boolean functions are simplified, as shown in the Fig. 9.3.5. The simplified functions in sum of products are obtained from the maps are : Step 2 : Write PLA program table Therefore, there are three distinct product terms : AC, BC and AB, and two sum terms. The PLA program table shown in Table consists of three columns specifying product terms, inputs and outputs. The first column gives the lists of product terms numerically. The second column specifies the required paths between inputs and AND gates. The third column specifies the required paths between the AND gates and the OR gates. Under each output variable, we write a T (for true) if the output inverter is to be bypassed, and C (for complement) if the function is to be complemented with the output inverter. The product terms listed on the left of first column are not the part of PLA program table they are included for reference only Step 3 : Implementation Ex. Draw a PLA circuit to implement the logic functions Sol. : Step 1 : Simplify the Boolean functions Note : The second Boolean function is in simplified form. Step 2 : Implementation Ex. Implement the following multiboolean function using 3 × 4 × 2 PLA PLD. f1 (a2, a1, a0 ) = ∑ m (0, 1, 3, 5) and f2 (a2, a1, a0 ) = ∑ m (3, 5, 7) Sol. : Step 1 : Simplify the Boolean functions. To implement functions fj. and f2 we require 3 x 5 x 2 PLA and we have to implement them using 3x4x2 PLA. Therefore, we have to examine product terms by grouping Os instead of 1. That is product terms for complement of a function. Step 2 : Implementation Looking at function outputs we can realize that product terms are common in both functions. Therefore, we need only 4 product terms and functions can be implemented using a 3 × 4 × 2 PLA as shown in Table 9.3.2 and Fig. 9.3.10. As shown in the Fig. exclusive-OR gate is programmed to invert the function to get the desired function outputs. PLA Table: Design a BCD to Excess-3 code converter and implement using suitable PLA. Sol. : Step 1 : Derive the truth table of BCD to Excess-3 converter Step 2 : Simplify the Boolean functions for Excess-3 code Step 3 : Write PLA program table Step 4 : Implementation What is Programmable Array Logic (PAL)? Programmable Array Logic (PAL) is a type of device which comes from the class of programmable logic devices (PLDs) and is used to implement combinational circuits. The basic configuration of a PAL consists of a programmable AND array and followed by a fixed OR gate. It differs from PLA in a manner, that PAL consists of an AND array followed by a fixed OR array whereas in case of PLA it has an AND array followed by a programmable OR gate. In PAL, since only AND array is programmable it is easier to use but it is not that flexible. A schematic diagram of the basic configuration of PAL can be drawn as: Programmable Array Logic (PAL) Examples Example 1 Implement the following Boolean expression using PAL, F1= ∑ m (3,5,7) and F2 = ∑ m (4,5,7). Solution Since, F1= ∑ m (3,5,7) and F2 = ∑ m (4,5,7). Truth table for Boolean functions F1 and F2 can be drawn as: Now, for these Boolean functions, using the K-Map we can find the simplified Boolean expressions as: A PAL program table can be also drawn representing the terms in the Boolean expression as: The logic diagram of the combinational circuit implemented using PAL can be drawn as: Example 2 Implement the following Boolean expressions using a suitable PLA. A (x,y,z) = ∑ m (1,2,4,6) B (x,y,z) = ∑ m (0,1,6,7) C (x,y,z) = ∑ m (2,6) D (x,y,z) = ∑ m (1,2,3,5,7) Solution Truth table for Boolean functions A, B, C and D can be drawn as: Solving K-Map to get the required Boolean expressions: A PLA program table can be also drawn representing the terms in the Boolean expression as: The logic diagram of the combinational circuit implemented using PLA can be drawn as: Comparison between PROM, PLA and PAL Memory is a set of registers that holds instructions and data for processing. Data inside these memory units are stored in the form of binary data. There are mainly two kinds of memory that are used in Digital Systems which are named RAM (Random Access Memory) and ROM (Read Only Memory). The memory inside Digital Systems can be classified as: 1.Read-Only Memory (ROM) ROM is used only for performing Read operation. ROM is a non-volatile memory i.e., the information stored on the memory will not get erased even after power is turned off. That's why we have permanent programs (e.g.: Operating System programs) in ROM. Therefore, ROM is called as program memory. Block Diagram of ROM The block diagram of ROM can be drawn as: For ROM data lines are always output lines because it performs only Read operation. Chip Select (CS) or Memory Enable (MEN) input is used to select a ROM IC. If CS=0, n-data lines will be in a high impedance state. Types of Read-Only Memory (ROM) 1. Simple ROM and Masked ROM Earlier, simple ROMs were made using the diodes. A simple Diode ROM consists of only diodes and a decoder as shown in below fig. A 2:4 decoder is used to decode address lines A0 and A1 and it selects one of the four rows. Since the nature of the output of the decoder is active low, it places logic 0 on the selected row. When the diode connects the output data column to the selected row, then each data output line goes to logic 0. When the output-enable (OE) signal is lowDa, then data gets available on the output data lines. In the present scenario, ROMs are built using MOS technology instead of using diodes. Some significant changes have been made like diodes and pull up resistors are replaced by MOS transistors. Just like in simple ROMs, A0 and A1 are decoded using 2:4 decoders, and the decoder selects one of the four rows making it logic 0. The not gate which is connected to the output of the decoder inverts the state of the selected row (i.e., from logic 0 to logic 1). Hence, when the gate of the MOS transistor is connected to the row select line, each output data line goes to logic 0. The MOS transistor is turned on when the gate of the MOS transistor is connected to the selected rows. This causes the corresponding column data line to go to logic 0. The masked ROM has its storage locations written into (programmed) by the manufacturer according to the requirements of the customer. Masked ROMs are used in Microprocessor-based toys, TV games, personal computers, etc. 2. Programmable Read-Only Memory (PROM) (or) Field PROM The PROM chip comes 'blank' and can be programmed only once by a user. Above fig. shows 4-byte PROM. It has diodes in every bit position, therefore, the output is initially all 0's. Each diode inside the circuit has a fusible link connected in series with it. The fuse can be blown out by addressing the bit and applying proper current pulse at the corresponding output, hence, storing logic 1 at that bit position. The PROMs are one time programmable. Once programmed, the information stored is permanent. 3. Erasable Programmable Read-Only Memory (EPROM) EPROMs use MOS circuitry. 0s and 1s are stored as a packet of charge inside a buried layer of the IC chip. EPROM chips can be erased and rewritten a no. of times. Stored data in the EPROM can be erased by exposing the chip to ultraviolet light through its quartz window for 15 to 20 minutes (before erasing the data we have to remove the IC from its socket.) In EPROM, we cannot erase selective information; once something gets erased the entire information is lost. The chip can be reprogrammed. EPROM is ideally suitable for products and college laboratories since this chip can be reused many times. In EPROM, it is possible to program any location at any time, either individually, sequentially, or at random. 4. Electrically Erasable Programmable Read-Only Memory (EEPROM) EEPROM is like EPROM except that the previously programmed connections can be erased with an electrical signal instead of ultraviolet light. The advantage of EEPROM over EPROM is that the device can be erased without removing it from the socket. Random Access Memory (RAM) RAM is called "Random Access Memory" because through it any storage location can be accessed directly. RAM belongs to the class of volatile memory which means if the power supplied to the system goes OFF, then data stored inside the RAM will get lost, that is why RAM is generally used to store only temporary data. Hence, RAM is also known as data memory. Memory Write operation can be defined as the process of storing new information into memory. Memory Read operation can be defined as the process of transferring the stored information out of memory. A RAM is capable of performing both Read and Write operations that is why it is also called Read/Write Block Diagram of RAM The block diagram of a RAM can be drawn as: In the above figure, the size of RAM is 2K * N, it means RAM consists of 2K memory locations and each memory location has a size of n-bits.The communication between memory and other devices can be achieved through data lines. Each data line carries one bit of binary information. Data lines are bidirectional in nature, but at any time they act as either input or output lines.During memory write operation data lines act as input lines.An address line carries the desired memory location address for memory read or writes operation. Read / Write is a control signal. It is used to select either Read or Write operation. If Read / Write =0, then RAM performs write operation. RAM enables or performs either read or write operation only when its Chip Select (CS) or Memory Enable (MEN) input is high. If CS=0, then RAM is disabled. Types of Random Access Memory (RAM) There are two types of Random Access Memory (RAM). They are: Static Random-Access Memory (SRAM): SRAM consists of flip-flops to store binary information. Dynamic Random-Access Memory (DRAM): DRAM consists of CMOS transistors and capacitors. It stored the binary information in the form of electric charges on capacitors. Memory Read Operation: The memory read operation steps are: Step 1: Apply the binary address of the desired word to the address lines. Step 2: Activate the read input. The memory unit then takes the bits from the word that already has been selected by the address and all of them are then applied to the output data lines. Hence, the content of the selected word doesn't change after the reading process is completed. Memory read cycle timing diagram can be drawn as: Access Time: It is the memory device operating speed. It is defined as the time required to perform the read (or) write operation. Memory Write Operation The memory write operation steps are: Step 1: Apply the binary address of the desired word to the address lines. Step 2: Apply the data bits that must be stored in memory to the data input lines. Step 3: Activate the write input. The memory unit then takes the bits from the input data lines and stores them in the words which are specified by the address lines. Memory write cycle timing diagram can be drawn as: