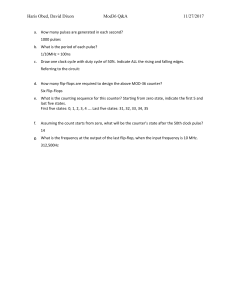

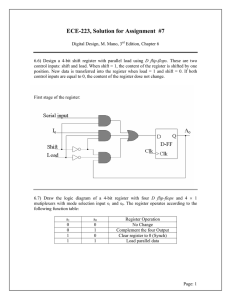

Registers and Counters Slide 1 Registers • Group of Flip-Flop, each one of which shares a common clock and is capable of storing 1 bit of information. • An n-bit register consists of a group of n flip-flops, capable of storing n bits of information. • In addition to flip-flops, the register may also contain combinational gates that performs certain data-processing tasks. Combinational gates n-Flip-Flops How the informatio is transferred into the registers Holds the Binary Information Counter • Special type of registers that goes though predetermined sequence of binary states. • Gates enables the predescribed sequence of states. Combinational gates n-Flip-Flops Control the predetermine sequence of binary states Holds the Binary Information Register • 4-bit register • Example: A simplest register with only flip-flops, and without any gates. • clock Triggers the flip-flop on rising edge, and data from input is transferred to the output. • clear_b: When 0 applied, all the flip-flops in registers are reset. Slide 4 Register • 4-bit register with Load control: • Fundamental building block in digital systems. • The transfer of new-information into a register is referred to as loading/updating the register. • The loading process must be controlled in digital system to determine, which register to be loaded when. • The contents of the register must be left unchanged, untill the desired needs are fulfilled. Slide 5 Register • 4-bit register with Load control: • To retain the Loaded information in the register, it can be controlled in two ways: 1. Controlling the Clock 2. Controlling the D input of the register • Clock controlling is an ill practice. e.g., In the given sequential logic, the Load=0, would disable the clock to a particular register. • When enabling the clock through a logic gate would produce delays, that could effect the synchronization Register • 4-bit register with Load control: • To fully synchronize the system, we must trigger all the flipflops simultanously; i.e., ensure that all the clock pulses arrive at the same time anywhere in the system without any delay. • Control the operation of register With the D inputs rather than controlling clock input. • Use two channel MUX at D input • MUX for Load C ontrol: • Implementation of the MUX: Registers: • 4-bit register with Load: Load = 0 • The Flip-flop outputs data toward the input is enabled. Hence register retains its previous data. Load =1 • The feedback is disabled and the input bus is enabled, this allows the register to be loaded from the data coming on input BUS. Slide 8 Shift Registers: A register capable of shifting the binary information held in each cell to its neighboring cell, in a selected direction, is called a shift register. • 4-bit Shift Register: • Shifting is unidirectional. o Possible from left-to-right, but not from right-to-left. Slide 9 Shift Registers: • Serial Transfer: • The Datapath of a digital system is said to operate in serial mode when information is transferred and manipulated one bit at a time. o One bit from one register is serially shifted to the other register. Slide 10 Register to Register Serial Transfer: • Serial Transfer: • Content of registers: Slide 11 Serial Addition: • Serial adder circuit diagram (Using D Flip-Flop): Slide 12 Serial Addition: JK FF IMplementation • FF input equations: (with K-MAP) 𝐽𝑄 = 𝑥𝑦 𝐾𝑄 = 𝑥′𝑦′ = (𝑥 + 𝑦)′ • The output equation: 𝑆=𝑥⨁𝑦⨁𝑄 Slide 13 Serial Addition: JK FF Implementation • Serial adder circuit diagram (Using J-K Flip-Flop): Slide 14 Universal Shift Register • A Universal SR can: – Remain unchanged, – Load serially and shift right, – Load serially and shift left, – Load in parallel. • We need 4 control signals (2 control bits): Slide 15 Universal Shift Register • The circuit for Universal shift Register: o A clear control: to clear the register to 0. o A clock input: to synchronize the operations. o Bidirectional control: to enable the shift‐right and shift‐left operation. o A parallel‐load control: to enable a parallel transfer with n output lines. o A control state: that leaves the information in the register unchanged in response to the clock. Slide 16 Universal Shift Register • The circuit for Universal shift Register: Slide 17 Counters: • A counter is a register that changes in a certain order. • Examples: – A binary counter c ounts from 0 to 2𝑛 -1. – A BCD counter counts from 0 to 9 (0000 to 1001). • There are two types of counters: – Ripple counters – Sync hronous c ounters • In a ripple counter, the output of one flip-flop has effect on the next state of the following flip-flop. • In a synchronous counter, state changes are dictated by a common clock. Slide 18 Binary Ripple Counter: with T FF LSB • A 4-bit ripple counter: The output of each flip‐flop is connected to the C input of the next flip‐flop in sequence. • T inputs = 1; making each flip‐ flop complement if the signal in its C input goes through a negative transition. • Every time that A1 goes from 1 to 0, it complements A2. Every time that A2 goes from 1 to 0, it complements A3, and so on. MSB Slide 19 Binary Ripple Counter: with D FF LSB • A 4-bit ripple counter with D FFs: D flip‐flop with the complement output connected to the D input. • The output of each flip‐flop is connected to the C input of the next flip‐flop in sequence. MSB Slide 20 BCD Ripple Counter: • State Diagram of a BCD Ripple Counter: Homework Slide 21 Synchronous Counters: • State Diagram of a Synchronous Binary Counter: • The C inputs of all flip‐flops are connected to a common clock. • The counter is enabled by Count_enable. If the enable input is 0, all J and K inputs are equal to 0 and the clock does not change the state of the counter. Clock 𝑨𝟑 𝑨𝟐 𝑨𝟏 𝑨𝟎 1 0001 2 0010 3 0011 . . . . 15 1111 Slide 22 Up-Down counters: • A 4-bit up/down c ounter: Up Down Output 0 0 Previous count 1 0 Up- Counting 0 1 Down-Counting 1 1 Up-Counting Slide 23 Synchronous BCD counter: • State transition table of a 4-bit up/down counter: Slide 24 Synchronous BCD counter: • Example: K-map for 𝑇2: FF Input Equations: 𝑇1 = 1, 𝑇2 = 𝑄8 ′ 𝑄1, 𝑇4 = 𝑄2𝑄1 𝑇8 = 𝑄8𝑄1 + 𝑄4𝑄2𝑄1 and the output equation: 𝑦 = 𝑄8𝑄1. Slide 25 Synchronous BCD counter: • The c irc uit for a BCD Counter with TFlip-flops: Slide 26 Counters with Parallel Load: • Binary Counter with Parallel Load: Slide 27 Counters with Parallel Load: • Binary Counter with Parallel Load: Slide 28 Counters with Unused States: • Binary Counter with n flip-flops can have 2𝑛 states. • We may not need all these states. • We have already seen the example of BCD counter that uses only 10 out of 24 = 16 possible states. • We can treat the unused states: – as don’t care condition or – some specific next states. Since, • Example: consider a counter following the sequence 000, 001, 010, 100, 101, 110. That is, the counter skips 011 and 111. Slide 29 Counters with Unused States: • Example: consider a counter following the sequence 000, 001, 010, 100, 101, 110. That is, the counter skips 011 and 111. • The state table for this counter is: • We have 𝐽𝐴 = 𝐾𝐴 = 𝐵, 𝐽𝐵 = 𝐶, 𝐾𝐵 = 1, 𝐽𝐶 = 𝐵′, and 𝐾𝐶 = 1. Slide 30 Counters with Unused States: • The circuit diagram is: State Diagram: Slide 31 Ring Counter: • • • • A Ring Counter counts: 1000, 0100, 0010, 0001, 1000, … At any time only one FF is on. It can be used to control a sequence of repetitive operations. A Ring Counter can be implemented by connecting the output of a shift register to its input. • Two FF implementation: Slide 32 Johnson Counter: • Schematic of switch-tail Ring Counter: • A Johnson counter is a switch tail ring with outputs (or inverted outputs) of flip-flops combined (by AND) to form 2k timing signals. • The rule for forming AND gate inputs is straightforward: – For all zero pattern the inverted outputs of the first and last flip- flop are used. – For all one pattern the regular outputs of the extreme flip-flops are used. – For other patterns, the first two alternating bits, either 01 or 10 are used. Slide 33 Johnson Counter: • The count sequence for the 4-bit tail-switch ring counter: • So, in this example: we use 𝐴′𝐸′ for 0000, 𝐴𝐸 for 1111, 𝐴𝐵′ for 1000, 𝐵𝐶′ for1100. Similarly 𝐴′𝐵 for 0111 and 𝐵′𝐶 for 0011 and so on. • When Johnson counter goes to an unused state, it goes from one invalid state to another. • To avoid this, we must use a good combinational logic to correct this. e.g., we may disconnect the output of 𝐵 flip-flop from the input 𝐷 of 𝐶 flip-flop and instead feed 𝐶 flip-flop with 𝐷𝐶 = (𝐴 + 𝐶)𝐵. Slide 34