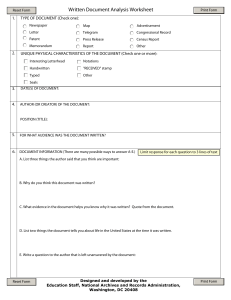

John Oscar Albasin ENGR271 Homework 2 1. Given: Four schematic diagrams are given in the problem. Find: Identify the ambiguities of each state diagram. Solution: To define an ambiguity in a state diagram, first we want to know if the input diagram combination must be equal to 1 and when it is double covered, the product the pair of that transition must be 1 also. a. X Y Current State Next State 0 0 B ? 0 1 B ? 1 0 B ? 0 0 C ? 0 1 C ? 1 0 C ? 0 0 D ? 1 0 D ? b. For this part, all the state A,B,C and D are ambiguous. For A state, it is missing another transition that that product would result in 1. For B state, at the sequence of 12,13,14 and 15 it covers both state B and A. For C state, at sequence 5,7,10,12,13,4 and 15 it covers both A, C and D. For D state, there are some sequences that doesn’t have any output such as at sequence 2 where the output is unknown. W X Y Z Current State Next State 0 0 0 1 A ? 0 0 1 1 A ? 1 0 1 1 A ? 1 1 0 0 B B&A 1 1 0 1 B B&A 1 1 1 0 B B&A 1 1 1 1 B B&A 0 0 1 0 C A&D 0 0 1 1 C C&D 0 1 0 0 C A&D 1 1 0 0 C A, C & D 1 1 0 1 C A, C & D 1 1 1 0 C A, C & D 1 1 1 1 C A, C & D 1 0 0 1 D A&B 1 0 1 1 D A&B c. X Y Z Current State Next State 0 0 0 A ? 0 0 1 A ? 0 1 0 B A&C 1 0 0 B B&D 1 1 0 B B&D 1 1 0 D B&D 1 1 1 D B&D W X Y Z Current State Next State 0 0 0 0 A A&D 1 0 0 0 A C&D 0 0 0 0 B B&C 0 1 0 0 B A&C 0 0 0 0 C B&C 0 0 0 1 C B&D 0 0 0 0 D A&D 0 0 1 0 D A&D d. 2. Given: - A sequence that counts starts from: 4, 5, 6 … 13, 14, 4. - Modulo 11 Find: Design a modulo 11 counters using the above sequence and use an IC 74163N. Solution: A modulo 11 counter counts from 4-14 and then goes back to 4 and counts again to 14. Since the count will start at 4, so I am going to input into that IC. VCC 3 4 5 6 A B C D QA QB QC QD 14 13 12 11 7 10 ENP ENT RCO 15 9 1 ~LOAD ~CLR 2 CLK 74163N I am going to enable ENP and ENT to have a consistent counting and increasing count. For the output I am going to use a NAND gate and one will be inverted which is the least significant bit and that when 14 comes in the counting which , it will load a zero and that will reset the counting back to 4. VCC VCC U3 2Hz 3 4 5 6 A B C D QA QB QC QD 14 13 12 11 7 10 ENP ENT RCO 15 9 1 ~LOAD ~CLR 2 CLK 74LS163N 0101 3. Given: A pattern is given in a series of binary 0110110. Find: Draw a state diagram for this mealy circuit. Solution: So, I am going to draw the state diagram of this series of binaries. This state diagram has an I/O in the transition when the current state transit to another state. First, I am going to draw a state bubble that doesn’t have any value yet. After that, I’m going to do the transition of the state of getting 0110110. The pattern will be 0110110 and that will continue to loop as it is. At the unknown state bubble, if In/Out is 0/0, it will transit to the next state bubble but it is 0/1 then it will go back to itself. In the transition, each of the inputs corresponds to the next state and will output a value of 1. If the inputs of the corresponding states are opposite to its valid transition value, then it will loop itself or it will go back to the previous state. I would say this is now the mealy machine state diagram. 4. Given: - Two state variables, Q1 and Q2. State assignments A=00, B=01, C=11, D=10. Find: - Design a state machine given above and use NAND gates and DFFs. Write an excitation equation. Solution: First, I am going to design a state diagram based on the transition/excitation table. So now I have the state diagram, next is I am going to create a transition table from that. diagram. 𝑸𝟐 0 0 0 0 1 1 1 1 𝑸𝟏 𝑋 𝑸∗𝟐 𝑸∗𝟏 Z 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 1 0 0 1 0 0 1 0 1 1 1 1 1 0 0 0 0 0 0 0 1 1 Next, I am going to create a Boolean expression from the future state and the Z using KMaps from Boolean solver tool online. Also note that the future state will be D input since this will determine what output will future state be. 𝐷2 = 𝑄2∗ = ̅̅̅ 𝑄1 𝑋 + ̅𝑄̅̅2̅ 𝑄1 𝑋̅ 𝐷1 = 𝑄1∗ = 𝑋̅ + 𝑄2 ⊕ 𝑄1 𝑍 = 𝑄1 𝑄2 Now that I have the expression, I am going to design a state machine using NAND and DFFs. I will be using 2 DFF since there are 2 input Q1 and Q2. X 1 X 1 SET 1 RESET X X Z SET SET Q2 Q1 SET SET D Q D Q CLK ~Q CLK ~Q RESET RESET U1 1kHz RESET RESET 5. Given: A state diagram is given in the problem. Find: Design a clocked synchronous FSM using DFFs and include transition table, Kmaps, and a schematic with the decoding logic. Solution: First, I’m going to do a transition table for this biquinary state diagram. Current State Future State Biquinary Code 𝑸𝟑 𝑸𝟐 𝑸𝟏 𝑸𝟎 𝑫𝟑 𝑫𝟐 𝑫𝟏 𝑫𝟎 𝑩𝟔 𝑩𝟓 𝑩𝟒 𝑩𝟑 𝑩𝟐 𝑩𝟏 𝑩𝟎 0 0 0 0 0 0 0 1 0 1 0 0 0 0 1 0 0 0 1 0 0 1 0 0 1 0 0 0 1 0 0 0 1 0 0 0 1 1 0 1 0 0 1 0 0 0 0 1 1 0 1 0 0 0 1 0 1 0 0 0 0 1 0 0 1 0 0 0 0 1 1 0 0 0 1 0 1 0 1 x x x x x x x x x x x 0 1 1 0 x x x x x x x x x x x 0 1 1 1 x x x x x 1 0 0 0 1 0 0 1 1 x 0 x 0 x 0 x 0 x 0 x 1 1 0 0 1 1 0 1 0 1 0 0 0 0 1 0 1 0 1 0 1 0 1 1 1 0 0 0 1 0 0 1 0 1 1 1 1 0 0 1 0 0 1 0 0 0 1 1 0 0 0 0 0 0 1 0 1 0 0 0 0 1 1 0 1 x x x x x x x x x x x 1 1 1 0 x x x x x x x x x x x 1 1 1 1 x x x x x x x x x x x After creating the transition table, I am going to create a Kmap for the output D and the output for the biquinary. 𝑫𝟑 𝑸𝟑 𝑸𝟐 𝑫𝟐 𝑸𝟏 𝑸𝟎 00 01 11 10 00 01 1 1 𝑫𝟏 𝑸𝟑 𝑸𝟐 00 01 11 00 11 10 𝑸𝟑 𝑸𝟐 𝑸𝟏 𝑸𝟎 1 x x x 01 x x x x x x 11 x x x 1 1 1 10 01 1 𝑫𝟎 𝑸𝟏 𝑸𝟎 00 10 11 𝑸𝟏 𝑸𝟎 10 𝑸𝟑 𝑸𝟐 00 1 00 1 01 11 10 1 00 1 01 x x x 01 x x x 11 x x x 11 x x x 10 1 1 10 Boolean expression for output D: 𝐷3 = 𝑄3 ⊕ 𝑄2 𝐷2 = 𝑄1 𝑄0 𝐷1 = 𝑄1 ⊕ 𝑄0 𝐷0 = ̅𝑄̅̅2̅ ̅𝑄̅̅0̅ 1 1 Output for the Biquinary. 𝑩𝟔 𝑸𝟑 𝑸𝟐 𝑩𝟓 𝑸𝟏 𝑸𝟎 00 01 11 10 00 01 x x x 11 x x x 1 1 1 10 1 𝑩𝟒 𝑸𝟑 𝑸𝟐 01 11 𝑸𝟑 𝑸𝟐 00 01 11 10 00 1 1 1 1 01 x x x 11 x x x 10 𝑩𝟑 𝑸𝟏 𝑸𝟎 00 𝑸𝟏 𝑸𝟎 10 00 𝑸𝟑 𝑸𝟐 𝑸𝟏 𝑸𝟎 00 01 00 11 10 1 01 1 x x x 01 x x x 11 1 x x x 11 x x x 10 10 1 𝑩𝟐 𝑸𝟏 𝑸𝟎 𝑸𝟑 𝑸𝟐 00 01 𝑩𝟏 11 10 00 𝑸𝟑 𝑸𝟐 𝑸𝟏 𝑸𝟎 00 01 1 00 1 11 10 01 x x x 01 x x x 11 x x x 11 x x x 1 10 1 10 𝑩𝟎 𝑸𝟑 𝑸𝟐 𝑸𝟏 𝑸𝟎 00 01 11 10 01 1 x x x 11 1 x x x 00 10 After getting the KMaps, I am going to create a Boolean expression and from that I am going to design a DFFs schematic with a decoding output. 𝑩𝟔 = 𝑸𝟑 ̅̅̅̅ 𝑸𝟐 𝑩𝟓 = ̅̅̅̅ 𝑸𝟑 ̅̅̅̅ 𝑸𝟐 𝑩𝟒 = 𝑸𝟐 𝑩𝟑 = 𝑸𝟏 𝑸𝟎 𝑩𝟐 = 𝑸𝟏 ̅̅̅̅ 𝑸𝟎 𝑩𝟏 = ̅̅̅̅ 𝑸𝟏 𝑸𝟎 𝑩𝟎 = ̅̅̅̅ 𝑸𝟐 ̅̅̅̅ 𝑸𝟏 ̅̅̅̅ 𝑸𝟎 For output D, this is the flip flop that I am going to wire and for the out B’s are the decoding logic. Q2 Q3 Q0 Q1 Q1 Q0 Q2 SET Q0 0 RESET 0 SET SET SET Q3 SET D CLK Q1 SET Q D ~Q CLK RESET Q0 SET Q D ~Q CLK RESET RESET U12 SET Q2 SET Q D ~Q CLK RESET RESET Q2 B6 Q3 B5 Q2 Q2 Q1 Q0 Q1 Q0 Q0 Q1 Q0 Q1 Q2 B4 B3 B2 B1 B0 ~Q RESET RESET RESET 1Hz Q3 Q B6 B5 B4 B3 B2 B1 B0 0 1 0 0 1 0 0