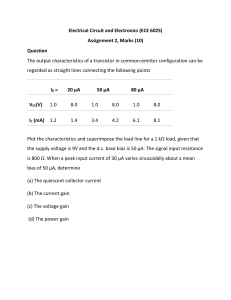

CMOS Analog Design Using All-Region MOSFET Modeling ( PDFDrive )

advertisement