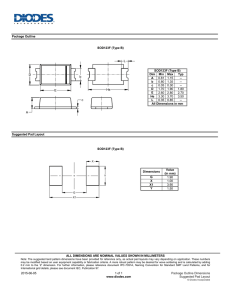

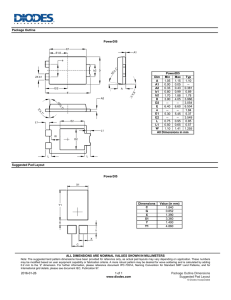

Cadence Design Systems, Inc. Power Routing Calculation 1 Power calculation Power routing calculations has to be done for determine ring and stripe widths needed for the implementation. To better understanding of calculation an example has been taken as below to show how the calculation of power grid can be done. • Input for power calculation The power network is mainly dependent on the process technology so from the technology DRM (Design rule Manufacture) EM (Electro Migration) Line Current Limits (High Density Backend) (Tj = 125C) has been taken out as below Metal Level M1 (Metal1) M2 (Metal2) M3 (Metal3) M4 (Metal4) M5 (Metal5) M6 (Metal6) M7 (Metal7) Idc (mA) 0.759 * (W - 0.02) 1.007 * (W - 0.02) 1.007 * (W - 0.02) 1.007 * (W - 0.02) 1.007 * (W - 0.02) 2.904 * (W - 0.02) 2.904 * (W - 0.02) Where, W is width of one pad finger. CMOS90 spec indicates 110mA @125oc max continuous DC current per power pad • How to do the power calculation Total Estimated core power : 4W Core supply voltage : 1.1v-1.2-v-1.3v Operating temperature : 125oc P=IV therefore current is : 4/1.1=3.64A (909mA per side) (1.1v is used to get the worst case scenario) No of VDD pads : 24 (# of VDD pads decided from package) Current per pad : 3.64/24 = 151mA Exceeds power pad, finger spec, ring mesh width need recalculation CMOS90 spec indicates 110mA @125oc max continuous DC current per power pad • Pad Design o Pad has 8x fingers which are available for connection into core o Layer M4 to M7 is available for connection with 3.36um wide pin with 1.68um spacing Below figure shows the structure of the pad. 2 Finger of pad • Calculating the Current through pad tracks Now we have to calculate the max current we can pass through the pad tracks so that we can decide how to use the different metal layer Current pre length*((width of finger-edge effect loss)*No. of fingers connected Thin Metal (M4-M5) @125oc = 1.007*((3.36-0.02)*8) =26.9*2 layers=53.9mA ** 53.9mA current is calculated if we use both M4-M5 layers overlapping with each other Thick Metal (M6-M7) @125oc = 2.904*((3.36-0.02)*8) =77.5*2 layers=155.1mA ** 155.18mA current is calculated if we use both M6-M7 layers overlapping with each other CMOS90 spec indicates 110mA @125oc max continuous DC current. So above configuration cannot be used. Since the above combination won’t work with the specification so to achieve the max mA in ring from pad through fingers if ring M6 vertical and M7 horizontal. Horizontal connection using preferred routing direction would achieve current both VDD and VSS connection possible Thick (M7) + Thin (M5) fingers = 77.59+ 26.90= 104.5mA Vertical connection using preferred routing direction would achieve current both VDD and VSS connection possible Thick (M6) + Thin (M4) fingers = 77.59+26.90=104.5mA 3 • Calculating the density of Metal stripes M7 core mesh - VDD/VSS 5.22um wide 6.72um pitch – straps in 100x100um 14.881*5.22=77.69% (38.84%per supply) M6 core mesh - VDD/VSS 4.4um wide 12.32um pitch – straps in 100x100um 8.116*4.4=35.71% (17.85% per supply) M5 core mesh - VDD/VSS 1.5um wide 13.44um pitch – straps in 100x100um 7.44*1.5=11.16% (5.58%per supply) M4 core mesh - VDD/VSS 1.5um wide 24.64um pitch – straps in 100x100um 4.061*1.5um=6.092% (3%per supply) M1 std rows - VDD/VSS 1.2um wide 3.92um pitch – 25 rows in 100x100um 25*1.2um=30% (15%per supply) • Calculating the ring width using current per pad distributed calculation For Horizontal Ring: Pad Current: 104mA Current through M7 straps = (2.904 * (5.22 – 0.02) * 4) = 60.4032mA Current through ring = 104 – 60.4032 = 43.5968mA Current in (left or right) ring branch = 43.5968/2 = 21.7984mA Certain width (W7) of ring has to drive this current, 21.7984 = 2.904* (W7– 0.02) W7 = 7.526um (this is for single M7 segment either VSS or VDD) ~7.56um (to make it multiple of 0.28, pitch of lower most H Layer M1) For Vertical Ring: Pad Current: 104mA Current through M6 straps = (2.904 * (4.4 – 0.02) * 2) = 25.43904mA Current through ring = 104 – 25.43904 = 78.56096mA Current in ring branch = 78.56096/2 = 39.28mA Certain width (W6) of ring has to drive this current, 39.28 = 2.904* (W6 – 0.02) W6 = 13.54um (this is for single M6 segment either VSS or VDD) ~13.44um (to make it multiple of 0.28, pitch of lower most V Layer M1) It is recommended that once power structure has been created then user should run a signoff analysis tool such as EPS to verify the power grids meeting the IR drop and EM requirements. 4