ECS502U - Microprocessor Systems Design Topic 6: Basic Interfacing Lecturer: Chris Phillips School of Electronic Engineering & Computer Science Basic Interfacing – TTL Logic Transistor-Transistor-Logic (TTL) interfaces are common Current Level Voltage Low Below 0.9V Virtually zero current flow High Above 2.4V 1.6mA sinking current from TTL input to ground (depends on logic family) Normally TTL inputs “float” HIGH though, due to the reduced noise immunity, it is better to tie them high through an external resistor (i.e. 10K ohms) if unused Unlike CMOS logic gates, TTL devices are less prone to “zapping” due to the use of internal clamping diodes, however, this is not necessarily true of some newer TTL-like logic families 2 Driving Light Emitting Diodes from TTL Most standard LEDs have a forward voltage drop of 1.7 – 2.5V, so how do we drive such an LED from our output port? • Circuit A: will perform poorly due to the fact that the TTL output can't source above a few hundred µA, meaning that the LED will be very dim • Circuit B: will work better as the output can sink a much higher current, however, the LED will conduct heavily at about 2V and the extra 3V will be dropped in the port circuitry, causing high power dissipation • Circuit C: the resistor limits the current allowing the port to safely drive the LED (if the LED drops 2.3V and the port output is at 0.5V then the current will be limited to 2.2/260 = 8.5mA, which should be ok but you should always check the data sheet) A B C +5v R +5v R 3 8051 P1, P2 and P3 Port Structure Writing a ‘1’ to an 8051 port pin causes the internal D-type flip-flop to latch a ‘1’ into the Q output. As Q’ is LOW the transistor TR1 is switched OFF Whatever voltage appears at the port pin is then transferred to TB1. The internal load is a weak pull-up that does not interfere with the reading operation Vcc Vcc Read Latch Internal CPU Bus TB2 ‘1’ D Q Write to Latch Clk Q’ Read Pin TB1 Internal Load Port Pin TR1 ‘0’ 4 8051 P1, P2 and P3 Port Structure Writing a ‘0’ to an 8051 port pin causes the internal D-type flip-flop to latch a ‘0’ into the Q output. As Q’ is HIGH the transistor TR1 is switched ON When TR1 is ON it provides a low resistance path to ground for the internal load and any signal on the port pin. If the port pin is connected to Vcc then an excessive current will flow through TR1 and DESTROY it! Read Latch Internal CPU Bus Write to Latch Read Pin Vcc TB2 ‘0’ D Q Clk Q’ Vcc Internal Load Port Pin TR1 ‘1’ TB1 5 Simple Switches 8051 I/O Pin A 8051 I/O Pin Vcc Circuit A: When switch is pressed I/O pin reads as ‘0’, else it reads as ‘1’. If pullup not present, then input would float when switch is not pressed, and input value may read as ‘0’ or ‘1’ because of system noise ? Circuit B: is ok (?) except that it requires the pull-down resistor to be very small otherwise the pin will rise above 0.9V when the resistor passes the sinking current, also this circuit will waste a large current when the switch is closed since virtually no current flows into the pin 8051 I/O Pin Vcc R B Vcc 8051 I/O Pin R 6 Matrix Keypad This section examines how simple matrix-type keypads may be scanned with a microcontroller. De-bouncing and interrupt-driven operations are also considered Matrix-type keypads consist of a rectangular array of momentary pushbuttons. Each row and each column of pushbuttons is connected to a common rail A four-by-four array is often used to input hexadecimal numbers. There are four column rails and four row rails. Each pushbutton has two terminals, one connected to its column rail and the other to its row rail The row and column rails are connected to the microcontroller ports. The columns are driven low by output ports. The rows are then read into the input ports 7 Matrix Keypad If no key is pressed, the rows read 1. When a row is detected to be 0, it indicates that a key in that row is pressed The task now is to detect which key of the row is actually pressed. The microcontroller loops through each column, driving only one column low at a time as it inspects the row The microcontroller needs to poll the rows to see if a key is pressed. Only when the column in which the pressed key resides is driven low is the row rail grounded, and thus the voltage is low The rows and columns are interchangeable, that is, the rows may be driven low as the columns are read by the input ports 8 Columns Matrix Keypad Rows Connections with microcontroller • Columns driven low “0000” and Row values read • If Rows read = “1111” then no keys pressed – inputs float high • If any Row reads = “0” then a key has been pressed • Microcontroller drives one Column “0” at a time while reading the Rows • When column containing pressed Key is “0” the Row output is “0” 9 ECS502U Matrix Keypad 8051 P3.5 Port 3 P3.4 P3.3 P3.2 8255A A0 A1 RD’ WR’ Segment* e Digit* b g c d h Port B Port CU Port 1* * P1.0 equates to D0 and so on f a Port A Row Column D0-7 Display Port CL CS’ GND R0 R1 R2 R3 C0 C1 C2 C3 Keypad * Port A bit 0 equates to segment “a” and so on * Port B bit 0 equates to the right-most digit and so on 10 ECS502U Matrix Keypad Code Example with Interrupt Initially the microcontroller writes to the Status/CR register of the 8255A to configure its ports appropriately – i.e. Port A output, Port B output and Port C upper output and Port C lower input. Enable external interrupt. The main routine is then needed to refresh the display and the interrupt routine is called when a key is pressed. Main Routine - repeat forever, for all digits: • Read segment value from register (such as R0-3) • Set P1 to 8255 Port A by writing to 8255 Control Register • Write segment value from P1 to Port A • Set P1 to 8255 Port B by writing to 8255 Control Register • Enable appropriate digit by writing to Port B • Delay • Clear displayed character before moving on Interrupt Service Routine: • Check source of interrupt and continue as follows if external • Set P1 to 8255 Port C by writing to 8255 Control Register • Write scanning pattern to CU and read CL to determine key pressed • Based on identified key – take appropriate action • Finish interrupt routine with RETI to clear interrupt flag 11 ECS502U Matrix Keypad R0 R1 R2 R3 Rows Columns C3 C2 C1 C0 Connections with microcontroller • Rows driven high “1111” and Column values read • If Column reads = “0000” then no keys pressed – inputs pulled low • If any Column reads = “1” then a key has been pressed • Microcontroller drives one Row “1” at a time while reading the Columns • When Row containing pressed Key is “1” the Column output is “1” 12 Interrupt Driven Matrix Keypad The keypad may be implemented to invoke an interrupt, thus reducing the load on the CPU. The interrupt should be invoked whenever a key is pressed. Typically, the rows are combined into an AND gate When no key is pressed, all rows are at level 1; thus the AND gate produces a 1. Whenever a key is pressed, one of the rows becomes 0. This action also causes the output of the AND gate to be 0 A 1-to-0 transition at the output of the AND gate indicates that a key has just been pressed. This signal may be used as the external interrupt of the microcontroller. With this arrangement, the CPU detects key-press actions in an interrupt service routine, called only upon the event of a key press 13 Matrix Keypad with Interrupt Support Using AND gates an active LOW interrupt can be triggered when any key is pressed, causing an Interrupt Service Routine to scan the keypad 14 Matrix Keypad De-Bounce Many pushbuttons, when pressed, make a series of contacts and breaks before a solid contact is established. These pulses are due to the mechanical motion of the two conductors engaging to make the final contact These pulses are short in duration and appear as spikes on an oscilloscope. However, since microcontrollers are fast, there is a possibility that a single key press is registered as a few separate key presses, as the key bounces. A de-bouncing scheme is needed De-bouncing may be accomplished in hardware or in software. The simplest software de-bouncing routine is a short delay loop to wait out the pulses 15 Schmitt Trigger A schmitt trigger is a special kind of comparator circuit. A Schmitt trigger changes its output state when its input voltage level rises above a certain reference voltage; however, the output does not switch back automatically when the input voltage level sinks again unless a second, lower reference voltage is crossed A standard op-amp comparator simply outputs the highest voltage it can, when the positive input is at a higher voltage than the negative, and then switches to the lowest output voltage it can, when the positive input drops below the negative Schmitt triggers use hysteresis to guard against noise that would otherwise cause rapid switching back and forth between the two output states, when the inputs are close to the threshold 16 Seven-Segment Display One common requirement of many different digital devices is a visual numeric display. Individual LEDs can display the binary states of a set of latches or flip-flops. However, humans prefer dealing with decimal numbers. To this end, we want a display that can represent decimal numbers One possibility is a matrix of 28 LEDs in a 7×4 array. We can then light up selected LEDs in the pattern required for whatever character we want. However, if all we want to display is numbers, this becomes expensive. A cheaper way is to arrange the minimum possible number of LEDs in such a way as to represent numbers in a simple fashion This requires just seven LEDs (plus an eighth one for the decimal point, if needed). A common technique is to use a shaped piece of translucent plastic to distribute the light from the LED evenly over a fixed bar shape. The bars are laid out as a squared-off figure "8“ creating a seven-segment LED 17 Seven-Segment Display The illustration shows the basic layout of the segments in a seven-segment display. The segments themselves are identified with lower-case letters "a" through "g," with segment "a" at the top and then counting clockwise. Segment "g" is the centre bar. Most seven-segment digits also include a decimal point ("dp") In addition, most displays are slanted a bit, making them look as if they were in italics. This arrangement allows us to turn one digit upside down and place it next to another, so that the two decimal points look like a colon between the two digits. The technique is commonly used in clock displays Seven-segment displays can be made using different technologies. The three most common methods are fluorescent displays, Liquid Crystal Displays (LCDs), and Light Emitting Diode (LED) displays 18 Seven-Segment Display The LEDs in a seven-segment display are not isolated from each other. Rather, either all of the cathodes, or all of the anodes, are connected together into a common lead, while the other end of each LED is individually available. This means fewer electrical connections to the package, and also allows us to easily enable or disable a particular digit by controlling the common lead There is no automatic advantage of the common-cathode seven-segment unit over the common-anode version, or vice-versa. Each type lends itself to certain applications, configurations, and logic families 19 Seven-Segment Display The 4511 incorporates an input latch so that it can hold and display a steady digit as part of a multi-digit count, while a new count is being accumulated in the background. The latch allows the display to be updated only at the end of each counting cycle, instead of displaying the ongoing count. The main circuitry is the Decoder section consisting of combinational logic circuits to accept a four-bit Binary Coded Decimal input and generate seven output signals to control the individual segments of a 7-segment display device The decoder section also has two additional inputs. Lamp Test (LT') turns all segments on so you can verify that all display segments are working. The Blanking (BL') input is just the reverse; it forces the entire display off. This is often used to blank out leading or trailing zeros 20 Seven-Segment Multiplexed Display Multi-character displays can be constructed by combining a number of individual seven-segment display modules If each display requires seven data lines, then an N-character display would require N x 7 data lines + 1 (common cathode / anode) However, it is possible to separately control each display’s ON / OFF status using its own common cathode / anode. The 7 data lines can then be “shared” between each of the characters (total = N + 7) The multiplexing technique relies on human persistence of vision. Each character is illuminated in sequence. Whilst it is illuminated, the shared data lines are set to a display the correct value on the selected display. When the next display is selected the data lines are set to the correct value for that one, and so on 21 Seven-Segment Multiplexed Display Altering the on-off ratio can be used to adjust the brightness. This can be controlled by a small delay routine during the ON state The refresh cycle should be > 50Hz for the displayed characters to appear continuous Multiplexed displays typically consume much less power than continuous display alternatives as only a single character is actually displayed at a given instant Unless the refresh circuitry is separate from the microcontroller (i.e. part of an intelligent display module) then the microcontroller must undertake the refresh operation. If other activities distract the CPU the display refreshing may be adversely affected 22 Seven-Segment Multiplexed Display 23 Liquid Crystal Displays LCD displays typically consume less current than LED displays but they rely on selective polarisation of liquid crystals to allow light to pass through or be attenuated. They need illumination if they are to be used in an environment where external light sources are absent Most modules conform a standard interface specification. 14pin access is provided having eight data lines, three control lines and three power lines 24 Liquid Crystal Displays The Register Select (RS) pin is used to control access to two registers within the LCD module If RS=0 the instruction command control register is selected, allowing the user to send a command such as clear display. If D0-7 are read, they indicate its status If RS=1 the data register is selected, allowing the user to send data to be displayed on the LCD at the current cursor location The Read/Write (R/W) line is pulled LOW to write commands or character data to the module, or HIGH to read character data or status information from the module 25 LCD Module Timing The Enable pin is used by the LCD module to latch information presented to its data pins. A High-to-Low transition must be applied to the Enable pin for the LCD to latch in the data. This pulse must be typically at least 450nsec wide When communicating with the command register, pin D7 can be used as a “busy” flag once Enable is pulled low. If D7 is HIGH then the module is occupied 26 LCD - Writing Characters Upon power-on reset the LCD initialises to a display-OFF state The Display On/Off & Cursor command is used to turn the display on. The data lines are set to 000011UB (underline, blank), RS=0 and R/W=0. The Enable line is then pulsed HIGH (>450 nsec) To enter a character the data lines are set to the appropriate value, the RS line is set HIGH and the R/W line remains LOW. Pulsing the Enable line will now cause the character to be written at the cursor’s current location Each time a character is entered the cursor moves to the next character location (leftwards). This auto-incrementing simplifies the programming of text strings If a character needs to be entered directly to a specific location on the display, then the command Set Display Address must first be used to move the cursor to the desired position 27 LCD Command Control Codes 28 Liquid Crystal Display Interfacing An LCD display typically requires 11 I/O pins of the 8051 29 LCD Brightness Control Vcc and Vss provide +5v and ground, respectively. VEE is used to control the LCD contrast as shown 30 Intelligent Display - DLG2416 These are four character 5 x 7 dot matrix displays driven by an on-board CMOS IC. The IC stores and decodes 7 bit ASCII data and displays it using a 5 x 7 font. Multiplexing circuitry, and drivers are also part of the IC The address and data inputs can be directly connected to the microprocessor address and data buses 31 DLG2416 Character Set & Timing CE1/2 A0/1 WR D0/6 CLR Internal latches within the 2416 hold onto the character values until they are explicitly reprogrammed or power is removed 32

0

0

advertisement

Download

advertisement

Add this document to collection(s)

You can add this document to your study collection(s)

Sign in Available only to authorized usersAdd this document to saved

You can add this document to your saved list

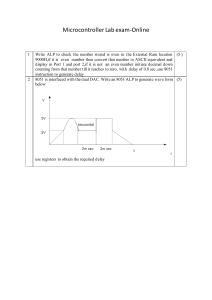

Sign in Available only to authorized users