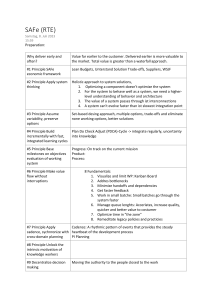

CADENCE/TSMC REFERENCE FLOW 6.0 Chip and package routability checking Chip and package STA Voltage island design planning Encounter RTL Compiler Design for test Encounter Test Low-power synthesis: Voltage island and fine-grain MTCMOS cell Encounter RTL Compiler Voltage island floorplan, power plan Enabled level shifter insertion APD620 Voltage island placement, CTS, IPO, fine-grain MTCMOS sleep net generation SoC Encounter GPS 65nm route, wire spreading Concurrent redundant via insertion NanoRoute, Fire & Ice QXC On-chip RC variation timing signoff Voltage island timing signoff CeltIC NDC APSI620 MCTMOS HVt retention path check Chip and package static IR-Drop SoC Encounter GPS Encounter Automatic Power Planner PrimeTime Spyglass-LP VSPE, APD620 CeltIC NDC, VoltageStorm Dynamic Gate (DG) Volatge island crosstalk, power, IR signoff Chip and package dynamic IR-Drop Hierarchical crosstalk analysis Hierarchical dynamic IR analysis VSDG, APD620 VoltageStorm (DG) Chip and package LVS Metal fill for balanced metal density DRC/LVS APD620 Physical verification Reference flow 6.0 — Cadence track As demands for increasing functionality, performance, and battery life drive the industry to migrate to nanometer process nodes, design teams face unprecedented challenges. At 65nm, additional challenges emerge in the areas of low power, DFM-aware routing, chip/package integration, and design for test (DFT). Design teams creating today's SoCs will require new solutions to meet their design goals. The TSMC Reference Flow 6.0 is the industry's first IC implementation flow that addresses these and many other key issues involved in creating electronics at 90nm and 65nm. TSMC pioneered the concept of a foundry-driven reference flow in 2001. Four years and five major releases later, the TSMC reference flow is the standard for the industry. Each release has anticipated new design challenges and offered the design community methodologies that instill increased confidence in using Cadence's products to design for TSMC's manufacturing processes. This systematic approach addresses the varied implementation requirements of leading-edge designs, minimizes unnecessary risks and delays, and improves your odds of achieving firstpass silicon success. The latest release, the TSMC Reference Flow 6.0, builds on previous versions. Included in Reference Flow 5.0 were TSMC-validated techniques for power optimization, power analysis, DFM, area reduction, chip and package Power consumption and integrity Low power and DFM Signal integrity NEW DFM Design complexity Power management Design challenges P&R iterations Power closure flow Power closure flow SI closure flow SI closure flow SI closure flow Hierarchical flow Hierarchical flow Hierarchical flow Hierarchical flow Synthesis & P&R link Timing-driven flow Timing closure flow Timing closure flow Timing closure flow Timing closure flow Timing closure flow Release 1.0 Release 2.0 Release 3.0 Release 4.0 Release 5.0 Release 6.0 0.25 micron 65nm TSMC Reference Flow 6.0, a comprehensive design flow portfolio integration, and flip chip area I/O design. These include key elements of the Cadence Encounter™ digital IC design platform—technologies that deal with issues such as low-power synthesis, multiple supply voltages and power domains, leakage power optimization, automatic power grid generation, and IR (voltage) drop analysis. Within the Encounter platform, Encounter RTL Compiler synthesis supplies the multiple threshold voltage (multi-Vt) library synthesis needed for low-power designs. Cadence First Encounter® Global Physical Synthesis (GPS) provides level shifter insertion for employing multiple power domains and automated power grid generation. Cadence First Encounter® Global Physical Synthesis (GPS) is a highcapacity, hierarchical, RTL-to-placednetlist implementation system within the Encounter platform. Complete peripheral I/O flip-chip design planning and 45 degree RDL routing is also integrated in the Encounter platform, which enables chip implementation in the presence of bump and RDL effects. Meanwhile, Cadence VoltageStorm® working together with the Cadence Allegro® system interconnect platform provides static and dynamic IR drop analysis as well as key capabilities for chip/package integration. Reference Flow 6.0 is a comprehensive new offering that uses advanced Cadence technologies to meet critical design and implementation challenges at 65 nanometers and below. It is ready now to handle today's most advanced nanometer designs. New in Reference Flow 6.0 are technologies for power optimization; power analysis with package effects; additional capabilities for chip/ package integration; and support for the 65nm process node, including DFM, routing, parasitic extraction, and DFT. Along with driving the evolution of process technologies, TSMC has collaborated closely with Cadence to meet design teams' increasingly tight technical constraints and advanced product requirements. TSMC Reference Flow 6.0 pays particular attention to these following technical issues: * Cadence First Encounter GPS is part of the Cadence SoC Encounter™ GPS offering. Power optimization/Power Analysis The TSMC Reference Flow 6.0 builds on previously created Cadence technologies for power optimization, such as the multiple supply voltage (MSV) features of First Encounter GPS as well as the power-shutdown, voltage-scaling, and leakage power optimization solutions delivered by Encounter RTL Compiler synthesis and First Encounter GPS. Further refinements to existing power optimization techniques include Cadence Encounter platform support for fine-grain and coarse-grain powergating using multi-threshold CMOS (MTCMOS) transistors, dynamic voltage scaling, and automatic power rail synthesis. MTCMOS power-gating works to reduce leakage currents by disconnecting the power supply from specific portions of a circuit when those portions are not needed. Dynamic voltage scaling is a type of hierarchical power optimization that can switch whole circuits or blocks into different power and, therefore, performance modes. Encounter enables designs to dynamically switch the circuit or block between different power supply voltages. Lowering the voltage supply to non-critical blocks or paths can significantly reduce dynamic and leakage power. Automatic power rail synthesis takes advantage of the Automatic Power Planner capability in the Encounter platform to detect power grid issues early in the design cycle through power prototyping. This lowers the cost of fixing problems and achieves a close correlation with back-end results due to a common power, IR drop, and electromigration analysis engine. Allegro platform in Reference Flow 6.0. The Allegro platform delivers a number of new capabilities for chip/package integration, including: • Differential pair analysis: Eye diagram inspection and timing extraction • Package power/ground RLC model extraction • Cross-talk analysis from bump to package to pin • Broadband package parameter to STA • TDR-like impedance profile checking Power integrity sign-off Reference Flow 6.0 includes Cadence VoltageStorm, which enables designers to perform analysis of static and dynamic power with package effects, MTCMOS paths, and dynamic voltage scaling. Hierarchical dynamic IR analysis can include RAM, soft block, and MTCMOS modeling. Design for Test As part of the Reference Flow 6.0, Cadence Encounter Test products— including test insertion and ATPG— were validated. This validation demonstrates that Encounter Test meets these TSMC requirements for 90nm and 65nm design. Chip and package co-design Today's highly complex nanometer designs also often have very high I/O and package pin counts coupled with high-speed interfaces, which require engineers to consider packagerelated physical and electrical effects concurrently in their designs. Integrated RDL design flow is also qualified in TSMC Reference Flow 6.0. Complete peripheral I/O flip-chip design planning and 45 degree RDL routing are integrated in the Encounter platform, which enables chip implementation in the presence of bump and RDL routing effects. RDL includes Cadence RC extraction, timing and SI analysis and optimization to provide an even more accurate physical implementation flow. To help customers optimize chip and package design flows, TSMC exclusively features the Cadence • Static and dynamic IR with package effect Using Allegro Package Designer, customers can achieve collaborative design of high-performance interconnect across the IC, package, and PCB domains. The Allegro platform comprises a design flow that includes extraction of package parasitics for use in the IC-level timing and IR drop modeling environment. Within version 6.0, the Allegro platform also helps customers to address emerging chip I/O and flipchip challenges. Routability, timing, and IR drop are major concerns for chip and package integration. In Reference Flow 6.0, the Allegro platform gives design teams the ability to analyze the impact of crosstalk on timing-from bump to package to pin. It also provides the ability to extract a frequency domain S-parameter AMS/RF package parasitic for high-speed I/Os and translate it to a time domain parasitic for timing for STA. This advanced capability extends to static and dynamic IR drop analysis as well. Previous capabilities for routability checks are augmented via TDR (Timing Driven Routing)-like impedance checks. First Encounter GPS can automatically insert metal fill into a placed and routed design to achieve a metal density within the range recommended by TSMC design rules. In addition, First Encounter GPS improves design quality by considering effects from inserted metal fill on timing analysis. First Encounter GPS also enables ECO flows for double-cut (dual) via insertion. The goal of ECO placement and routing after metal fill and dual via insertion is to prevent timing or density jumps between before-andafter ECO actions. Dual via insertion enhances yield by reducing the likelihood of opened vias, which can cause design failures. Support for 65nm process Cadence NanoRoute supports TSMC 65nm process rules with technologies for concurrent routing and dual via insertion. In addition, Cadence Fire & Ice® QX and Assura™ RCX support parasitic extraction for TSMC's production Nexsys 65 nm process node. For more detailed information, the TSMC Reference Flow 6.0 documentation and test case/scripts can be accessed via your TSMC-online account. FOR MORE INFORMATION http://www.cadence.com/company/news room/press_releases/pr.aspx?xml=060203 _TSMC Design for manufacturability Wire spreading, double-cut via optimization, and metal fill are three major Design for Manufacturability (DFM) steps in placement and routing. The TSMC Reference Flow 6.0 includes the Cadence First Encounter GPS system to bring these critical manufacturing issues into the IC design process. © 2005 Cadence Design Systems, Inc. All rights reserved. Cadence, the Cadence logo, Allegro, Fire & Ice, First Encounter, and VoltageStorm are registered trademarks and Assura, CeltIC, Encounter, SoC Encounter, and NanoRoute are trademarks of Cadence Design Systems, Inc. All others are properties of their respective holders. 6159 06/05