tsmc

SECURITY

Taiwan Semiconductor Manufacturing Co., LTD

B

TSMC-RESTRICTED SECRET

Ver.

2.6

Eff_Date

10-31-19

ECN No.

E120201933134

Author

M. H. Yang

(PDS)

Change Description

Please refer to Appendix A.13 Revision

History for the update from V2.5 to V2.6.

2.5_R

10-31-18

E120201842189

M. H. Yang

(PDS)

Correct attached seal ring gds file names.

No any rule and gds content change.

2.5

09-19-18

E120201838097

M. H. Yang

(PDS)

Please refer to Appendix A.12 Revision

History for the update from V2.4 to V2.5.

2.4

07-29-16

E120201631098

M. S. Hsieh

(PDS)

Please refer to Appendix A.11 Revision

History for the update from V2.3 to V2.4.

Approvals :

Title

Please refer to EDW workflow to see detail approval

records

TSMC 45/40 NM CMOS LOGIC AND

MS_RF DESIGN RULE

(CLN45LP/LPG, CLN40LP/LPG/LP+,

CLN40G)

Document No. : T-N45-CL-DR-001

Contents

Attach.

Total

: 600

:0

: 600

The information contained herein is the exclusive property of TSMC and shall not be distributed, copied, reproduced, or disclosed in

whole or in part without prior written permission of TSMC.

1 of 600

tsmc

SECURITY

Taiwan Semiconductor Manufacturing Co., LTD

B

TSMC-RESTRICTED SECRET

Ver.

2.3

Eff_Date

08-03-15

ECN No.

E120201531138

Author

Y. L. Chen

(PDS)

Change Description

Please refer to Appendix A.10 Revision

History for the update from V2.2 to V2.3.

2.2

12-01-14

E120201436190

Y. L. Chen

(PDS)

Please refer to Appendix A.9 Revision

History for the update from V2.1 to V2.2

2.1

06-28-13

E120201316032

Y. L. Chen

(PDS)

1.Please refer to Appendix A.8 Revision

History for the update from V2.0 to V2.1.

2.Change title

2.0

07-31-12

E120201231088

C. M. Kao

(PDS)

Please refer to Appendix A.7 Revision

History for the update from V1.3_1 to V2.0.

1.3_1

12-15-10

E070201048072

C. M. Kao

(PDS)

Please refer to Appendix A.6 Revision

History for the update from V1.3 to V1.3_1.

1.3

09-03-10

E070201036011

M. C. Lee

(PDS)

Please refer to Appendix A.5 Revision

History for the update from V1.2 to V1.3.

1.2

09-30-09

E070200935010

Y. M. Chen

Please refer to Appendix A.4 Revision

History for the update from V1.1 to V1.2.

1.1

06-30-08

E120200826098

C. H. Lu

Please refer to Appendix A.3 Revision

History for the update from V1.0 to V1.1.

1.0

01-31-08

E120200802093

C. H. Lu

Please refer to Appendix A.2 Revision

History for the update from V0.2 to V1.0.

0.2

10-18-07

E120200742028

C. H. Lu

Please refer to Appendix A.1 Revision

History for the update from V0.1 to V0.2.

0.1

04-04-07

E120200713104

C. T. Tsai

Provide the official N45GS design rule

manual

0.04

01-05-07

E120200704034

C. T. Tsai

Original

Title

TSMC 45/40 NM CMOS LOGIC AND

MS_RF DESIGN RULE

(CLN45LP/LPG, CLN40LP/LPG/LP+,

CLN40G)

Document No. : T-N45-CL-DR-001

The information contained herein is the exclusive property of TSMC and shall not be distributed, copied, reproduced, or disclosed in

whole or in part without prior written permission of TSMC.

2 of 600

SECURITY B – TSMC RESTRICTED SECRET

tsmc

Confidential – Do Not Copy

Document No.

Version

: T-N45-CL-DR-001

: 2.6

TSMC 45/40 NM CMOS LOGIC AND MS_RF DESIGN RULE

(CLN45LP/LPG, CLN40LP/LPG/LP+, CLN40G)

Table of Contents

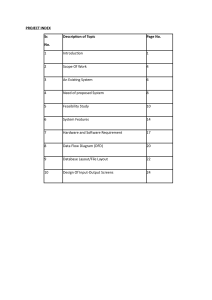

1 INTRODUCTION ................................................................................................................................................................. 8

1.1

1.2

OVERVIEW .................................................................................................................................................................. 8

REFERENCE DOCUMENT ............................................................................................................................................. 9

2 TECHNOLOGY OVERVIEW ............................................................................................................................................. 12

2.1

SEMICONDUCTOR PROCESS ...................................................................................................................................... 12

2.1.1

Front-End Features ......................................................................................................................................... 12

2.1.2

Back-End Features.......................................................................................................................................... 14

2.2

DEVICES................................................................................................................................................................... 15

2.3

POWER SUPPLY AND OPERATION TEMPERATURE RANGES.......................................................................................... 16

2.4

CROSS–SECTION ...................................................................................................................................................... 17

2.5

METALLIZATION OPTIONS .......................................................................................................................................... 23

3 GENERAL LAYOUT INFORMATION ............................................................................................................................... 27

3.1

MASK INFORMATION, KEY PROCESS SEQUENCE, AND CAD LAYERS............................................................................ 27

3.2

METAL/VIA CAD LAYER INFORMATION FOR METALLIZATION OPTIONS ......................................................................... 51

3.3

DUMMY PATTERN FILL CAD LAYERS ......................................................................................................................... 53

3.4

SPECIAL RECOGNITION CAD LAYER SUMMARY .......................................................................................................... 54

3.5

DEVICE TRUTH TABLES ............................................................................................................................................. 58

3.5.1

N45/N40 Low Power (LP): 1.1V Core Design ................................................................................................. 59

3.5.2

N40 Low Power Plus (N40LP+): 1.1V Core and 2.5V I/O Design .................................................................. 61

3.5.3

N45LPG/N40LPG: 1.1V/0.9V Core Design ..................................................................................................... 62

3.5.4

N40G (N45GS) General Purpose Superb: 0.9V Core Design ........................................................................ 64

3.5.5

MOM ................................................................................................................................................................ 65

3.5.6

Inductor ........................................................................................................................................................... 67

3.6

MASK REQUIREMENT FOR DEVICE OPTIONS (HIGH/STD/LOW VT/ULTRA LOW VT PLUS).............................................. 69

3.7

DESIGN GEOMETRY RESTRICTIONS ........................................................................................................................... 70

3.7.1

Design Grid Rules ........................................................................................................................................... 70

3.7.2

OPC Recommendations and Guidelines ........................................................................................................ 71

3.8

DESIGN HIERARCHY GUIDELINES ............................................................................................................................... 73

3.9

CHIP IMPLEMENTATION AND TAPE OUT CHECKLIST ..................................................................................................... 74

4 LAYOUT RULES AND RECOMMENDATIONS ............................................................................................................... 75

4.1

LAYOUT RULE CONVENTIONS .................................................................................................................................... 75

4.2

DERIVED GEOMETRIES USED IN PHYSICAL DESIGN RULES.......................................................................................... 76

4.2.1

Derived Geometries ........................................................................................................................................ 76

4.2.2

Special Definition............................................................................................................................................. 77

4.3

DEFINITION OF LAYOUT GEOMETRICAL TERMINOLOGY ................................................................................................ 78

4.4

MINIMUM PITCHES .................................................................................................................................................... 86

4.5

LAYOUT RULES AND GUIDELINES ............................................................................................................................... 87

4.5.1

Gate Oxide and Diffusion (OD) Layout Rules (Mask ID: 120) ........................................................................ 87

4.5.2

Deep N-Well (DNW) Layout Rules (Mask ID: 119) [Optional] ........................................................................ 91

4.5.3

N-Well (NW) Layout Rules .............................................................................................................................. 94

4.5.4

N-Well Resistor Within OD (NWROD) Layout Rules ...................................................................................... 95

4.5.5

N-Well Resistor Under STI (NWRSTI) Layout Rules ...................................................................................... 97

4.5.6

Native Device (NT_N) Layout Rules ............................................................................................................... 98

4.5.7

Thick Oxide (OD2) Layout Rules (Mask ID: 152) .......................................................................................... 100

4.5.8

Dual Core Oxide (DCO) Layout Rules (Mask ID: 153) ................................................................................. 102

The information contained herein is the exclusive property of TSMC and shall not be distributed, copied, reproduced, or disclosed in

whole or in part without prior written permission of TSMC.

3 of 600

SECURITY B – TSMC RESTRICTED SECRET

tsmc

Confidential – Do Not Copy

Document No.

Version

: T-N45-CL-DR-001

: 2.6

4.5.9

1.2V Core Oxide (OD_12) Layout Rules (Mask ID: 12A).............................................................................. 104

4.5.10 OD25_33 Layout Rules ................................................................................................................................. 106

4.5.11 OD25_18 Layout Rules ................................................................................................................................. 107

4.5.12 OD18_15 Layout Rules ................................................................................................................................. 108

4.5.13 Poly (PO) Layout Rules (Mask ID: 130) ........................................................................................................ 109

4.5.14 High Vt NMOS (VTH_N) Layout Rules (Mask ID: 11H) ................................................................................ 116

4.5.15 High Vt PMOS (VTH_P) Layout Rules (Mask ID: 11G) ................................................................................ 117

4.5.16 Low Vt NMOS (VTL_N) Layout Rules (Mask ID: 118) .................................................................................. 118

4.5.17 Low Vt PMOS (VTL_P) Layout Rules (Mask ID: 117) .................................................................................. 119

4.5.18 Ultra Low Vt Plus Devices Layout Rules ....................................................................................................... 120

4.5.19 P+ Source/Drain Ion Implantation (PP) Layout Rules (Mask ID: 197) .......................................................... 124

4.5.20 N+ Source/Drain Ion Implantation (NP) Rules (Mask ID: 198) ..................................................................... 126

4.5.21 Layout Rules for LDD Mask Logical Operations ........................................................................................... 128

4.5.22 Resist Protection Oxide (RPO) Layout Rules (Mask ID: 155) ...................................................................... 130

4.5.23 OD and Poly Resistor Layout Rules.............................................................................................................. 131

4.5.24 HVMOS_25 Layout Rules ............................................................................................................................. 133

4.5.25 HVMOS_18 Layout Rules ............................................................................................................................. 139

4.5.26 HVMOS Guard-Ring Rules and Guidelines for HVMOS_25 and HVMOS_18 ............................................. 145

4.5.27 MOS Varactor Layout Rules (VAR)............................................................................................................... 146

4.5.28 Contact (CO) Layout Rules (Mask ID: 156) .................................................................................................. 149

4.5.29 Metal-1 (M1) Layout Rules (Mask ID: 360) ................................................................................................... 152

4.5.30 VIAx Layout Rules (Mask ID: 378, 379, 373, 374, 375, 376, 377) ................................................................ 159

4.5.31 Mx Layout Rules (Mask ID: 380, 381, 384, 385, 386, 387, 388) .................................................................. 165

4.5.32 LOWMEDN Layout Rules ............................................................................................................................. 172

4.5.33 VIAy Layout Rules (Mask ID: 379, 373, 374, 375, 376, 377, 372, 37A) ....................................................... 174

4.5.34 My Layout Rules (Mask ID: Second Inter-layer Metal (385, 386, 387, 388) and Top Metal (381, 384, 385,

386, 387, 388, 389, 38A)) ............................................................................................................................................ 179

4.5.35 Top VIAz Layout Rules (Mask ID: 379, 373, 374, 375, 376, 377, 372, 37A) ................................................ 182

4.5.36 Top Mz Layout Rules (Mask ID: 381, 384, 385, 386, 387, 388, 389, 38A) ................................................... 186

4.5.37 Top VIAr Layout Rules (Mask ID: 375, 376, 377, 372, 37A) ......................................................................... 188

4.5.38 Top Mr Layout Rules (Mask ID: 386, 387, 388, 389, 38A) ........................................................................... 191

4.5.39 RV Layout Rules (Mask ID: 306)................................................................................................................... 193

4.5.40 Al Redistributional Layer (AP RDL) Layout Rules (Mask ID: 309) ................................................................ 194

4.5.41 Via Layout Recommendations ...................................................................................................................... 196

4.5.42 MOM Layout Rules........................................................................................................................................ 197

4.5.43 Top VIAu Layout Rules (Mask ID: 373, 374, 375, 376, 377, 372, 37A) ........................................................ 203

4.5.44 Mu (Ultra Thick Metal) Layout Rules ............................................................................................................. 204

4.5.45 Inductor Layout Rules ................................................................................................................................... 206

4.5.46 Introduction of Inductor and Transmission Line ............................................................................................ 215

4.5.47 SRAM Rules .................................................................................................................................................. 219

4.5.48 NPreDOSRM (50;21) Layout Rules .............................................................................................................. 225

4.5.49 SRAM Periphery (Word Line Driver) Rules ................................................................................................... 227

4.5.50 SRAM CO2 (100;0) Layout Rule for Embedded DRAM (eDRAM) Process ................................................. 228

4.5.51 ROM Rules .................................................................................................................................................... 229

4.5.52 Antenna Effect Prevention (A) Layout Rules ................................................................................................ 230

4.5.53 Product Labels and Logo Rules .................................................................................................................... 235

4.5.54 Seal Ring Overview ....................................................................................................................................... 236

4.5.55 Resistor Warning Rules ................................................................................................................................ 276

4.5.56 DRM and DRC Completeness ...................................................................................................................... 277

5 LAYOUT GUIDELINES FOR THE DEVICE GEOMETRY EFFECT ............................................................................... 278

5.1

LAYOUT RULES FOR THE WPE (W ELL PROXIMITY EFFECT)....................................................................................... 278

5.2

LAYOUT GUIDELINES FOR LOD (LENGTH OF THE OD REGION) EFFECT ...................................................................... 282

5.2.1

What is LOD? ................................................................................................................................................ 282

5.2.2

How to have a precise LOD Simulation ........................................................................................................ 282

5.3

LAYOUT GUIDELINES FOR OSE (OD SPACE EFFECT) ............................................................................................... 283

5.3.1

What is OSE? ................................................................................................................................................ 283

5.3.2

Id change on device due to OSE .................................................................................................................. 283

5.3.3

How to reduce the differences between pre-simulation and post-simulation ............................................... 284

5.4

LAYOUT GUIDELINES FOR PSE (POLY SPACE EFFECT) ............................................................................................. 287

5.4.1

What is PSE? ................................................................................................................................................ 287

5.4.2

Id change on device due to PSE ................................................................................................................... 287

5.4.3

How to reduce the differences between pre-simulation and post-simulation on N40G circuit? ................... 287

5.5

LAYOUT GUIDELINES FOR D-CESL EFFECT .............................................................................................................. 288

The information contained herein is the exclusive property of TSMC and shall not be distributed, copied, reproduced, or disclosed in

whole or in part without prior written permission of TSMC.

4 of 600

SECURITY B – TSMC RESTRICTED SECRET

tsmc

5.5.1

5.5.2

5.5.3

Confidential – Do Not Copy

Document No.

Version

: T-N45-CL-DR-001

: 2.6

What is d-CESL effect? ................................................................................................................................. 288

Id change on the N40G device due to d-CESL ............................................................................................. 288

How to reduce the differences between pre-simulation and post-simulation on N40G circuit? ................... 289

6 N40LP/LPG DESIGN INFORMATION ............................................................................................................................ 291

6.1

NON-SHRINKABLE LAYOUT RULES ........................................................................................................................... 291

6.1.1

Purpose: ........................................................................................................................................................ 291

6.1.2

Non-shrinkable Rules .................................................................................................................................... 291

6.1.3

Stress Migration and Wide Metal Spacing Rules Adjustment (Rule Relaxing) ............................................. 292

6.1.4

Pad Rule for Wire Bond ................................................................................................................................ 294

6.1.5

Flip Chip Bump Rules ................................................................................................................................... 294

6.2

DESIGN FLOW FOR TAPE-OUT ................................................................................................................................ 295

6.2.1

How to design for CLN40LP/LPG shrink technology .................................................................................... 295

6.2.2

How to prepare a new design of CLN40LP/LPG .......................................................................................... 295

6.2.3

CLN45LP/LPG Design Migration to CLN40LP/LPG Technology .................................................................. 296

6.2.4

Layout check and post simulation ................................................................................................................. 297

7 LAYOUT RULES AND RECOMMENDATIONS FOR ANALOG CIRCUITS .................................................................. 301

7.1

USER GUIDES ......................................................................................................................................................... 301

7.2

LAYOUT RULES, RECOMMENDATIONS AND GUIDELINES FOR THE ANALOG DESIGNS ................................................... 302

7.2.1

General Guidelines........................................................................................................................................ 302

7.2.2

MOS Recommendations ............................................................................................................................... 303

7.2.3

Bipolar Transistor (BJT) Rules and Recommendations ................................................................................ 304

7.2.4

Resistor Rules ............................................................................................................................................... 305

7.2.5

Capacitor Guidelines ..................................................................................................................................... 306

7.3

LAYOUT RULES AND GUIDELINES FOR DEVICE PLACEMENT ....................................................................................... 307

7.3.1

General Rules and Guidelines ...................................................................................................................... 307

7.3.2

Matching Rules and Guidelines .................................................................................................................... 308

7.3.3

Electrical Performance Rules and Guidelines ............................................................................................... 315

7.3.4

Noise ............................................................................................................................................................. 320

7.4

BURN-IN GUIDELINES FOR ANALOG CIRCUITS ........................................................................................................... 323

8 DUMMY PATTERN RULE AND FILLING GUIDELINE .................................................................................................. 325

8.1

DUMMY OD (DOD/SR_DOD) RULES AND GUIDELINES ............................................................................................ 325

8.1.1

DOD Layout Rules ........................................................................................................................................ 326

8.1.2

SR_DOD Layout Rules ................................................................................................................................. 328

8.2

DUMMY POLY (DPO/SR_DPO) RULES AND GUIDELINES ......................................................................................... 330

8.2.1

DPO Layout Rules......................................................................................................................................... 331

8.2.2

SR_DPO Layout Rules ................................................................................................................................. 332

8.3

DUMMY TCD RULE AND FILLING GUIDELINE ............................................................................................................. 334

8.3.1

Dummy TCD Rules ....................................................................................................................................... 334

8.3.2

Dummy TCD layout Summary ...................................................................................................................... 338

8.4

DUMMY TCD DESIGN INFORMATION ........................................................................................................................ 339

8.4.1

Overview ....................................................................................................................................................... 339

8.4.2

Design Consideration of Dummy TCD Insertion ........................................................................................... 339

8.4.3

Dummy TCD Macro Placement .................................................................................................................... 340

8.4.4

P&R Dummy TCD Rule Check ..................................................................................................................... 341

8.4.5

Dummy TCD Macros Insertion Flow ............................................................................................................. 341

8.4.6

TCD Library Kits ............................................................................................................................................ 342

8.5

IN CHIP OVERLAY (ICOVL) RULE AND FILLING GUIDELINE........................................................................................ 343

8.5.1

In Chip Overlay (ICOVL) Rules ..................................................................................................................... 343

8.5.2

ICOVL layout Summary ................................................................................................................................ 349

8.5.3

N40 In-Chip OVL Marker Design Insertion Methodology .............................................................................. 350

8.6

DUMMY METAL (DM) RULES ................................................................................................................................... 353

8.7

DUMMY VIA (DVIAX) RULES ................................................................................................................................... 357

8.8

DUMMY PATTERN FILL USAGE SUMMARY ................................................................................................................. 359

8.8.1

Dummy Pattern Filling Requirements ........................................................................................................... 359

8.8.2

Recommended Flow for Dummy Pattern Filling ........................................................................................... 360

8.8.3

Blockage Layer (ODBLK/POBLK/DMxEXCL/ DVIAxEXCL) Requirements and Recommendations ........... 361

8.8.4

Dummy Pattern Filling Guidelines ................................................................................................................. 362

8.8.5

Mask Revision Guidelines ............................................................................................................................. 363

8.8.6

Dummy Pattern Re-fill Evaluation Flow Chart ............................................................................................... 364

The information contained herein is the exclusive property of TSMC and shall not be distributed, copied, reproduced, or disclosed in

whole or in part without prior written permission of TSMC.

5 of 600

SECURITY B – TSMC RESTRICTED SECRET

tsmc

Confidential – Do Not Copy

Document No.

Version

: T-N45-CL-DR-001

: 2.6

9 DESIGN FOR MANUFACTURING (DFM) ...................................................................................................................... 368

9.1

LAYOUT GUIDELINES FOR YIELD ENHANCEMENT....................................................................................................... 368

9.1.1

Layout Tips for Minimizing Critical Areas ...................................................................................................... 368

9.1.2

Guidelines for Optimal Electrical Model and Silicon Correlation ................................................................... 371

9.1.3

Electrical Wiring............................................................................................................................................. 378

9.1.4

Guidelines for Mask Making Efficiency ......................................................................................................... 378

9.2

DFM RECOMMENDATIONS AND GUIDELINES SUMMARY............................................................................................. 379

9.2.1

Action-Required Rules .................................................................................................................................. 379

9.2.2

Recommendations ........................................................................................................................................ 380

9.2.3

Guidelines ..................................................................................................................................................... 385

9.2.4

Grouping Table of Recommendations .......................................................................................................... 386

9.3

GDA DIE SIZE OPTIMIZATION KIT ............................................................................................................................ 389

9.3.1

What is MFU?................................................................................................................................................ 390

9.3.2

Design Guidelines for Higher MFU ............................................................................................................... 390

9.3.3

Recommended GDA criteria MFU > 80% ..................................................................................................... 390

9.3.4

MFU Reference Table for N45 ...................................................................................................................... 391

9.3.5

MFU Reference Table for N40 ...................................................................................................................... 392

10 LAYOUT GUIDELINES FOR LATCH-UP AND I/O ESD .............................................................................................. 393

10.1 LAYOUT RULES AND GUIDELINES FOR LATCH-UP PREVENTION .................................................................................. 394

10.1.1 Latch-up Introduction .................................................................................................................................... 394

10.1.2 Layout Rules and Guidelines for Latch-up Prevention.................................................................................. 397

10.1.3 Test Specification and Requirements ........................................................................................................... 416

10.2 I/O ESD PROTECTION CIRCUIT DESIGN, LAYOUT RULES AND GUIDELINES ................................................................ 417

10.2.1 ESD introduction ........................................................................................................................................... 417

10.2.2 TSMC IO ESD layout style introduction ........................................................................................................ 420

10.2.3 ESD Implant (ESDIMP) Layout Rules (MASK ID: 111) ................................................................................ 422

10.2.4 SR_ESD device Layout Rules (N40G only) .................................................................................................. 423

10.2.5 ESD Dummy Layers Summary ..................................................................................................................... 424

10.2.6 ESD circuits Definition ................................................................................................................................... 425

10.2.7 Requirements for ESD Implant Masks .......................................................................................................... 426

10.2.8 DRC methodology for ESD guidelines .......................................................................................................... 426

10.2.9 ESD Guidelines ............................................................................................................................................. 431

10.3 ESD BACK-END RELIABILITY GUIDELINES ................................................................................................................ 456

10.3.1 Test Methodology .......................................................................................................................................... 456

10.3.2 Failure Mechanism ........................................................................................................................................ 457

10.3.3 Maximum ESD Current Density for Resistor ................................................................................................. 457

10.3.4 Maximum ESD Current Density for Via and Metal ........................................................................................ 458

10.3.5 Minimum ESD Current for ESD Device......................................................................................................... 459

10.4 TIPS FOR THE ESD/LATCHUP DESIGN ...................................................................................................................... 460

10.4.1 Tips for General Latchup Design .................................................................................................................. 460

10.4.2 Tips for General ESD Design ........................................................................................................................ 460

10.4.3 Tips for Power-Ground ESD Protection ........................................................................................................ 462

10.4.4 Tips for MOS gate directly connected to power/ground/IO PAD .................................................................. 463

10.5 ESD TESTING METHODOLOGY ................................................................................................................................. 466

10.5.1 Stress condition and Measurement condition ............................................................................................... 466

10.5.2 Failure criteria................................................................................................................................................ 466

11 CLN45LP/LPG RELIABILITY RULES .......................................................................................................................... 467

11.1 TERMINOLOGY ........................................................................................................................................................ 467

11.2 FRONT-END PROCESS RELIABILITY RULES AND MODELS .......................................................................................... 467

11.2.1 I/O Over Drive Voltage .................................................................................................................................. 467

11.2.2 Gate Oxide Integrity ...................................................................................................................................... 467

11.2.3 Hot Carrier Injection Effect ............................................................................................................................ 470

11.2.4 Negative Bias Temperature Instability (NBTI) ............................................................................................... 473

11.2.5 N45 Poly Current Density .............................................................................................................................. 475

11.2.6 N45 Poly EM Joule heating ........................................................................................................................... 475

11.2.7 N45 OD Current Density ............................................................................................................................... 476

11.3 BACK-END PROCESS RELIABILITY RULES................................................................................................................. 477

11.3.1 Stress Migration (SM) ................................................................................................................................... 477

11.3.2 Low-k Dielectric Integrity ............................................................................................................................... 477

11.3.3 Cu Metal Current Density (EM) Specifications .............................................................................................. 478

The information contained herein is the exclusive property of TSMC and shall not be distributed, copied, reproduced, or disclosed in

whole or in part without prior written permission of TSMC.

6 of 600

SECURITY B – TSMC RESTRICTED SECRET

tsmc

11.3.4

11.3.5

11.3.6

Confidential – Do Not Copy

Document No.

Version

: T-N45-CL-DR-001

: 2.6

AP RDL Current Density (EM) Specifications ............................................................................................... 484

Cu Metal AC Operation ................................................................................................................................. 485

AP RDL AC Operation .................................................................................................................................. 494

12 CLN40LP/LPG/45GS(=40G) RELIABILITY RULES .................................................................................................... 495

12.1 TERMINOLOGY ........................................................................................................................................................ 495

12.2 FRONT-END PROCESS RELIABILITY RULES AND MODELS .......................................................................................... 495

12.2.1 I/O Over Drive Voltage .................................................................................................................................. 495

12.2.2 Gate Oxide Integrity ...................................................................................................................................... 495

12.2.3 Hot Carrier Injection Effect ............................................................................................................................ 499

12.2.4 Negative Bias Temperature Instability (NBTI) ............................................................................................... 502

12.2.5 N40 Poly Current Density .............................................................................................................................. 504

12.2.6 N40 Poly EM Joule heating ........................................................................................................................... 504

12.2.7 N40 OD Current Density ............................................................................................................................... 505

12.3 BACK-END PROCESS RELIABILITY RULES................................................................................................................. 506

12.3.1 Stress Migration (SM) ................................................................................................................................... 506

12.3.2 Low-k Dielectric Integrity ............................................................................................................................... 506

12.3.3 Cu Metal Current Density (EM) Specifications .............................................................................................. 508

12.3.4 AP RDL Current Density (EM) Specifications ............................................................................................... 514

12.3.5 Cu Metal AC Operation ................................................................................................................................. 515

12.3.6 AP RDL AC Operation .................................................................................................................................. 526

13 APPENDIX A REVISION HISTORY .............................................................................................................................. 527

A.1 FROM VERSION 0.1 TO 0.2........................................................................................................................................... 527

A.2 FROM VERSION 0.2 TO 1.0........................................................................................................................................... 537

A.3 FROM VERSION 1.0 TO 1.1........................................................................................................................................... 539

A.4 FROM VERSION 1.1 TO 1.2........................................................................................................................................... 544

A.5 FROM VERSION 1.2 TO 1.3........................................................................................................................................... 563

A.6 FROM VERSION 1.3 TO 1.3_1....................................................................................................................................... 565

A.7 FROM VERSION 1.3_1 TO 2.0....................................................................................................................................... 567

A.8 FROM VERSION 2.0 TO 2.1........................................................................................................................................... 592

A.9 FROM VERSION 2.1 TO 2.2........................................................................................................................................... 595

A.10 FROM VERSION 2.2 TO 2.3......................................................................................................................................... 597

A.11 FROM VERSION 2.3 TO 2.4......................................................................................................................................... 599

A.12 FROM VERSION 2.4 TO 2.5......................................................................................................................................... 599

A.13 FROM VERSION 2.5 TO 2.6......................................................................................................................................... 600

The information contained herein is the exclusive property of TSMC and shall not be distributed, copied, reproduced, or disclosed in

whole or in part without prior written permission of TSMC.

7 of 600

SECURITY B – TSMC RESTRICTED SECRET

tsmc

Confidential – Do Not Copy

Document No.

Version

: T-N45-CL-DR-001

: 2.6

1 Introduction

This chapter has been divided into the following topics:

1.1

Overview

1.2

Reference document

1.1

Overview

This document provides all the rules and reference information for the design and layout of integration circuits

using the TSMC 45 nm CMOS LOGIC 1P10M (single poly, 10 metal layers), salicide, Cu technology. These

rules and information about other specifications apply to TSMC semiconductor process: CLN45LP, CLN40LP,

CLN40LP+, CLN45LPG, N40LPG, N40G (= N45GS), and N45/N40 MSRF.

CLN45LP is a low-power product for applications with an 1.1V core design and with an 1.8V or a 2.5V

capable I/O’s.

CLN40LP is a low-power product which is 90% linear shrinkage from CLN45LP layout dimension for

applications with an 1.1V core design, and with an 1.8V or a 2.5V capable I/O’s.

CLN40LP+ (40nm low power plus) is a low-power product for applications with an 1.1V core design and

with a 2.5V capable I/O’s by adding ultra low Vt plus devices into TSMC 40nm CMOS logic low power

(CLN40LP) process.

CLN45LPG is a low-power and low standby power product for applications with both 1.1V (LP) and 0.9V

(G) core designs and with an 1.8V capable I/O’s.

CLN40LPG is a low-power and low standby power product which is 90% linear shrinkage from CLN45

layout dimension for applications with both 1.1V (LP) and 0.9V (G) core designs and with a 3.3V capable

I/O’s. If you want to shrink CLN45LPG to CLN40LPG, you must redesign 3.3V I/O since 1.8V I/O cannot

be shrunk in LPG process.

N40G (= N45GS) is a general-purpose product which is 90% linear shrinkage from 45nm layout

dimension for applications with a 0.9V core design and with 1.8V, 2.5V capable I/O’s.

N45/N40 MSRF process can adopt the regular logic processes (CLN45LP/ CLN40LP/ CLN45LPG/

CLN40LPG/ CLN40G (=CLN45GS)), or adopt an ultra thick metal (Mu: 34KÅ or 35KÅ ) as the most top

metal layer (Mu layer only can be used as the most top metal layer).

In this document, figures and tables are usually numbered with 3 digits. The first two digits indicate section

number and the last one is sequence number. For example, Table 1.2.1 is the first table in the section 1.2 of

Chapter 1.

Warning: All tape-outs MUST be DRC clean.

The information contained herein is the exclusive property of TSMC and shall not be distributed, copied, reproduced, or disclosed in

whole or in part without prior written permission of TSMC.

8 of 600

SECURITY B – TSMC RESTRICTED SECRET

tsmc

1.2

Document No.

Version

: T-N45-CL-DR-001

: 2.6

Reference Document

Table 1.2.1

Reference Documents

Content

GDS layer usage

DRC deck

Wire bond and EU Flip Chip

DRM

Wire bond and EU Flip Chip

DRC deck

DENMOS DRM

LF Flip Chip DRM

LF Flip Chip DRC

Dummy pattern generation

utility

DFM guideline

DFM utility

SPICE

Confidential – Do Not Copy

Reference Document

T-N45-CL-LE-001

TSMC 45/40 NM GENERAL PURPOSE GDS LAYER USAGE DESCRIPTION FILE

T-N45-CL-DR-001-X1 (X is the code of EDA tool. Please refer to TSMC-Online for the details.)

TSMC 45 NM CMOS LOGIC AND 40NM CMOS LOGIC DRC COMMAND FILE (CLN45LP/LPG, CLN40LP/LPG,

CLN40G)

T-N45-CL-DR-003

TSMC 45NM/40NM WIRE BOND, EUTECTIC FLIP CHIP AND INTERCONNECTION DESIGN RULE

T-N45-CL-DR-003-X1 (X is the code of EDA tool. Please refer to TSMC-Online for the details.)

TSMC 45NM/40NM WIRE BOND, EUTECTIC FLIP CHIP AND INTERCONNECTION DRC COMMAND FILE

T-N40-CM-DR-004

TSMC 40 NM RF HIGH VOLTAGE NMOS (DEMOS) DESIGN RULE

T-N45-CL-DR-017

TSMC 45/40 NM LEAD FREE (LF) BUMP FLIP CHIP WITH BUILD UP SUBSTRATE (FCBGA, FLIP CHIP BALL

GRID ARRAY) AND INTERCONNECTION DESIGN RULE

T-N45-CL-DR-022

TSMC 45/40 NM LEAD FREE (LF) BUMP FLIP CHIP WITH LAMINATE SUBSTRATE (FCCSP, FLIP CHIP CHIP

SCALE PACKAGE) AND INTERCONNECTION DESIGN RULE

T-N45-CL-DR-017-X1 (X is the code of EDA tool. Please refer to TSMC-Online for the details.)

TSMC 45/40 NM LEAD FREE (LF) BUMP FLIP CHIP WITH BUILD UP SUBSTRATE (FCBGA, FLIP CHIP BALL

GRID ARRAY) AND INTERCONNECTION DRC COMMAND FILE

T-N45-CL-DR-022-X1 (X is the code of EDA tool. Please refer to TSMC-Online for the details.)

TSMC 45/40 NM LEAD FREE (LF) BUMP FLIP CHIP WITH LAMINATE SUBSTRATE (FCCSP, FLIP CHIP CHIP

SCALE PACKAGE) AND INTERCONNECTION DRC COMMAND FILE

T-N45-CL-DR-001-X2 (X is the code of EDA tool. Please refer to TSMC-Online for the details)

TSMC 45NM CMOS LOGIC DUMMY OD/PO GENERATION UTILITY

T-N45-CL-DR-001-X3 (X is the code of EDA tool. Please refer to TSMC-Online for the details)

TSMC 45NM CMOS LOGIC DUMMY METAL GENERATION UTILITY

T-N40-CL-RP-020

TSMC 40 NM CMOS LOGIC GENERAL PURPOSE DFM ROLLOUT PACKAGE REPORT

T-N40-CL-RP-016

TSMC N45/N40 LAYOUT GUIDELINES FOR LAYOUT ENVIRONMENT AND CO PLACEMENT

T-N45-CL-DR-001-X4 (X is the code of EDA tool. Please refer to TSMC-Online for the details.)

TSMC 45NM DFM REDUNDANT VIA UTILITY

T-N45-CL-SP-001

TSMC 45NM CMOS LOGIC LOW POWER 1P10M+AL_RDL SALICIDE Cu_ELK 1.1V/1.8V SPICE MODELS

(CLN45LP)

T-N45-CL-SP-012

TSMC 45 NM CMOS LOGIC LOW POWER 1P10M+AL_RDL SALICIDE CU_ELK 1.1V/2.5V SPICE MODELS

(CLN45LP)

T-N45-CL-SP-051

TSMC 45 NM CMOS LOGIC LOW POWER HIGH VOLTAGE 1P10M+AL_RDL SALICIDE CU_ELK 2.5V SPICE

MODELS 45LP

T-N40-CL-SP-040

TSMC 40 NM CMOS LOGIC GENERAL PURPOSE SALICIDE 1P10M_7X2Z+UT-ALRDL CU_ELK HD BEOL SPICE

MODEL 40G

T-N45-CE-SP-001

TSMC 45 NM CMOS EMBEDDED DRAM GENERAL PURPOSE SUPERB 1P8M_5X2R_UT-ALRDL SALICIDE

CU_LOWK 0.9V&1.4V SPICE MODELS 40G (CLN45GS EDRAM)

T-N40-CL-SP-038

TSMC 40 NM CMOS LOGIC LOW POWER HIGH VOLTAGE 1P10M+AL_RDL SALICIDE CU_ELK 1.8V SPICE

MODELS 40LP

T-N40-CL-SP-034

TSMC 40 NM CMOS LOGIC LOW POWER HIGH VOLTAGE 1P10M+ AL_RDL SALICIDE CU_ELK 2.5V SPICE

MODEL 40LP

T-N40-CL-SP-041

TSMC 40 NM CMOS LOGIC LOW POWER SALICIDE 1P10M_7X2Z+UT-ALRDL CU_ELK HD BEOL SPICE

MODEL 40LP

T-N40-CL-SP-031-P1

TSMC 40 NM CMOS LOGIC LP-BASED TRIPLE GATE OXIDE WITH DUAL CORE 1P10M+AL_RDL SALICIDE

ELK CU 0.9/1.1/3.3V SPICE MODEL 40LPG (PRE-RELEASE)

T-N40-CE-SP-001

TSMC 40 NM CMOS EMBEDDED DRAM LOW POWER 1P8MT2 (2XTM : M7-M8) SALICIDE CU_LOWK

1.1V&1.5V SPICE MODELS (CLN40LP EDRAM)

T-N40-CL-SP-051

TSMC 40 NM CMOS LOGIC LOW POWER PLUS 1P10M SALICIDE CU_ELK 1.1/2.5V SPICE MODEL 40LE

The information contained herein is the exclusive property of TSMC and shall not be distributed, copied, reproduced, or disclosed in

whole or in part without prior written permission of TSMC.

9 of 600

SECURITY B – TSMC RESTRICTED SECRET

tsmc

Content

Device formation examples

and LVS properties

LVS

Confidential – Do Not Copy

Document No.

Version

: T-N45-CL-DR-001

: 2.6

Reference Document

T-N40-CL-SP-038

TSMC 40 NM CMOS LOGIC LOW POWER HIGH VOLTAGE 1P10M+AL_RDL SALICIDE CU_ELK 1.8V SPICE

MODELS 40LP

T-N40-CL-SP-034

TSMC 40 NM CMOS LOGIC LOW POWER HIGH VOLTAGE 1P10M+ AL_RDL SALICIDE CU_ELK 2.5V SPICE

MODEL 40LP

T-N40-CL-SP-032

TSMC 40NM CMOS LOGIC LOW POWER 1P10M+AL_RDL SALICIDE CU_ELK 1.1V/1.8V SPICE MODELS 40LP

T-N40-CL-SP-004

TSMC 40NM CMOS LOGIC LOW POWER 1P10M+AL_RDL SALICIDE CU_ELK 1.1V/2.5V SPICE MODELS 40LP

T-N45-CL-SP-012

TSMC 45NM CMOS LOGIC LOW POWER 1P10M+AL_RDL SALICIDE Cu_ELK 1.1V/2.5V SPICE MODELS

(CLN45LP)

T-N45-CL-SP-010

TSMC 45 NM CMOS LOGIC GENERAL PURPOSE SUPERB 1P10M+AL_RDL SALICIDE CU_ELK 0.9V/1.2V/1.8V

SPICE MODELS 40G

T-N45-CL-SP-011

TSMC 45 NM CMOS LOGIC GENERAL PURPOSE SUPERB 1P10M+AL_RDL SALICIDE CU_ELK 0.9/1.2V/2.5V

SPICE MODEL 40G

T-N45-CL-SP-053

TSMC 45 NM CMOS LOGIC GENERAL PURPOSE SUPERB 1P10M+AL RDL SALICIDE CU_ELK 0.9/1.8V

SPICE MODELS 40G

T-N45-CM-SP-004

TSMC 45 NM CMOS MIXED SIGNAL RF LOW POWER 1P9M+AL_RDL SALICIDE CU_ELK 1.1&1.8V SPICE

MODEL 45LP

T-N40-CM-SP-004

TSMC 40 NM CMOS MIXED SIGNAL RF GENERAL PURPOSE 1P10M+AL_RDL SALICIDE CU_ELK 0.9/1.8V

SPICE MODEL 40G (45GS, TGO)

T-N40-CM-SP-007

TSMC 40 NM CMOS MIXED SIGNAL RF GENERAL PURPOSE 1P10M+AL_RDL SALICIDE CU_ELK 0.9/1.8V

SPICE MODEL 40G (45GS, DGO)

T-N40-CM-SP-003

TSMC 40 NM CMOS MIXED SIGNAL RF GENERAL PURPOSE 1P10M+AL_RDL SALICIDE CU_ELK 0.9/2.5V

SPICE MODEL 40G (45GS)

T-N40-CM-SP-002

TSMC 40 NM CMOS MIXED SIGNAL RF LOW POWER 1P10M+AL_RDL SALICIDE CU_ELK 1.1&1.8V SPICE

MODEL 40LP

T-N40-CM-SP-001

TSMC 40 NM CMOS MIXED SIGNAL RF LOW POWER 1P10M+AL_RDL SALICIDE CU_ELK 1.1&2.5V SPICE

MODEL 40LP

T-N45-CM-SP-003

TSMC 45 NM CMOS MIXED SIGNAL RF LOW POWER 1P9M+AL_RDL SALICIDE CU_ELK 1.1&2.5V SPICE

MODEL 45LP

T-N45-CL-LS-001

TSMC 45 NM CMOS LOGIC GENERAL PURPOSE 1P10M SALICIDE DEVICE FORMATION EXAMPLES AND LVS

PROPERTIES

T-N45-CL-LS-002

TSMC 45 NM CMOS LOGIC GENERAL PURPOSE SUPERB 1P10M SALICIDE CU_ELK 0.9&2.5V DEVICE

FORMATION EXAMPLES AND LVS PROPERTIES

T-N40-CL-LS-001

TSMC 40 NM CMOS LOW POWER DEVICE FORMATION EXAMPLES AND LVS PROPERTIES

(CLN40LP/CLN40LPG/CRN40LP)

T-N45-CL-LS-001-X1 (X is the code of EDA tool. Please refer to TSMC-Online for the details.)

TSMC 45 NM CMOS LOGIC GENERAL PURPOSE DEVICE FORMATION EXAMPLES AND LVS PROPERTIES

LVS COMMAND FILE

T-N45-CL-LS-002-X1 (X is the code of EDA tool. Please refer to TSMC-Online for the details.)

TSMC 45 NM CMOS LOGIC GENERAL PURPOSE SUPERB 1P10M SALICIDE CU_ELK 0.9&2.5V DEVICE

FORMATION EXAMPLES AND LVS PROPERTIES

T-N40-CL-LS-001-X1 (X is the code of EDA tool. Please refer to TSMC-Online for the details.)

TSMC 40 NM CMOS LOW POWER LVS COMMAND FILE (CLN40LP/CLN40LPG/CRN40LP)

The information contained herein is the exclusive property of TSMC and shall not be distributed, copied, reproduced, or disclosed in

whole or in part without prior written permission of TSMC.

10 of 600

SECURITY B – TSMC RESTRICTED SECRET

tsmc

Content

PDK

SRAM

Qualification report

Test Line Layout

Automotive

Confidential – Do Not Copy

Document No.

Version

: T-N45-CL-DR-001

: 2.6

Reference Document

T-N45-CL-SP-010-K1

TSMC 45 NM CMOS LOGIC GENERAL PURPOSE SUPERB 1P10M+AL_RDL SALICIDE CU_ELK 0.9V/1.8V PDK

CLN45GS=CLN40G (INCLUDES: CLN45GS 0.9V/2.5V)

T-N45-CM-SP-003-K1

TSMC 45 NM CMOS MIXED SIGNAL RF LOW POWER 1P9M+AL_RDL SALICIDE CU_ELK 1.1&2.5V PDK

(CRN45LP) (INCLUDES: CRN45LP 1.1V/2.5V; CRN45LP 1.1V/1.8V)

T-N40-CM-SP-001-K1

TSMC 40 NM CMOS MIXED SIGNAL RF LOW POWER 1P9M+AL_RDL SALICIDE CU_ELK 1.1&2.5V PDK

(INCLUDES: CRN40LP 1.1V/1.8V)

T-N40-CL-SP-051-K1

TSMC 40 NM CMOS MIXED SIGNAL RF LOW POWER PLUS 1P10M+AL_RDL SALICIDE CU_ELK 1.1&2.5V PDK

(1.1V/1.8V)

T-N45-CL-CL-010

TSMC 45 NM CMOS LOGIC LOW POWER 1P10M SALICIDE CU_LOWK 1.1/1.8V 6T/8T SRAM CELL LAYOUT &

MODEL

T-N45-CL-CL-014

TSMC 45 NM CMOS LOGIC GENERAL PURPOSE SUPERB 1P10M SALICIDE CU_ELK 0.9V 6T/8T SRAM CELL

LAYOUT & MODEL (45GS (=40G), G SRAM)

T-N45-CL-CL-015

TSMC 45 NM CMOS LOGIC GENERAL PURPOSE SUPERB 1P10M SALICIDE CU_ELK 0.9V (0.8V) 6T/8T SRAM

CELL LAYOUT & MODEL (45GS (=40G), GL SRAM)

T-N40-CL-CL-001

TSMC 40 NM CMOS LOGIC LOW POWER 1P10M SALICIDE CU_ELK 6T/8T SRAM CELL LAYOUT & SPICE

MODEL (6T SINGLE PORT SRAM AND 8T DUAL PORT SRAM)

T-000-CL-RP-002

TSMC EMBEDDED SRAM REDUNDANCY IMPLEMENTATION RULE AND ECC GUIDELINE

T-N45-CL-QR-001

TSMC 45 NM CMOS LOGIC LOW POWER 1P7M SALICIDE CU_LOWK 1.1/1.8V QUALIFICATION REPORTFAB12

T-N45-CL-QR-005

TSMC 45 NM CMOS LOGIC LOW POWER 1P7M SALICIDE CU_LOWK 1.1/2.5V QUALIFICATION REPORTFAB12

T-N45-CL-QR-006

TSMC 45 NM CMOS LOGIC LOW POWER 1P9M SALICIDE CU_ELK 1.1/1.8V CUP WIRE BOND PBGA

PACKAGE QUALIFICATION REPORT – 12 INCH FAB

T-N45-CL-QR-010

TSMC 45 NM CMOS LOGIC GENERAL PURPOSE SUPERB 1P10M SALICIDE CU ELK 0.9V/2.5V

QUALIFICATION REPORT-FAB12 (45GS (=40G))

T-N45-CL-QR-011

TSMC 45 NM CMOS LOGIC GENERAL PURPOSE SUPERB 1P10M SALICIDE CU ELK 0.9/1.8V QUALIFICATION

REPORT-FAB12 (45GS (=40G))

T-N40-CL-QR-004

TSMC 40 NM CMOS LOGIC LOW POWER 1P10M SALICIDE CU_ELK 1.1/2.5V QUALIFICATION REPORT-FAB12

(40LP)

T-N40-CL-QR-005

TSMC 45 NM / 40 NM CMOS LOGIC 1P9M CU_ELK CUP WIRE BOND PBGA PACKAGE QUALIFICATION

REPORT-12 INCH FAB

T-N40-CL-QR-027

TSMC 40 NM CMOS LOGIC LOW POWER HVMOS 1P10M SALICIDE CU_LOW K 1.1&2.5V AND HVMOS

(D5G2.5) PROCESS QUALIFICATION REPORT- FAB12

T-N40-CL-QR-031

TSMC 40 NM CMOS LOGIC LOW POWER HVMOS 1P10M SALICIDE CU_LOW K 1.1&1.8V AND HVMOS

(D5G1.8) PROCESS QUALIFICATION REPORT- FAB12

T-N40-CL-QR-043

TSMC 40 NM CMOS LOGIC LOW POWER HVMOS 1P10M SALICIDE CU_LOW K 1.1&2.5V and HVMOS

(D5G2.5) PROCESS QUALIFICATION REPORT-FAB14

T-N40-CL-QR-049

TSMC 40 NM CMOS LOGIC LOW POWER 1P10M SALICIDE CU_LOWK 1.1/2.5V QUALIFICATION REPORTFAB14 (HVMOS, D5G2.5)- FAB14

E-MSS-02-02-024

TSMC TEST LINE LAYOUT USER GUIDELINE

Q-QSM-05-03-221

TSMC AUTOMOTIVE SERVICE FOR WAFER MANUFACTURING

The information contained herein is the exclusive property of TSMC and shall not be distributed, copied, reproduced, or disclosed in

whole or in part without prior written permission of TSMC.

11 of 600

SECURITY B – TSMC RESTRICTED SECRET

tsmc

Confidential – Do Not Copy

Document No.

Version

: T-N45-CL-DR-001

: 2.6

2 Technology Overview

This chapter provides information about the following:

2.1

Semiconductor process (including front-end and back-end features)

2.2

Devices

2.3

Power supply and operation temperature ranges

2.4

Cross-section

2.5

Metallization options

2.1

Semiconductor Process

The process consists of the front-end features and the back-end features.

2.1.1

Front-End Features

Shallow trench isolation (STI)

Used for active isolation to reduce active pitch (OD pitch)

Retrograde twin well CMOS technology on <110> P- substrate (epitaxy wafer) (subtrate resistivity

of 8-12 Ω-cm) for N40G, and on <100> P- substrate (epitaxy wafer) (subtrate resistivity of 8-12 Ωcm) for N45LP/N40LP.

Retrograde twin well CMOS technology

For a low well sheet resistance and enhancement of latch-up behavior (compared to conventionally

diffused wells). Also provides for a good control of short parasitic field transistors.

Triple well, Deep N-Well (optional)

For isolating P-Well from the substrate

Dual gate oxide process

Dual gate oxide LP (1.1V/2.5V or 1.1V/1.8V), GS (0.9V/2.5V,or 0.9V/1.8V)

Triple gate oxide process

Dual core gate oxide and IO gate oxide N45LPG (0.9V/1.1V/1.8V(I/O)) and N40LPG(0.9V/1.1V/3.3V(I/O))

N+/P+ poly gate

Allows symmetrical design of NMOS and PMOS devices

Multiple Vt devices for low leakage or high performance requirements

These devices may be mixed on the same die.

Native devices with dual gate oxide

The information contained herein is the exclusive property of TSMC and shall not be distributed, copied, reproduced, or disclosed in

whole or in part without prior written permission of TSMC.

12 of 600

SECURITY B – TSMC RESTRICTED SECRET

tsmc

Confidential – Do Not Copy

Document No.

Version

: T-N45-CL-DR-001

: 2.6

SRAM cells offering (The cells described here are before shrinkage)

Technology

Cell Size

N45LP/N45LPG-LP

N40LP/N40LP+/N40LPG-LP

HD = 0.299um^2

(Vcc_nom = 1.1V)

HC = 0.374um^2

(Vcc_nom = 1.1V)

HD = 0.299um^2

(Vcc_nom = 1.1V)

HC (HP) = 0.374um^2

(Vcc_nom = 1.0V - 1.1V)

HDDP (HP) = 0.589um^2*

(Vcc_nom = 1.1V)

DP = 0.589um^2

(Vcc_nom = 1.1V)

HCDP (HP) = 0.741um^2

(Vcc_nom = 1.1V)

-DP = 0.589um^2

(Vcc_nom = 1.1V)

HCDP = 0.741um^2

(Vcc_nom = 1.1V)

*HDDP(HP) 0.589um^2 will replace DP 0.589um^2 and share the same implant mask 11N/11P with HC(HP) and

HCDP(HP). Original DP will be kept supporting but not official offering any more. Please refer to SRAM cell doc TN40-CL-CL-001 for HDDP(HP) GDS and more information.

Technology

Process Option

Cell Size

N40G(=N45GS)

G

GL

HD = 0.299um^2

(Vcc_nom = 0.9V - 1.0V)

HC = 0.374um^2

(Vcc_nom = 0.9V - 1.0V)

DP = 0.589um^2

(Vcc_nom = 0.9V - 1.0V)

HCDP = 0.741um^2

(Vcc_nom = 0.9V - 1.0V)

HD = 0.299um^2 (=G)*

(Vcc_nom = 0.9V - 1.0V)

HC = 0.374um^2

(Vcc_nom = 0.8V - 1.0V)

DP = 0.589um^2 (=G)**

(Vcc_nom = 0.9V - 1.0V)

HCDP = 0.741um^2

(Vcc_nom = 0.8V - 1.0V)

**D299 and D589 in N40GL process belong to N40G.

Self-aligned Ni-silicided drain, source, and gate

Silicide is necessary to short N+ and P+ gates; furthermore, it drastically reduces gate and S/D serial

resistance. Self-aligned silicide on source/drain structures allows butting straps with only one minimally

sized contact.

Unsilicided poly and OD resistors

Silicide protection (requires one additional mask, RPO) is used to prevent silicide formation over the active

and poly area.

Varactor

MOS varactor provides 0.9V/1.1V/1.2V/1.8V/2.5V NMOS-in-NW capacitor structure and 0.9V/1.8V/2.5V

PMOS-in-PW capacitor structure.

The information contained herein is the exclusive property of TSMC and shall not be distributed, copied, reproduced, or disclosed in

whole or in part without prior written permission of TSMC.

13 of 600

SECURITY B – TSMC RESTRICTED SECRET

tsmc

2.1.2

Confidential – Do Not Copy

Document No.

Version

: T-N45-CL-DR-001

: 2.6

Back-End Features

Tungsten contact connecting poly or OD to first metal level

Three to ten Cu metal levels, plus last metal level in Al pad.

Two kinds of inter-layer metal:

Mx: First Inter-layer Metal, W/S=0.07μm/0.07μm.

My: Second Inter-layer Metal, W/S=0.14μm/0.14μm.

Four kinds of top-layer metal:

Mz (TM): top metal pitch is 0.8μm (W/S=0.4μm/0.4μm).

My (2XTM): top metal pitch is two times of Mx pitch (W/S=0.14μm/0.14μm).

Mr: top metal pitch is 1.0μm (W/S=0.5μm/0.5μm)

Mu: top metal pitch is 3.0μm (W/S=2μm/1μm)

AlCu pad layer can be used as a redistribution layer (AP RDL) option.

One or two thick last (top) Cu metal layers at a relaxed pitch for power, clock, busses, and major

interconnect signal distribution

Tight pitch levels for routing on thin Cu for the other metal levels below the thick level

Chemical mechanical polishing (CMP) for enhanced planarization (STI, contact, metals, vias,

passivation)

Dual damascene copper interconnection, for metal-2 to the last (top) metal

ELK inter-metal dielectric for thin metal

Metal oxide metal (MOM) capacitor

Use metal lines to design metal capacitor. The device does not require any additional mask.

High-Q copper inductor for RF process:

Have Mz, Mu process for inductor metal.

Wire bond or flip chip terminals

T-N45-CL-DR-003: TSMC WIRE BOND, EUTECTUC FLIP CHIP, AND INTERCONNECTION DESIGN

RULE

For Lead-Free Flip Chip, please refer to section 1.2, Reference Document.

Electrical fuse

The IP of electrical fuse is provided. Please contact your account manager to get the related information.

The information contained herein is the exclusive property of TSMC and shall not be distributed, copied, reproduced, or disclosed in

whole or in part without prior written permission of TSMC.

14 of 600

SECURITY B – TSMC RESTRICTED SECRET

tsmc

2.2

Confidential – Do Not Copy

Document No.

Version

: T-N45-CL-DR-001

: 2.6

Devices

The technology provides multiple Vt devices, and optional thin and thick gate oxide native devices.

Table 2.2.1

Available Vt in each technology

Core

Technology

N45LP/N40LP

N40LP+

N45LPG

High Vt

N/A

STD Vt

Low Vt

Ultra Low Vt Plus

N/A

N/A

Native

N/A

Varactor*

MOM

Inductor

N40LPG

(N40 LPG-LP only)

(N40 LPG-G only)

N/A

(N40 LPG-LP only)

N40G (0.9V)

N/A

* Please refer to section 4.5.26, MOS Varactor Layout Rules (VAR), in details.

The information contained herein is the exclusive property of TSMC and shall not be distributed, copied, reproduced, or disclosed in

whole or in part without prior written permission of TSMC.

15 of 600

SECURITY B – TSMC RESTRICTED SECRET

tsmc

Confidential – Do Not Copy

Document No.

Version

: T-N45-CL-DR-001

: 2.6

2.3

Power Supply and Operation Temperature

Ranges

Table 2.3.1

Power Supplies

N45LP/N40LP

Normal

*Max

power

power

supply

supply

Core (thin

oxide)

I/O (thick

oxide)

2.5V

overdrive

to 3.3V

2.5V

underdrive

to 1.8V

1.8V

underdrive

to 1.5V

N40LP+

Normal

*Max

power

power

supply

supply

Technology

N45LPG/N40LPG

Normal

*Max

power

power

supply

supply

5.5V**

1.1V(LP),

0.9V(G)

1.8V

(N45LPG)

N/A

3.3V

(N40LPG)

N/A

1.26(LP),

1.05V(G)

1.98V

(N45LPG)

N/A

3.63V

(N40LPG)

N/A

3.3V

3.63V

N/A

1.98V

1.8V

1.98V

1.65V

(N40LP)

NA

NA

1.1V

1.26V

1.1V

1.26V

1.8V

1.98V

N/A

N/A

2.5V

2.75V

2.5V

2.75V

N/A

N/A

N/A

N/A

5V**

5.5V**

5V**

3.3V

3.63V

1.8V

1.5V

(N40LP)

N40G

Normal

power

supply

*Max

power

supply

0.9V,

1.1V,

1.2V(OD_12) 1.32V(OD_12)

1.8V

1.98V

2.5V

2.75V

N/A

N/A

N/A

N/A

N/A

3.3V

3.63V

N/A

N/A

1.8V

1.98V

N/A

N/A

1.5V

1.65V

** Only drain side can be applied to 5V. The other terminals can only be applied to 2.5V (HVMOS_25 for

N45LP/N40LP/N40LP+) or 1.8V (HVMOS_18 for only N40LP).

The operation temperature range is -40C to 125C (junction temperature).

* Maximum power supply voltage means variation upper limit of product operation voltage.

o p e r a ti o n

M a x i m u m p o w e r s u p p ly v o lta g e

v o lta g e

N o m ina l p o w e r

s u p p ly v o lta g e

o p e r a ti o n ti m e

The information contained herein is the exclusive property of TSMC and shall not be distributed, copied, reproduced, or disclosed in

whole or in part without prior written permission of TSMC.

16 of 600

SECURITY B – TSMC RESTRICTED SECRET

tsmc

2.4

Confidential – Do Not Copy

Document No.

Version

: T-N45-CL-DR-001

: 2.6

Cross–section

Cross section (1P10M as inter Mx, top Mz(TM))

P a s s iv a tio n - 2

A P

P a s s iv a tio n - 1

M 1 0 (C u )

M 10

U S G

M 1 0 W /S = 0 .4 /0 .4

V 9 W /S = 0 .3 6 /0 .3 4

V 9

M 9 (C u )

M 9

U S G

M 9 W /S = 0 .4 /0 .4

V 8 W /S = 0 .3 6 /0 .3 4

V 8

M 8 W /S = 0 .0 7 /0 .0 7

M 8

~

~

E LK

M 3 W /S = 0 .0 7 /0 .0 7

M 3

M 3 (C u )

V 2 W /S = 0 .0 7 /0 .0 7

M 2 W /S = 0 .0 7 /0 .0 7

M 2 (C u )

E LK

V 2

M 2

E LK

V 1 W /S = 0 .0 7 /0 .0 7

P O

M 1 W /S = 0 .0 7 /0 .0 7

M 1 (C u )

W /S = 0 .0 4 /0 .1 0 (o n S T I)

0 .0 4 /0 .1 4 (o n O D )

C O

P o ly

V 1

E LK

M 1

W /S = 0 .0 6 /0 .0 8

W - P lu g

P o ly

O D W /S = 0 .0 6 /0 .0 8

S a lic id e

S TI

Figure 2.4.1 Cross-section for 1P10M_7x2z

The information contained herein is the exclusive property of TSMC and shall not be distributed, copied, reproduced, or disclosed in

whole or in part without prior written permission of TSMC.

17 of 600

SECURITY B – TSMC RESTRICTED SECRET

tsmc

Document No.

Version

Confidential – Do Not Copy

: T-N45-CL-DR-001

: 2.6

Cross section (1P10M as inter Mx, top My(2XTM))

P a s s iv a tio n - 2

AP

P a s s iv a tio n - 1

M 1 0 (C u )

M 10

USG

M 1 0 W /S = 0 .1 4 /0 .1 4

V 9 W /S = 0 .1 4 /0 .1 4

V9

M 9 (C u )

M 9

USG

M 9 W /S = 0 .1 4 /0 .1 4

V 8 W /S = 0 .1 4 /0 .1 4

V8

M 8 W /S = 0 .0 7 /0 .0 7

M 8

~

~

ELK

M 3 W /S = 0 .0 7 /0 .0 7

M 3

M 3 (C u )

ELK

V2

V 2 W /S = 0 .0 7 /0 .0 7

M 2 W /S = 0 .0 7 /0 .0 7

M 2 (C u )

M 2

ELK

V 1 W /S = 0 .0 7 /0 .0 7

M 1 W /S = 0 .0 7 /0 .0 7

M 1 (C u )

P O W /S = 0 .0 4 /0 .1 0 (o n S T I)

0 .0 4 /0 .1 4 (o n O D )

M 1

C O W /S = 0 .0 6 /0 .0 8

P o ly

V1

ELK

W - P lu g

P o ly

O D W /S = 0 .0 6 /0 .0 8

S a lic id e

STI

Figure 2.4.2 Cross-section for 1P10M_7x2y

The information contained herein is the exclusive property of TSMC and shall not be distributed, copied, reproduced, or disclosed in

whole or in part without prior written permission of TSMC.

18 of 600

SECURITY B – TSMC RESTRICTED SECRET

tsmc

Document No.

Version

Confidential – Do Not Copy

: T-N45-CL-DR-001

: 2.6

Cross section (1P10M as inter Mx/My, top Mz(TM))

P a s s iv a tio n - 2

AP

P a s s iv a tio n - 1

M 1 0 (C u )

M 10

M 1 0 W /S = 0 .4 /0 .4

V9

V 9 W /S = 0 .3 6 /0 .3 4

USG

M 9 (C u )

M9

M 9 W /S = 0 .4 /0 .4

V 8 W /S = 0 .3 6 /0 .3 4

V8

M 8 (C u )

M8

M 8 W /S = 0 .1 4 /0 .1 4

V 7 W /S = 0 .1 4 /0 .1 4

V7

M 7 (C u )

M7

M 7 W /S = 0 .1 4 /0 .1 4

V 6 W /S = 0 .1 4 /0 .1 4

V6

LK

M6

ELK

M6

M 6 W /S = 0 .0 7 /0 .0 7

~

~

-------------------------------------

LK

-------------------------------------

M 2 (C u )

M 2 W /S = 0 .0 7 /0 .0 7

USG

M2

ELK

V 1 W /S = 0 .0 7 /0 .0 7

M 1 W /S = 0 .0 7 /0 .0 7

M 1 (C u )

P O W /S = 0 .0 4 /0 .1 0 (o n S T I)

0 .0 4 /0 .1 4 (o n O D )

P o ly

V1

M1

C O W /S = 0 .0 6 /0 .0 8

ELK

W - P lu g

P o ly

O D W /S = 0 .0 6 /0 .0 8

S a lic id e

STI

Figure 2.4.3 Cross-section for 1P10M_5x2y2z

The information contained herein is the exclusive property of TSMC and shall not be distributed, copied, reproduced, or disclosed in

whole or in part without prior written permission of TSMC.

19 of 600

SECURITY B – TSMC RESTRICTED SECRET

tsmc

Confidential – Do Not Copy

Document No.

Version

: T-N45-CL-DR-001

: 2.6

Cross section (1P10M as inter Mx, top Mr)

P a s s iv a tio n - 2

A P

P a s s iv a tio n - 1

M 1 0 (C u )

M 10

U S G

M 1 0 W /S = 0 .5 /0 .5

V 9 W /S = 0 .4 6 /0 .4 4

V 9

M 9 (C u )

M 9

U S G

M 9 W /S = 0 .5 /0 .5

V 8 W /S = 0 .4 6 /0 .4 4

V 8

M 8 W /S = 0 .0 7 /0 .0 7

M 8

~

~

E LK

M 3 W /S = 0 .0 7 /0 .0 7

M 3

M 3 (C u )

M 2 W /S = 0 .0 7 /0 .0 7

M 2 (C u )

E LK

V 2

V 2 W /S = 0 .0 7 /0 .0 7

M 2

E LK

V 1 W /S = 0 .0 7 /0 .0 7

M 1 W /S = 0 .0 7 /0 .0 7

P O

M 1 (C u )

W /S = 0 .0 4 /0 .1 0 (o n S T I)

0 .0 4 /0 .1 4 (o n O D )

P o ly

C O

V 1

E LK

M 1

W /S = 0 .0 6 /0 .0 8

W - P lu g

P o ly

O D W /S = 0 .0 6 /0 .0 8

S a lic id e

S TI

Figure 2.4.4 Cross-section for 1P10M_7x2r

The information contained herein is the exclusive property of TSMC and shall not be distributed, copied, reproduced, or disclosed in

whole or in part without prior written permission of TSMC.

20 of 600

SECURITY B – TSMC RESTRICTED SECRET

tsmc

Document No.

Version

Confidential – Do Not Copy

: T-N45-CL-DR-001

: 2.6

Cross section (1P10M as inter Mx, top Mz/Mu (TM))

P a s s iv a tio n - 2

A P

P a s s iv a tio n

M 1 0 (C u )

1

M 10

U S G

M 1 0 W /S = 2 .0 /1 .0

V 9 W /S = 0 .3 6 /0 .3 4

V 9

M 9 (C u )

M 9

U S G

M 9 W /S = 0 .4 /0 .4

V 8 W /S = 0 .3 6 /0 .3 4

V 8

M 8 W /S = 0 .0 7 /0 .0 7

M 8

~

~

E LK

M 3

M 3 W /S = 0 .0 7 /0 .0 7

M 3

(C u )

E LK

V 2

V 2 W /S = 0 .0 7 /0 .0 7

M 2

M 2 W /S = 0 .0 7 /0 .0 7

M 2

(C u )

E LK

V 1 W /S = 0 .0 7 /0 .0 7

M 1

M 1 W /S = 0 .0 7 /0 .0 7

P O

W /S = 0 .0 4 /0 .1 0 (o n S T I)

0 .0 4 /0 .1 4 (o n O D )

O D W /S =

V 1

(C u ) C O

P o ly

E LK

M 1

W /S =

0 .0 6 /0 .0 8

W P lu g

P o ly