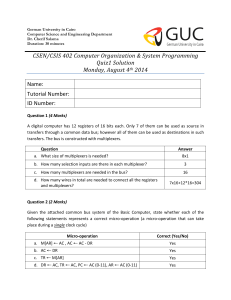

Assignment 1–COMPUTER ORGANIZATION AND ARCHITECTURE_CSF201, Odd Semester 2023 Your Name: SAP ID: Branch: Instructions There is 10 question in this assignment. This evaluation instrument, if submitted after due date, will not be evaluated, and a score of zero will be awarded, if it is a graded instrument. Email/paper/other modes of submissions will not be accepted. Upload a pdf version of this document. Copied assignments will fetch a score of zero for all parties involved Due Date: 9:00 pm, September 01, 2023. Submitting this Assignment You will submit (upload) this assignment in MS Teams. Name this document as A1_CSF201 _SAP ID.pdf. Grading: 5 points Question 1: Give a brief historical perspective of computers covering the following points Features of each generation of computers (1-5) Drawbacks of previous generation that were overcome in the upcoming generation Question 2: Explain the basic functions of computer. Question 3: What is Micro-operations, Register Transfer and Register Transfer Language? Question 4: Show the block diagram of the hardware the implements the following register transfer statement: y: R2 <- R1 y’T2: R1 R2 Question 5: Implement 16:1 Mux using 2:1 Mux’s. Question 6: Draw a diagram of a bus system for four registers of 4 bit each that, uses three-state buffers and a decoder instead of the multiplexers. Assignment 1–COMPUTER ORGANIZATION AND ARCHITECTURE_CSF201, Odd Semester 2023 Question 7: A digital computer has a common bus system for 32 registers of 16 bits each. The bus is constructed with multiplexers. a. How many selection inputs are there in each multiplexer? b. What size of multiplexers are needed? c. How many multiplexers are there in the bus? Question 8: Design a 4-bit combinational circuit decrementer using four full-adder circuits. Question 9: Derive a combinational circuit that selects and generates any of the 16 logic functions listed in Table. Question 10: Show the hardware that implements the following statement. Include the logic gates for the control function and a block diagram for the binary counter with a count enable input.