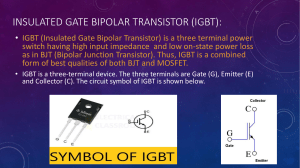

PT-IGBT PSpice Model with New Parameter Extraction for Life-Time and Epy Dependent Behaviour Simulation F. Frisina, R. Letor Co.Ri.M.Me.Research Laboratories SGS-Thomson Microelectronics Stradale Promosole, 50 - 95 121 Catania, Italy Tel.: +39 95 599381 Fax: +39 95 599099 S . Musumeci, A. Raciti, M. Sardo Dept. of Electrical Electronic and Systems Engineering University of Catania Viale Andrea Doria, 6 - 95125 Catania, Italy Tel.: +39 95 339535 Fax: +39 95 330793 Abstract. IGBT PSpice models recently proposed do not give satisfactory simulation results of the behaviour of Punch-Through (PT) IGBTs. The reason can be attributed to the incorrect modelling of the particular epitaxial structure of the intrinsic PNP of the IGBT. In particular, the most critical behaviour to simulate accurately is the turn-off since such transient is strongly influenced by the life time of the minority carriers and the reapplied voltage on the collector of the bipolar part of the IGBT. An improved fGBT PSpice model is presented aiming to overcome the incompleteness of other models. A detailed procedure describing the parameter extraction of the model by qew methods is also developed. The proposed model is validated comparing several simulation runs with experimental traces on both static and dynamic conditions for both fast and slow IGBTs at different working conditions. I. INTRODUCTION Power Electronics designers often use circuit simulator packages to study and predict the behaviour of traditional or new circuits. When the simulation study is devoted to know power losses in the circuit, switches can not be considered as ideal elements but they must be replaced by suitable models of the devices accounting for the actual phenomena during both on-state and switching behaviours. In recent years, a lot of models for power semiconductor devices, specially BJTs and Power MOSFETs, have been proposed but with the growing use of IGBTs in switchmg power converters attention is focusing on the development of models for these interesting devices. A few of papers aiming to develop IGBT models are dedicated to the well-established PSpice simulator package, but most of them fail the goal to take into account for the non ideal structure and behaviour of the device. In [l] an IGBT model is presented where none relevance is given to the Early effect in the PNP transistor part of the IGBT and to the short channel effect in the MOSFET part. Moreover the PNP 0-7803-3500-7/96/$5.00 0 1996 IEEE base structure and also the high injection conditions are not considered. In turn, in this model the parameters used to define the current gain and transconductance for the internal transistors, being essentially intended to represent such elements as ideal devices, do not allow to model exactly the behaviour of the IGBT in all current and voltage conditions. Some improvement is proposed in [2] and [3], where high injection conditions are modeled. In recent works [4] and [5], some structure dependent behaviours such as Early effect, have been introduced. The aim of this paper is to improve the IGBT PSpice model by introducing also the effects above reported. However, to fulfil the requirements of potential users of simulation packages some remarks must be previously drawn. Generally speaking, the IGBT characterization in the data-sheets of producers is not sufficient to describe the device behaviour by using the models already available. Furthermore, the physical structure of the devices is not always available and in most cases it changes strongly depending on the manufacturer and the device type. Consequently, to encounter the needs of users, a suitable way to develop “easy-to-use” IGBT models is to avoid the definition of too many physical parameters, and when necessary, to provide a new characterization methodology giving an easy parameters extraction. 11. INFLUENCE OF THE PHYSICAL STRUCTURE AND WORKING CONDITIONSON STATIC AND DYNAMIC BEHAVIOUR OF IGBTS The presence of a N’ buger-layer in the base of the bipolar part of the IGBT, which structure is shown in Fig. 1, leads to unusual I-V characteristics for the internal PNP, since this layer acts as a barrier to the collector-base depletion layer which modulates the effective base width, and then the current gain of the transistor. The macroscopic effect is that the static I-V characteristics present, as shown in Figure 2, a sttong Early effect until the emitter-collector 1682 voltage reaches a 'typical value VN-,when the N- drift region is completely depleted. Since the PNP constitutes the output stage of the IGBT, this effect also appears on the I-V characteristics of the complete device. As a combined result of the above considerations, both the MOS part and the bipolar part of the IGBT turn-off current are strongly influenced by the clamp voltage. III. THE PROPOSED PT-IGBT PSPICE MODEL A . Static characteristics The basic representation of an IGBT device considers a Darlington connection between an MOS device, acting as a driver, and a PNP transistor as output device, as shown in Fig. 4. --I intrinsic ' PaverMOSFET COLLECTOR Fig. 1. Cross section of a PT-IGBT. + ~ ~J m .;\ ci PAP tramistor I GAT%: EMITI'ER I Fig. 4. Basic equivalent circuit ofthe IGBT. + I I VN- VCE Fig. 2. Typical I-V characteristics for the internal bipolar transistor of the IGHT. Loolung at dynamic behaviour, it is well known that the IGBT turn-off on inductive load allows to determine the two components of its total current and, namely, the MOS current IMosand the PNP current ZpW. By performing several tests at different clamp voltages, it is easy to observe that both these currents are strongly related to the voltage across the collector-(emitterterminals, as shown in Figure 3. - The most general equation used to represent the two contributions to the total current of an IGBT is the following: where P f l p ~V&) , is the bipolar transistor gain expressed as a function of either the bipolar current and the applied collector-emitter voltage. As a first approximation, a square law is generally accepted to model the current of the MOS part. However, taking into account for the influence of the drain-source voltage on the drain current, a corrective empirical term can be considered [7], as shown by this equation: +VCE = ioo\i/div where Kp is the transconductance coefficient, Vth is the threshold voltage, and A is the parameter accounting for the channel length reduction. With referewe to the PNP current component of the IGBT at low v,, voltage (less than v,->, the following approximation can be used: IC = lA/div L i i l l l l i l l l d [.l p .sldivl Fig. 3. Influence of clamp voltage on tum-off IGBT behaviour. Moreover, the dynamic behaviour is also influenced by the PNP transistor structure. In [6] has been shown that minority carriers life-time is a function of the applied voltage. 1683 (3) where Ipm and 1, are the collector and base currents of the PNP transistor, ,& is the peak gain, V, is the Early voltage and IK is the knee current (the collector current at which the gain is half the gkak value). According to the explained considerations, the unusual dual slope I-V output curves can be obtained, from a macroscopic point of view, by considering a voltagecontrolled current source Ibuf, as shown in Fig. 5, which decreases the total current modelled by the intrinsic PSpice bipolar transistor during the simulation stage. recombination for low clamp voltage conditions and a voltage-controlled current souw Ihv simulates recombination for high clamp voltage conditions. Fig. 6 shows the circuit that includes the above elements. COLLECTOR Q Intnnsrc PNP transistor 1 DRAIN EMITTER b IA Fig. 6 . Circuit used to model recombination ofminority carriers. PNP PSpice transistor By considering the Clv capacitor discharges onto a resistance RI, (which has been suitably set to the value of 15 mCl, obtained using PSpice default parameters for the BJT), then its value is determined, once the time constant z of the tail current has been evaluated, by the relation: Rcon Fig. 5. Equivalent circuitfor the modeling of the buffer-layer. The Ibuf generator is enabled only when the emittercollector voltage of the intrinsic PNP transistor (V, voltage in Figure 5 ) exceeds the V i voltage. The evaluation of the amplitude of this current source involves primarily the determination of VN-.Once it is obtained from an analysis of the I-V PNP curves, Ibuf can be calculated by the following expression: (4) and is easily implemented by using the Analog Behavioral Modeling (ABM) feature provided by PSpice [SI. Coefficient C is a term which value must be set to fit simulated curves with experimental data. Vco, is a control voltage that varies according to the following law to enable the attached auxiliary circuit: z c, = - R, The current source Ihv used to model the reduction of the minority carriers life time versus the clamp voltage is defined bY where the transconductance K can be deduced by solving the first order Merential equation for the circuit shown in Fig. 7 and whose details are reported in the parameter extraction section. r I I NV 7 - 1 I Fig. 7. Equivalent circuit used for the calculationof K parameter. Finally, to conclude with the determination of static parameters, a contribution term RONcan be introduced to take into account for the modulated conductance in the drift region. It can be determined from the I-V IGBT c w e s in the saturation region and the detailed definition will be performed in the next sections. B. Dynamic characteristics I ) IC behaviour. An innovative approach is used to model recombination of minority carriers, that means, the tail current at turn-off.The problem is faced in SPICE by the transit time parameter TF, whereas we propose a circuit where the discharge of a fixed capacitor Cl" simulates 2) VGE and V& behaviour. Intemal capacitances of IGBTs can be considered to be similar to those present in a Power MOSFET. For this reason, they are modelled with a constant capacitor for CGEand a strongly variable capacitor, obtained with the connection shown in Fig. 8, for CGD. When a negative voltage is applied to the gate and source terminals of Power MOSFETs, the input capacitance is equal to the oxide capacitance because the source-drift region junction forward biases [9]. Consequently, to model such phenomenon, which can also be observed on IGBTs, a fixed CGD(*aplcapacitor and a switch controlled by the gateemitter voltage are inserted in parallel to the CGE capacitor. The Cm capacitor in parallel with DGDis introduced to obtain a better 1684 this reason, several turn-off commutations at different load cutrent and clamp voltage determined on the IGBT characteristics must be executed. The experimental curves allow to deduce the output curves of intrinsic MOS , and hence the following PSpice parameters: the short-channel parameter LAMBDA, the transconductance coefficient KP, the threshold voltage VTU. LAMBDA is easily extracted from the slope of the I-V MOS curves in the saturation region. Once this parameter is known, KP and VTU can be evaluated from fit at high clamp voltage of experimental capacitance variation curve with the simulated one. f r the corrected transfer curve 0 Fig. 8. Equivalent circuitused to obtain CODand CCZ. Finally, based on the above discussion the improved PTIGBT PSpice model is completed and its equivalent circuit is reported in Figure 9. \ GJ of the intrinsic MOS. In the same extent, to obtain PNP parameters, intrinsic PNP curves are needed. Then, several turn-off commutations with the MOS current kept constant, must be executed. The following parameters, already defined to model the bipolar part of the IGBT, should be identlfed: the peak gain BF, the Early voltage VAF, the knee current IW. VAF is determined from the higher slope I-V curves in the linear region, whle BF and I W are extracted from the curve (pFversus Id. Finally, to determine RON,measurements in the saturation region must be executed, so determining two points (Icl, VCEI) and (Icz, VCEZ).RONcan be easily calculated by using the following relation: B. Dynamic parameters. Dynamic parameters can be classified for convenience in the following way: 0 0 Fig. 9. Equivalent circuit ofthe improved PT-IGBT PSpice model. IV. EXTRACTION PROCEDURE OF THE MODEL PARAMETERS A. Static parameters. Since internal base terminal of the bipolar part of the IGBT is not externally available, a test to evidentiate the contributions to the total current must be performed. Accordingly with the above discussion, the static parameters extraction procedure requires switching waveforms at turnoff. A suitable technique is used to obtain both MOS and bipolar transistor curves starting from IGBT static characteristics and turn-offwaveforms. Such a procedure can be summarized in the following steps: 0 I-V static characteristics in the range where the IGBT has to be modelled, are needed. To extract MOS part parameters, intrinsic MOS I-V curves are needed. For parameters influencing VGEand VCEbehaviour; parameters influencing ICbehaviour. The former ones are: the fixed CGEcapacitance; the highly variable CGDcapacitance which is modelled with a capacitor CGD(,,,a5)connected in series with a diode; the gate terminal resistance RG. The capacitance values are calculated from a study of the gate-charge curve, while only Rc has to be determined from the time constant of the VGE voltage transient during the commutation. In details, CGEvalue is obtained from a measurement of the VGEslope before the beginning of the Miller effect in the gate-charge curve by: (9) where Im is the constant current generator used to obtain the curve. CmfmMlcan be also obtained from the gate-charge curve by this equation: 1685 STGH30N60 IC [AI 35 30 25 20 To include the capacitance variation on CGDthe diode variable capacitance q# available in PSpice has been connected to The following relation, whose parameters CJO, M, and VJ should be determined to fit with the experimental data, has been used: C j ( V )= 15 10 5 0 CJO 0 100 200 Vce Vge: STEP 0.5V OFFSET 5V 300 400 500 M Fig. 10. Comparison of experimental ( 0 ) and simulated (-) I-V static characteristicsof STGB30N60 IGBT. For the calculation of K parameter defined in (7), an analysis of the turn-off tail current at high clamp voltage must be executed. By using the solution of the differential equation for the circuit shown in Figure 7, K can be determined as follows: 40 30 20 10 0 where I,, is the initial tail current, t* is the time instant at which this current is half the initial value, z is the time constant used in (6), & is the current gain at the specified conditions, and Vclomp is the clamp voltage. 0 50 100 150 Vce Vge: STEP 0.5V 200 250 300 M OFFSET 4.5V Fig. 11. Comparison of experimental ( 0 ) and simulated (-) I-V static characteristics of STGH20N60 IGBT. V. EXPERIMENTAL VALIDATION The proposed PT-IGBT model has been validated on various SGS-Thomson devices. Aiming to compare simulation with actual performances in Fig. 10 and 11 are reported the I-V static characteristics for a STGH30N60 and a STGH20N60 IGBT. As can be observed, the simulated results are in good agreement with the experimental data. The model has been also proved on switching behaviours. In Figures from 12 to 20 are reported the experimental traces as well as the simulation runs relative to turn-off and turn-on behaviours at different clamp voltages on inductive load. Since turn-on behaviour is principally influenced by the MOS part, while turn-off waveforms allow to distinguish between MOS current and bipolar current, only one turn-on commutation has been reported. The freewheeling diode has been modeled by using the diode model presented in [lo]. The close correlation between predicted and simulated behaviours is evident and gives validity to the proposed approach. VI. CONCLUSION The aim of the present work was to improve the IGBT macromodel used in PSpice simulator. A scan of the recent models presented in literature has been usell to evidentiate the lack of specific effects present in IGBT behaviours. An attempt to complete the macromodel with such effects has been developed, and the model proposed has been validated by comparison of simulation results with experimental traces. The close correlation of static and dynamic behaviours has been demonstrated, so giving consistence and effectiveness to the proposed model. 1686 STGH30N60 STGH20N60 c [AI 12 10 10 ncreasing Vclamp 8 15 6 IO 4 2 5 0 I 0 t [1pddiv] t [400nsldiv] -2 Fig. 12. Collector current during tum-offtransients Fig. 15. Collector current duringtum-off transient. STGH30N60 STGH20N60 Lke [VI 500 r I I I I I 1 200 100 ----0 i t [Ipddiv] I t [4OOnsldiv] Fig. 13. Collector voltage duringtum-offtransients Fig. 16. Collector voltage during tum-offtransient. STGH30N60 be M STGH20N60 Vge 16 I !O M I I I I I I I I 14 15 12 IO 10 8 5 6 4 0 ncreasing Vclamp 2 -5 0 t [Ipddiv] t [400nsldiv] Fig. 14. Gate voltage during tum-off transient?. Fig. 17. Gate voltage duringtum-off transient. 1687 I I REFERENCES STGH30N60 Jse M I I I I 1 I I I [l] F. F. Protiwa, B. Rasch and B. Arlt, “IGBT Model for PSpice,” Power Conversion Proceedings, Munich, Germany, pp. 445-456, June 1994. I [2] Z. Shen and T. P. Chow, “Modeling and Characterization of the Insulated Gate Bipolar Transistor (IGBT) for SPICE Simulation,” Proceedings of the 5* ISPSD, Seattle, Washington, USA, pp. 166-170,1993. and M. [3] F. Mihalic, K. Jezemik, K. Krischnan Rentmeister, “IGBT SPICE Model,” IEEE Trans. on Industrial Electronics, vol. 42, N. 1, pp. 98-105, February 1995. t [40nsldiv] Fig. 18. Gate voltage during tum-on transient. STGH30N60 I [4] J. Pilacinski, “A Method for Determining the Parameters of Power MOSFET and IGBT Transistor Models Applied in the PSpice Program,” Proceedings of the 6” EPE Conference, Sevilla, Spain, pp. 1268-1272, September 1995. [5 T. Bonafe, S. El Baroudi, F. Bernot and A. Berthon, “ IGBT Model for Power Electronics Simulation,” Proceedings of the 6” EPE Conference, Sevilla, Spain, pp.1141-1145, September 1995. [6] A.F. Hefner, JR, “Modeling Buffer Layer IGBTs for Circuit Simulation,” IEEE Trans. on Power Electronics, vol. 10, N.2, pp. 111-123, March 1995. t [MO nsldiv] [7] P. Antognetti and G. Massobrio, “Semiconductor Device Modelling with SPICE,” McGraw-Hill, New York, USA, 1988. Fig. 19. Collector current during tum-on transient [8] PSpice Circuit Analysis Manual, MicroSim Corp., Imine, CA, USA, July 1994. STGH30N60 M J- 120 100 [9] I. Budihardjio and P.O. Lauritzen, “The Lumped-Charge Power MOSFET Model, Including Parameter Extraction,” IEEE Trans. on Power Electronics, vol. 10, N.3, pp. 379-387, May 1995. [lo] K.J. Tseng, C.F. Foo and P.R. Palmer, “Implementing Power Diode Models in SPICE and Saber,” PESC ‘94 Conf. Rec., Taipei, Taiwan, pp.59-63, June 1994. 80 60 40 20 0 t [400nsldiv] Fig. 20. Collector voltage during tum-on transient. 1688