Single Miller Compensation using Inverting Current

Buffer for Multi-stage Amplifiers

Annajirao Garimella, M. Wasequr Rashid and Paul M. Furth

Klipsch School of Electrical and Computer Engineering

New Mexico State University, Las Cruces, NM 88003 USA

{annaji, wasequr, pfurth}@nmsu.edu

Abstract—A novel single Miller frequency compensation

topology utilizing a current mirror as an inverting current

buffer (SMCICB) for multi-stage amplifiers is proposed. An

effective method for accurate placement of the Left-Half-Plane

(LHP) zero, introduced by the current buffer is detailed. The

SMCICB network effectively cancels the pole at output node,

resulting in a single-pole system. This topology does not

introduce additional transistors and static power dissipation. As

a design example, we simulated a four-stage amplifier driving a

25kΩ//125-pF load, achieving 8.2MHz gain-bandwidth product,

with 80µA of quiescent current and ±1.5Vpower supplies in a

0.5µm ON Semi 2P3M process CMOS. Simulation results, in

good agreement with theoretical analysis, validate the proposed

SMCICB scheme.

Index Terms------Single Miller Compensation, Inverting Current

Buffer, LHP Zero, Multi-stage amplifier.

I.

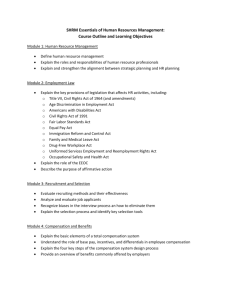

Figure 1. Single Miller Capacitor Feedforward Frequency Compensation

amplifier (SMFFC) topology [1]-[2].

INTRODUCTION

As supply voltages scale down with advanced process

nodes, low voltage, high gain amplifiers are realized by

cascading multiple gain stages. However, each gain stage

inevitably introduces low-frequency poles which require

additional frequency compensation capacitors for stability.

For this purpose, compensation of multi-stage amplifiers

using the single Miller compensation (SMC) capacitor

technique has been introduced [1]-[4]. This technique

employs only a small compensation capacitor, reducing the

area of the amplifier significantly, while improving smallsignal and large-signal amplifier characteristics.

The topology of a single Miller capacitor feedforward

frequency compensation amplifier (SMFFC) [1] is shown in

Fig. 1. Prior to compensation, with large capacitive loads, the

dominant poles p1 at the output of the first stage and at the

output node p3 are situated very close to each other. SMC

capacitor CC is used to effectively split the poles, moving p3

to higher frequencies. In addition to SMC, additional

feedforward transconductance stage gmf1 is used to introduce a

Left-Half-Plane (LHP) zero zLHP, to effectively cancel the

pole p3. However, the implementation of transconductance

stage gmf1 entails an additional differential pair, which

978-1-4244-5309-2/10/$26.00 ©2010 IEEE

Figure 2. Topology of single Miller capacitor compensation with nulling

resistor [3].

increases static power consumption. Also, this topology

introduces a non-dominant Right-Half-Plane (RHP) zero due

to the feedforward path created by the SMC capacitor CC at

high frequencies.

Other SMC topologies exist. The topology of a single

Miller compensation capacitor with nulling resistor [2] is

shown in Fig. 2. In this topology, nulling resistor RC in series

with SMC capacitor CC is used to move the RHP zero into the

LHP for improved stability. In [3]–[4], the authors use a

common-gate amplifier as a positive current buffer in series

with the SMC network to introduce a LHP zero.

1579

A. Contributions of This Work

To this end, we propose a novel Single Miller

Compensation topology using an Inverting Current Buffer

(SMCICB) as shown in Fig. 3. The inverting current buffer

gmCB, in series with the SMC capacitor CSMC, forms a LHP

zero. A simple and effective technique to move the LHP zero

to a desired location is proposed and illustrated in Section II.

This topology does not require any additional transistors; a

simple current mirror that is inherent to the first gain stage is

used to implement the inverting current buffer. Compact

pole-zero and phase margin equations are detailed.

The rest of the paper is organized as follows. The topology

of the proposed SMC network and circuit implementation

details are discussed in Section III. Simulation results are

shown in Section IV, followed by conclusions in Section V.

II.

Figure 3. Small-signal model of Four-Stage Amplifier using Proposed Single

Miller Compensation with Inverting Current Buffer (SMCICB) Topology.

CANCELLATION OF THE MILLER RHP ZERO

ωZ = +

As illustrated in Fig. 4(a), in addition to pole splitting,

Miller capacitor CC forms a feedforward path between nodes

A and B, resulting in a RHP zero. As shown in Fig. 4(b), this

RHP zero is moved to the LHP, by choosing an appropriate

value of the nulling resistor RC [5]-[6]. Similarly a current

buffer or a voltage buffer can be used to obviate a RHP zero

[7].

A. Positive Current Buffer

As shown in Fig. 4(c), a positive current buffer,

implemented with a common-gate amplifier transistor gmCG,

can be used to obviate the feedforward path and introduce a

LHP zero at ω Z = − g mCG / CC . This cascode compensation

topology is also known as Ahuja compensation [5]-[10].

B. Inverting Current Buffer

As shown in Fig. 4(d), an inverting current buffer gmCB [8],

[11]-[13] can be used in series with compensation capacitor

CC to introduce a LHP zero at

ω Z = − g mCB / CC

(1)

Often LHP zeros are used to cancel poles and improve

phase response. To make the LHP zero more dominant, either

the value of the transconductance of the inverting current

buffer gmCB, (often implemented using a current mirror) or the

compensation capacitance CC has to be modified. However

changing these values for a given design significantly affects

other small signal and large signal parameters and may not

form a feasible solution.

We propose a simple and effective solution for accurately

placing the current buffer LHP zero. A resistor RSMC can be

placed in series with the compensation capacitor CSMC,

similar to a nulling resistor as shown in Fig. 4(e). The new

location of the LHP zero is given by

1

1

ωZ = −

(2)

≈−

C SMC (1/g mCB + RSMC )

RSMC C SMC

The significance of adding resistor RSMC is illustrated in Fig.

5, in which the zero moves to lower frequencies as RSMC

increases. Similarly, a resistor can be used in series with the

positive current buffer gmCG in Fig. 4(c) to adjust the location

of the LHP zero created by the positive current buffer [13].

g mB

CC

ωZ ≈ −

1

RCCC

ωZ = −

gmCG

CC

ωZ = −

g mCB

CC

ωZ ≈ −

1

RSMC C SMC

Figure 4. Cancellation techniques for Miller RHP zero: (a) Miller

compensation (b) Miller compensation with nulling resistor (c) Ahuja

cascode compensation (d) Inverting current buffer compensation (e) Resistor

RSMC in series with Inverting current buffer for transforming the location of

zero. Equations for the zeros are also given.

If RSMC = 0

g

ωZ = − mCB

C SMC

If g mCB RSMC >> 1

ωZ ≈ −

1

RSMC CSMC

Figure 5. Significance of RSMC: Diagram illustrating the movement of the

inverting current buffer zero as a function of RSMC.

III.

PROPOSED SINGLE MILLER COMPENSATION TOPOLOGY

The proposed single Miller compensation with inverting

current buffer (SMCICB) topology is shown in Fig. 3. The

circuit implementation in a low-voltage four-stage pseudoclass AB amplifier is shown in Fig. 6. The parameters gmi, Ri,

Ci and vi represent the transconductance, output resistance,

1580

Figure 6. Schematic of the proposed SMCICB network implemented in a low-voltage four-stage pseudo class AB amplifier.

Av (s ) ≈ ADC

(1 + sRSMC C SMC )(1 + s / ω Z ,non−dom )

(1 + sR1CSMC g m 2 R2 g m3 R3 )(1 + s(R1C1 + R2C2 )RSMC [R1 R2 g m2 R3 g m3 ]−1 )(1 + sRL C L )

(3)

lumped parasitic capacitance, and voltage associated with the

⎞

⎛ ω

⎛ ω

⎞

⎛ω

⎞

⎛ω

⎞

ith stage whereas RL and CL represent the load resistance and PM ≈ 90D − tan −1 ⎜⎜ ωGBW ⎟⎟ + tan −1 ⎜⎜ ω GBW ⎟⎟ − tan −1 ⎜⎜ ωGBW ⎟⎟ ≈ tan −1 ⎜⎜ ω P2 ⎟⎟ (9)

⎝ P2 ⎠

⎝ PL ⎠

⎝ GBW ⎠

⎝ Z ,SMCICB ⎠

load capacitance, respectively. The proposed compensation

network consisting of CSMC and RSMC is connected between The phase margin with RSMC, as seen from Fig. 8 is above 80⁰,

nodes v3 and vx. The inherent current mirror formed by M3- indicating a single-pole system.

M4, which are part of the differential input stage (M0-M5), is

used as an inverting current buffer gmCB. Common-source

amplifiers M6 and M8 form the second and third inverting gain

stages. An additional transconductance stage gmf is used

between the output of first stage v1 and the final output node

vout. Transistors M9-M10 form the push-pull output stage.

Assuming that the Ci’s << CSMC and CL, gmf = gm3 in order

to obtain a symmetrical push-pull output stage with improved

slew rate and settling performance, and the poles are widely

separated, small-signal analysis yields the transfer function Figure 7. Diagram illustrating pole-zero locations (not to scale).

given in (3). The dominant LHP zero is due to the SMCICB

IV. SIMULATION RESULTS

network, given by

The

circuit

in

Fig. 6 was simulated in 0.5µm 2P3M CMOS

ω Z ,SMCICB ≈ −1 / RSMC C SMC .

(4)

ON-Semi process using the aspect ratios of the transistors

The second zero ωZ,non-dom is non-dominant, situated at very given in Table I. The amplifier was designed to drive a

high frequencies, and is neglected. The dominant pole is due 25kΩ//125pF load, achieving 8.2MHz bandwidth, with power

to the CSMC of the SMCICB network and is given by

supplies of ±1.5V, CSMC of 12pF and RSMC of 200kΩ. The total

(5) quiescent current is 80μA.

ω P1 ≈ −1 / R1C SMC g m 2 R2 g m3 R3 .

The non-dominant second pole is given by

Fig. 9 shows the closed-loop unity-gain step response.

R1 R2 g m 2 R3 g m3

ωP2 ≈ −

.

(6) Characteristics of the proposed amplifier are shown in Table

RSMC (R1C1 + R2C 2 )

II. Table III summarizes the performance comparison with

The output pole is situated close to the dominant pole and is reported multi-stage amplifiers. The proposed scheme achieves

figures of merit, IFOMS (= GBW ⋅ C L / I dd ) and IFOML

given by

ω PL ≈ −1 / R L C L .

(7) (= SR ⋅ C L / I dd ) comparable to the other reported topologies.

The LHP zero ω Z ,SMCICB cancels the output pole resulting in a

V. CONCLUSION

single-pole system as shown in Fig. 7. By equating (4) and

A novel single Miller compensation topology using an

(7), we see that the simple design equation for the SMCICB

inverting current buffer (SMCICB) for multi-stage amplifiers

network becomes

(8) is introduced. An effective method of using a series resistor for

RSMC C SMC = RL C L .

accurate placement of the LHP zero is detailed. Simulation

Fig. 8 shows the simulated gain and phase response with and

results in good agreement with theoretical analysis validate the

without RSMC. The phase margin is given by

proposed compensation scheme.

1581

90

Gain (dB)

60

40

With RSMC

GBW=8.2MHz

20

0

-20

Without RSMC

-40 0

10

10

1

10

2

10

3

10

4

10

5

10

6

10

7

Phase (Degrees)

180

150

With RSMC

Phase Margin=80º

100

50

Without RSMC

0 0

10

10

1

10

2

10

3

10

4

10

5

10

6

10

7

Frequency (Hz)

Figure 8. Gain and phase response of the amplifier of Fig. 6 with and without RSMC in the SMCICB network. The effect of RSMC on the phase margin can be clearly seen.

0.4

Voltage (V)

0.2

REFERENCES

Vout

[1]

0

-0.2

-0.4

0

2

4

time µs

6

[2]

0.4

Voltage (V)

0.2

Vin

0

[3]

-0.2

-0.4

0

2

4

6

[4]

time µs

Figure 9. Unity-gain buffer transient response.

[5]

TABLE I

TRANSISTOR ASPECT RATIOS.

Transistor

M0, M5, M7, M9

M1, M2

M3, M4

M6, M8, M10

Value

2(30/0.9)

9/0.9

15/0.9

30/0.9

[6]

[7]

[8]

TABLE II

CHARACTERISTICS OF THE AMPLIFIER OF FIG. 6.

Power supply

Total bias current

Load Resistance

Load capacitance

DC gain

Gain-Bandwidth Product

Phase Margin

Positive/negative slew rate

PSRR at DC

Process

±1.5V

80µA

25kΩ

125pF

75dB

8.2MHz

>80⁰

4.3V/µs, 5.5V/ µs

63dB

0.5µm 2P3M ON Semi

[9]

[10]

[11]

TABLE III

COMPARISON OF DIFFERENT MULTI-STAGE AMPLIFIER TOPOLOGIES.

SMFFC

[2]

SMCNR

[3] *

RAFFC

[9]

RSAMC

[4]*

SMCICB*

This

work

Itot

µA

GBW

MHz

SR

V/µs

CC

RC

IFOMS

MHzpF/mA

IFOML

V/µspF/mA

µm

210

9

0.5

4pF

5143

1943

0.5

150pF

14

1.8

0.7

500

pF

105

1.75

1.5

500pF

160

27

0.8

4.9

CL

RL

120pF

25kΩ

125pF

25kΩ

80

8.2

2pF,

15.8kΩ

C1=11.5

C2=0.5

19,286

7500

0.35

7292

6333

0.6

0.7pF

85,218

2640

0.18

12pF

200kΩ

12,813

7656

0.5

[12]

[13]

*simulated results.

1582

X. Fan, C. Mishra, and E. Sanchez-Sinencio, “Single Miller Capacitor

Frequency Compensation Technique for Low-power Multistage

Amplifiers,” IEEE J. Solid-State Circuits, vol. 40, no. 3, pp. 584-592,

Mar. 2005.

S. O. Cannizzaro, A. D. Grasso, G. Palumbo, and S. Pennisi, “Single

Miller capacitor frequency compensation with nulling resistor for threestage amplifiers,” International Journal of Circuit Theory and

Applications, vol. 36, no. 7, pp. 825–837, Oct 2008.

M. Jalalifar, M. Yavari, and F. Raissi “A novel topology in RNMC

amplifiers with single miller compensation capacitor,” in Proc. IEEE

Int. Symp. Cir. and Syst., ISCAS’08, pp. 296–299, May 2008.

S. Guo and H. Lee, “Single-Capacitor Active-Feedback Compensation

for Small-Capacitive-Load Three-Stage Amplifiers,” IEEE Trans. on

Circuits and Systems–II, vol. 56, no. 10, pp. 758-762, Oct. 2009.

B. K. Ahuja, “An improved frequency compensation technique for

CMOS operational amplifiers,” IEEE J. Solid-State Circuits, vol. 18,

no. 6, pp. 629–633, Dec. 1983.

P. R. Gray and R. G. Meyer, “MOS operational amplifier design-A

tutorial overview,” IEEE J. Solid-State Circuits, vol. 17, no. 6, pp.

969–982, Dec. 1982.

G. Palumbo, S. Pennisi, “Feedback Amplifiers: Theory and Design,”

Kluwer Academic Publishers: Boston, 2002.

P. J. Hurst, et al, “Miller compensation using current buffers in fully

differential CMOS two-stage operational amplifiers,” IEEE Trans. on

Cir. and Syst. I, vol.51, no. 2, pp. 275–285, Feb. 2004.

A. D. Grasso, G. Palumbo, and S. Pennisi, “Advances in reverse nested

Miller compensation,” IEEE Trans. Circuits Syst. I, vol. 54, no. 7, pp.

1459-1470, Jul. 2007.

A. Garimella and P. M. Furth, “A 1.21V, 100mA, 0.1μF-10μF output

capacitor low drop-out voltage regulator for SoC applications,” IEEE

Int. Conf. on Electronics, Circuits, and Syst, ICECS 2009, Dec 2009.

G. A. Rincon-Mora, “Active capacitor multiplier in Millercompensated circuits,” IEEE J. Solid-State Circuits, vol.35, no.1,

pp.26–32, Jan. 2000.

S. K. Lau, P. K. T. Mok, and K. N. Leung, “A low-dropout regulator

for SoC with Q-reduction,” IEEE J. Solid-State Circuits, vol. 42, no. 3,

pp. 658–664, Mar. 2007.

A. Garimella, M. W. Rashid, and P. M. Furth, “Reverse Nested Miller

Compensation using Current Buffers and Implementation in a Threestage Low Drop-Out Voltage Regulator,” IEEE Trans. on Circuits and

Systems-II, accepted for future publication, in print, Jan 2010.