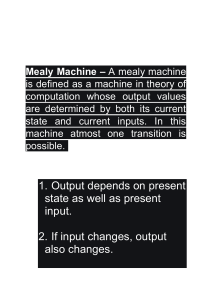

Indian Institute of Technology Jodhpur, Year 2018-2019 Digital Logic and Design (Course Code: EE222) Lecture 22-23: Sequential Circuits Contd.. Course Instructor: Shree Prakash Tiwari Email: sptiwari@iitj.ac.in Webpage: http://home.iitj.ac.in/~sptiwari/ Course related documents will be uploaded on http://home.iitj.ac.in/~sptiwari/DLD/ Note: The information provided in the slides are taken form text books Digital Electronics (including Mano & Ciletti), and various other resources from internet, for teaching/academic use only 1 Combinational vs. Sequential Combinational Logic Circuit − − − Output is a function of the inputs. Does not have state information. Does not require memory. Sequential Logic Circuit − Output is a function of the present state (and of the inputs). − Has state information Requires memory. Uses Flip-Flops to implement memory. − − Synchronous vs. Asynchronous Synchronous Sequential Circuit − − Clocked All Flip-Flops use the same clock and change state on the same triggering edge. Asynchronous Sequential Circuit − − − No clock Can change state at any instance in time. More complex than synchronous sequential circuits. Flip-Flop Summary ° Flip flops are powerful storage elements • They can be constructed from gates and latches! ° D flip flop is simplest and most widely used ° Asynchronous inputs allow for clearing and presetting the flip flop output ° Multiple flops allow for data storage • The basis of computer memory! ° Combine storage and logic to make a computation circuit ° Next: Analyzing sequential circuits. Overview ° Understanding flip flop state: • Stored values inside flip flops ° Clocked sequential circuits: • Contain flip flops ° Representations of state: • State equations • State table • State diagram ° Finite state machines • Mealy machine • Moore machine Flip Flop State ° Behavior of clocked sequential circuit can be determined from inputs, outputs and FF state x Q1 D0 D Q Q’ Q Q0 D D1 Q0 Q’ y Q1 Clk y(t) = x(t)Q1(t)Q0(t) Q0(t+1) = D0(t) = x(t)Q1(t) Q1(t+1) = D1(t) = x(t) + Q0(t) Output and State Equations ° Next state dependent on previous state. x Q1 D0 D Q Q’ Q Q0 Output equation State equations D D1 Q0 Q’ y Q1 Clk y(t) = x(t)Q1(t)Q0(t) Q0(t+1) = D0(t) = x(t)Q1(t) Q1(t+1) = D1(t) = x(t) + Q0(t) State Table ° Sequence of outputs, inputs, and flip flop states enumerated in state table ° Present state indicates current value of flip flops ° Next state indicates state after next rising clock edge ° Output is output value on current clock edge Present State State Table Q1(t) Q0(t) 00 01 10 11 Next State x=0 x=1 00 10 00 10 10 10 11 11 Q1(t+1) Q0(t+1) Output x=0 x=1 0 0 0 0 0 0 0 1 State Table ° All possible input combinations enumerated ° All possible state combinations enumerated ° Separate columns for each output value. ° Sometimes easier to designate a symbol for each state. Let: s0 = 00 s1 = 01 s2 = 10 s3 = 11 Present State s0 s1 s2 s3 Next State x=0 x=1 s0 s2 s0 s2 s2 s2 s3 s3 Output x=0 x=1 0 0 0 0 0 0 0 1 State Diagram ° Circles indicate current state ° Arrows point to next state ° For x/y, x is input and y is output Present State 00 01 10 11 Next State Output x=0 x=1 00 10 00 10 x=0 x=1 10 10 11 11 0 0 0 0 1/1 0/0 0/0 00 01 0/0 10 1/0 1/0 1/0 0/0 11 0 0 0 1 State Diagram ° Each state has two arrows leaving ° One for x = 0 and one for x = 1 ° Unlimited arrows can enter a state ° Note use of state names in this example ° Easier to identify 1/1 0/0 0/0 s0 s1 1/0 0/0 1/0 s2 1/0 0/0 s3 Flip Flop Input Equations ° Boolean expressions which indicate the input to the flip flops. x Q1 D0 D Q Q’ Q Q0 D D1 Q0 Q’ y Q1 Clk DQ0 = xQ1 DQ1 = x + Q0 Format implies type of flop used Mealy Machine • Output based on state and present input Comb. Logic X(t) present input Q(t+1) next state Flip Flops Q(t) present state clk Comb. Logic Y(t) Moore Machine • Output based on state only Comb. Logic X(t) present input Q(t+1) next state Flip Flops clk Q(t) present state Comb. Logic Y(t) Mealy versus Moore Mealy Model Inputs Input Logic Combinational Output Logic Memory Element Outputs Combinational Moore Model Inputs Input Logic Combinational Output Logic Memory Element Combinational Outputs Finite State Machine: Models Mealy Machine − Outputs are a function of the present state and the input. − State diagram includes an input and output value for each transition (between states). Moore Machine − Outputs are a function of the present state. − Outputs are independent of the inputs. − State diagram includes an output value for each state. There is an equivalent Mealy machine for each Moore machine. State Diagram with One Input & One Mealy Output ° Mano text focuses on Mealy machines ° State transitions are shown as a function of inputs and current outputs. e.g. 1 S1 1/1 S4 0/0 Input(s)/Output(s) shown in transition 0/0 1/0 S2 0/0 1/0 0/0 S3 1/0 FSM: State Diagram (Moore) Output State A Input C B FSM Analysis: Procedure, simplified • Determine the Flip-Flop input equations In terms of the present state and input variables • Determine the FSM output equation(s) • Determine the next state values in the state table Assume binary encoding Use Flip-Flop Characteristic Equation • Construct the state table Assign a state to each binary state assignment • Draw the corresponding state diagram • Determine the behavior of the FSM Clocked Synchronous State-machine Analysis Given the circuit diagram of a state machine: 1 Analyze the combinational logic to determine flip-flop input (excitation) equations: Di = Fi (Q, inputs) • The input to each flip-flop is based upon current state and circuit inputs. 2 Substitute excitation equations into flip-flop characteristic equations, giving transition equations: Qi(t+1) = Hi( Di ) 3 From the circuit, find output equations: • Z = G (Q, inputs) The outputs are based upon the current state and possibly the inputs. 4 Construct a state transition/output table from the transition and output equations: • • • Similar to truth table. Present state on the left side. Outputs and next state for each input value on the right side. • Provide meaningful names for the states in state table, if possible. 5 Draw the state diagram which is the graphical representation of state table. FSM Analysis: Example (D FF) input state output What type of FSM is this? A(t+1) = A.x + B.x B(t+1) = A’.x Y = (A+B).x’ FSM Analysis: Example (D FF) ° A time sequence of inputs, outputs and multiple flipflop states can be enumerated in a state table or transition table Another State Table for the Circuit ° A time sequence of inputs, outputs and multiple flipflop states can be enumerated in a state table or transition table State diagram of the circuit ° A graphical representation of the time sequence of inputs, outputs and flip-flop states is state diagram ° State diagram follows directly from the state table Analysis with D Flip-Flops ° Identify flip flop input equations ° Identify output equation DA = A ⊕ x ⊕ y A(t+1) = A ⊕ x ⊕ y Note: this example has no output Sequential circuit with JK flip-flop ° Input equations Characteristic/state equations next-state values Input Equations: JA = B, KA = B.x’, JB = x’, KB = A’.x + A.x’ = A ⊕ x State Table Characteristic Equations: A(t+1) = J.A’ + K’A, B(t+1) = J.B’ + k’B A(t+1) = B.A’ + (B.x’)’.A = A’.B + A.B’ + A.x B(t+1) = x’.B’ + (A ⊕ x )’.B = B’.x’ + A.B.x + A’.B.x’ State diagram of the circuit Sequential circuit with T flip-flops (Binary Counter) State Table and Diagram Summary ° Flip flops contain state information ° State can be represented in several forms: • State equations • State table • State diagram ° Possible to convert between these forms ° Circuits with state can take on a finite set of values • Finite state machine ° Two types of “machines” • Mealy machine • Moore machine FSM Design: Procedure, simplified ° Understand specifications ° Derive state diagram ° Create state table ° Perform state minimization (if necessary) ° Encode states (state assignment) ° Create state-assigned table ° Select type of Flip-Flop to use ° Determine Flip-Flop input equations and FSM output equation(s) ° Draw logic diagram 32 What next…… ° FSM Design