Universal Chiplet Interconnect

Express (UCIe)

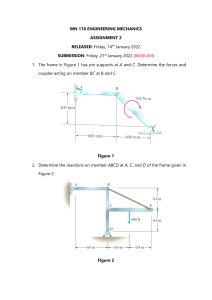

Specification Revision 1.0

Februrary 24, 2022

Universal Chiplet Interconnect express (UCIe)

Specification

UCIe Specification Revision 1.0

Februrary 24, 2022

Property of Universal Chiplet Interconnect Express (UCIe) 2022

2

Universal Chiplet Interconnect express (UCIe)

Specification

Contents

1.0

Introduction . . . . . . . . . . . . . . . . . . . . .

1.1

UCIe Components . . . . . . . . . . . . .

1.1.1 Protocol Layer . . . . . . . . . .

1.1.2 Die-to-Die (D2D) Adapter . .

1.1.3 Physical Layer . . . . . . . . . .

1.1.4 Interfaces . . . . . . . . . . . . .

1.2

UCIe Configurations . . . . . . . . . . . .

1.2.1 Single module configuration .

1.2.2 Multi Module Configurations:

1.3

UCIe Retimers . . . . . . . . . . . . . . . .

1.4

UCIe Key Performance Targets . . . .

1.5

Interoperability . . . . . . . . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

15

18

19

19

20

20

21

21

21

23

24

25

2.0

Protocol Layer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1

PCIe 6.0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.1 Raw Mode for PCIe 6.0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.1.2 Flit Mode: Standard 256B Flit for PCIe 6.0 . . . . . . . . . . . . . . . .

2.2

CXL 3.0 256B Flit Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2.1 Raw Mode for "CXL 256B Flit Mode" . . . . . . . . . . . . . . . . . . . .

2.2.2 Flit Mode: Latency-Optimized 256B Flit for "CXL 256B Flit Mode"

2.2.3 Flit Mode: Standard 256B Flit for "CXL 256B Flit Mode" . . . . . . .

2.3

CXL 2.0 or "CXL 68B-Enhanced Flit Mode" . . . . . . . . . . . . . . . . . . . . . .

2.3.1 Raw Mode for CXL 2.0 or "CXL 68B-Enhanced Flit Mode" . . . . . .

2.3.2 Flit Mode: 68B Flit for CXL 2.0 or "CXL 68B-Enhanced Flit Mode"

2.4

Streaming protocol. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4.1 Raw Mode for Streaming protocol . . . . . . . . . . . . . . . . . . . . . .

2.5

Summary of supported modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

26

27

27

27

28

28

28

29

30

30

30

31

31

31

3.0

Die-to-Die Adapter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1

Link Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.1.1 Stage 3 of Link Initialization: Adapter Initialization . . . . . . .

3.2

Modes of operation and Protocols . . . . . . . . . . . . . . . . . . . . . . . . .

3.2.1 Raw Mode for all protocols . . . . . . . . . . . . . . . . . . . . . . . .

3.2.2 CXL 2.0 or "CXL 68B-Enhanced Flit Mode" . . . . . . . . . . . . .

3.2.3 PCIe 6.0 or "CXL 256B Flit Mode" with Standard 256B Flit . .

3.2.4 "CXL 256B Flit Mode" with Latency-Optimized 256B Flit . . . .

3.3

Decision table for protocol and flit format . . . . . . . . . . . . . . . . . . .

3.4

State Machine Hierarchy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5

Power Management Link States . . . . . . . . . . . . . . . . . . . . . . . . . .

3.6

CRC Computation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.7

Retry Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8

Runtime Link Testing using Parity . . . . . . . . . . . . . . . . . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

32

33

34

38

38

38

41

44

45

46

48

49

50

51

4.0

Logical Physical Layer . . . . . . . . . . . . . .

4.1

Data and Sideband Transmission Flow

4.1.1 Byte to Lane Mapping . . . . . .

4.1.2 Valid Framing . . . . . . . . . . . .

4.1.3 Clock Gating. . . . . . . . . . . . .

4.1.4 Free Running Clock Mode . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

54

54

54

56

57

57

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

UCIe Specification Revision 1.0

Februrary 24, 2022

Property of Universal Chiplet Interconnect Express (UCIe) 2022

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

3

Universal Chiplet Interconnect express (UCIe)

Specification

4.2

4.3

4.4

4.5

4.6

4.7

5.0

4.1.5 Sideband transmission. . . . . . . . . . . . . . . . . .

Lane Reversal . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.1 Lane ID . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Interconnect redundancy remapping . . . . . . . . . . . . .

4.3.1 Data Lane repair . . . . . . . . . . . . . . . . . . . . . .

4.3.2 Data Lane repair with Lane reversal . . . . . . . .

4.3.3 Data Lane repair implementation . . . . . . . . . .

4.3.4 Clock and Track Lane remapping . . . . . . . . . .

4.3.5 Clock and Track Lane repair implementation . .

4.3.6 Valid Repair and implementation. . . . . . . . . . .

4.3.7 Width Degrade in Standard Package Interfaces.

Data to Clock Training and Test Modes . . . . . . . . . . . .

4.4.1 Scrambling and training pattern generation . . .

Link Initialization and Training . . . . . . . . . . . . . . . . . .

4.5.1 Link Training basic operations. . . . . . . . . . . . .

4.5.2 Link Training with Retimer . . . . . . . . . . . . . . .

4.5.3 Link Training State Machine . . . . . . . . . . . . . .

Run time Recalibration . . . . . . . . . . . . . . . . . . . . . . .

Multi-module Link. . . . . . . . . . . . . . . . . . . . . . . . . . .

4.7.1 Multi-module initialization . . . . . . . . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

Electrical Layer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1

Interoperability . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1.1 Data rates . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2

Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.1 Interface Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.2 Electrical summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3

Transmitter Specification. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3.1 Driver Topology . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.3.2 Transmitter Electrical parameters . . . . . . . . . . . . . . . . . . .

5.3.3 24.0, and 32.0 GT/s Transmitter Equalization. . . . . . . . . . .

5.4

Receiver Specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.4.1 Receiver Electrical Parameters . . . . . . . . . . . . . . . . . . . . .

5.4.2 Rx Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.4.3 24.0, and 32.0 GT/s Receiver Equalization . . . . . . . . . . . . .

5.5

Clocking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.5.1 Track. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.6

Supply noise and clock skew . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.7

Ball-out and Channel Specification . . . . . . . . . . . . . . . . . . . . . . . .

5.7.1 Voltage Transfer Function . . . . . . . . . . . . . . . . . . . . . . . .

5.7.2 Advanced Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.7.3 Standard Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.8

Tightly-coupled mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.9

Interconnect redundancy remapping . . . . . . . . . . . . . . . . . . . . . .

5.9.1 Advanced Package Lane remapping. . . . . . . . . . . . . . . . . .

5.9.2 Standard Package Lane remapping . . . . . . . . . . . . . . . . . .

5.10 BER requirements, CRC and retry. . . . . . . . . . . . . . . . . . . . . . . . .

5.11 Valid and Clock Gating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.12 Electrical Idle. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.13 Sideband signaling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.13.1 Sideband Electrical Parameters . . . . . . . . . . . . . . . . . . . . .

UCIe Specification Revision 1.0

Februrary 24, 2022

Property of Universal Chiplet Interconnect Express (UCIe) 2022

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

. 58

. 58

. 59

. 60

. 60

. 62

. 62

. 69

. 70

. 72

. 73

. 73

. 75

. 79

. 79

. 82

. 83

109

109

109

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

111

111

111

111

111

112

113

114

115

116

117

118

119

121

122

122

123

124

124

126

130

134

135

135

136

136

136

137

138

138

4

Universal Chiplet Interconnect express (UCIe)

Specification

6.0

Sideband . . . . . . . . . . . . . . . . . . . . . . . . .

6.1

Protocol specification . . . . . . . . . . . . .

6.1.1 Packet Types . . . . . . . . . . . . .

6.1.2 Packet Formats. . . . . . . . . . . .

6.1.3 Flow Control and Data Integrity

6.1.4 Operation on RDI and FDI . . . .

7.0

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

139

139

139

142

160

161

Configuration and Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.1

High level Software view of UCIe . . . . . . . . . . . . . . . . . . . . . . . . .

7.2

SW Discovery of UCIe Links. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.3

Register Location Details and Access Mechanism . . . . . . . . . . . . . .

7.4

Software view Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.5

UCIe Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.5.1 UCIe Link DVSEC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

7.5.2 UCIe Switch Register Block (CiSRB) DVSEC Capability . . . . .

7.5.3 D2D/PHY Register Block. . . . . . . . . . . . . . . . . . . . . . . . . .

7.5.4 Test/Compliance Register Block . . . . . . . . . . . . . . . . . . . .

7.5.5 Implementation Specific Register Blocks . . . . . . . . . . . . . .

7.6

MSI and MSI-X Capability in Hosts/Switches for UCIe interrupt . . . .

....

....

....

....

....

....

....

....

....

....

....

....

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

162

162

163

164

166

168

169

186

188

214

214

215

8.0

Interface Definitions . . . . . . . . . . . . . . . .

8.1

Raw Die-to-Die Interface (RDI) . . . . . .

8.1.1 Interface reset requirements . .

8.1.2 Interface clocking requirements

8.1.3 Dynamic clock gating . . . . . . .

8.1.4 Data Transfer . . . . . . . . . . . . .

8.1.5 RDI State Status Machine . . . .

8.1.6 RDI bring up flow . . . . . . . . . .

8.1.7 RDI PM flow . . . . . . . . . . . . . .

8.2

Flit-Aware Die-to-Die Interface (FDI) . .

8.2.1 Interface reset requirements . .

8.2.2 Interface clocking requirements

8.2.3 Dynamic clock gating . . . . . . .

8.2.4 Data Transfer . . . . . . . . . . . . .

8.2.5 FDI State Status Machine. . . . .

8.2.6 Rx_active_req/Sts Handshake .

8.2.7 FDI Bring up flow . . . . . . . . . .

8.2.8 FDI PM Flow . . . . . . . . . . . . . .

8.3

Common rules for FDI and RDI . . . . . .

8.3.1 Stallreq/Ack Mechanism. . . . . .

8.3.2 State Request and Status . . . .

8.3.3 Example flow diagrams . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

216

216

220

221

221

223

223

224

225

229

237

237

238

239

241

241

242

243

248

248

249

255

9.0

Compliance and Debug . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 257

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

Appendices

A

CXL/PCIe Register applicability to UCIe. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 259

B

CRC Code Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 262

C

AIB Interoperability . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 286

UCIe Specification Revision 1.0

Februrary 24, 2022

Property of Universal Chiplet Interconnect Express (UCIe) 2022

5

Universal Chiplet Interconnect express (UCIe)

Specification

Figures

Figure 1.

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

2.

3.

4.

5.

6.

7.

8.

9.

10.

11.

12.

13.

14.

15.

16.

17.

18.

19.

20.

21.

22.

23.

24.

25.

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

26.

27.

28.

29.

30.

31.

32.

33.

34.

35.

36.

37.

38.

39.

40.

41.

42.

43.

44.

45.

A Package comprising of CPU dies, Accelerator die(s), and I/O Tile die connected

through UCIe 15

UCIe enabling long-reach connectivity at Rack/Pod Level . . . . . . . . . . . . . . . . . .

Standard Package interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Advanced Package interface: Example 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Advanced Package interface: Example 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Advanced Package interface: Example 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

UCIe Layers and functionalities . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Physical Layer components . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Single module configuration: Advanced Package . . . . . . . . . . . . . . . . . . . . . . . .

Single module configuration: Standard Package . . . . . . . . . . . . . . . . . . . . . . . .

Two module configuration for Standard Package . . . . . . . . . . . . . . . . . . . . . . . .

Four module configuration for Standard Package . . . . . . . . . . . . . . . . . . . . . . . .

Block Diagram for UCIe Retimer Connection . . . . . . . . . . . . . . . . . . . . . . . . . . .

Format for Raw Mode without spare Lanes . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Format for Standard 256B Flit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Format for CXL.io Latency-Optimized 256B Flit . . . . . . . . . . . . . . . . . . . . . . . . .

Second Format for CXL.cachemem Latency-Optimized 256B Flit . . . . . . . . . . . . .

Format for Standard 256B Flit for CXL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Format for 68B Flit on the UCIe Link . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Format for the 68B Flit on FDI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Functionalities in the Die-to-Die Adapter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Example configurations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Stages of UCIe Link initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Parameter exchange for Adapter Capabilities . . . . . . . . . . . . . . . . . . . . . . . . . .

Parameter Exchange if "68B Flit Mode" or "CXL 256B Flit Mode" is 1b in

{FinCap.Adapter} 37

Format 1: Raw Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Format 2: CXL 68B Flit Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PDS example. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Format 3: Standard 256B Flit Mode for PCIe 6.0 . . . . . . . . . . . . . . . . . . . . . . . .

Format 4: Standard 256B Flit Mode for CXL.cachemem . . . . . . . . . . . . . . . . . . .

Format 4: Standard 256B Flit Mode for CXL.io . . . . . . . . . . . . . . . . . . . . . . . . . .

Format 5 and 6: Latency Optimized 256B Flit Mode for CXL.io. . . . . . . . . . . . . . .

Format 5 and 6: Latency Optimized 256B Flit Mode for CXL.cachemem . . . . . . . .

State Machine Hierarchy examples. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Example of hierarchical PM entry for CXL . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Diagram of CRC calculation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Successful Parity Feature negotiation between Die 1 Tx and Die 0 Rx. . . . . . . . . .

Unsuccessful Parity Feature negotiation between Die 1 Tx and Die 0 Rx . . . . . . . .

Bit arrangement within a byte transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Byte map for x64 interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Byte map for x32 interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Byte map for x16 interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Byte to Lane mapping for Standard package x8 degraded. . . . . . . . . . . . . . . . . .

Valid framing example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Clock gating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

UCIe Specification Revision 1.0

February 24, 2022

Property of Universal Chiplet Interconnect Express (UCIe) 2022

16

17

18

18

18

19

20

21

22

22

22

23

27

28

29

29

30

31

31

32

33

34

37

38

41

41

42

42

42

45

45

47

49

50

52

53

54

54

55

55

56

57

57

6

Universal Chiplet Interconnect express (UCIe)

Specification

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

46.

47.

48.

49.

50.

51.

52.

53.

54.

55.

56.

57.

58.

59.

60.

61.

62.

63.

64.

65.

66.

67.

68.

69.

70.

71.

72.

73.

74.

75.

76.

77.

78.

79.

80.

81.

82.

83.

84.

85.

86.

87.

88.

89.

90.

91.

92.

93.

94.

95.

Sideband serial packet. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Sideband packet transmission: back to back . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Data Lane remapping possibilities to fix potential defects . . . . . . . . . . . . . . . . . . 61

Data Lane remapping: Mux chain. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Single Lane failure remapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Single Lane remapping implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Two Lane failure remapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Two Lane remapping implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Clock and Track repair . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Clock and track repair: Differential Rx . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Clock and track repair: Pseudo Differential Rx . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Clock and Track Lane repair scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Clock and track repair: CKP repair . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Clock and track repair: CKN repair . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Clock and track repair: Track repair . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Valid repair: Normal Path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Valid Repair: Repair Path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Test and training logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Lane failure detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

All Lane error detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

LFSR implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

LFSR alternate implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Example Retimer bring up when performing speed/width match . . . . . . . . . . . . . 83

Link Training State Machine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

MBINIT: Main band initialization and repair flow . . . . . . . . . . . . . . . . . . . . . . . . 88

Main Band Training . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Advanced Package module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

Standard Package module. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

Transmitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

Transmitter driver example circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

Transmitter de-emphasis . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

Transmitter de-emphasis waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

Receiver topology . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

Receiver termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

Receiver termination map for Table 34 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

Example CTLE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

Clocking architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

Example Eye diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

Circuit for VTF calculation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

Loss and Crosstalk mask. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

Advanced Package Bump Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

Advanced Package Bump map: Signal exit order . . . . . . . . . . . . . . . . . . . . . . . 129

Standard Package Bump Map: x16 interface . . . . . . . . . . . . . . . . . . . . . . . . . . 132

Standard Package x16 interface: Signal exit order . . . . . . . . . . . . . . . . . . . . . . 132

Standard Package Bump Map: x32 interface . . . . . . . . . . . . . . . . . . . . . . . . . . 133

Standard Package x32 interface: Signal exit routing . . . . . . . . . . . . . . . . . . . . 133

Standard Package cross section for stacked module . . . . . . . . . . . . . . . . . . . . . 133

Standard Package reference configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

Data Lane repair resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

Data Lane repair . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

UCIe Specification Revision 1.0

February 24, 2022

Property of Universal Chiplet Interconnect Express (UCIe) 2022

7

Universal Chiplet Interconnect express (UCIe)

Specification

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

Figure

96.

97.

98.

99.

100.

101.

102.

103.

104.

105.

106.

107.

108.

109.

110.

111.

112.

113.

114.

115.

116.

117.

118.

119.

120.

121.

122.

123.

124.

125.

126.

127.

128.

129.

Valid Framing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Data, Clock, Valid Gated Levels: Unterminated Link . . . . . . . . . .

Data, Clock, Valid Gated Levels: Terminated Link . . . . . . . . . . .

Sideband signaling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Format for Register Access request . . . . . . . . . . . . . . . . . . . . .

Format for Register Access completions . . . . . . . . . . . . . . . . . .

Format for Messages without Data . . . . . . . . . . . . . . . . . . . . . .

Format for Messages with data payloads . . . . . . . . . . . . . . . . .

Software view Example with Root Ports and Endpoints . . . . . . . .

Software view Example with Switch and Endpoints . . . . . . . . . .

Software view Example of UCIe Endpoint . . . . . . . . . . . . . . . . .

UCIe Link DVSEC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Example configurations using RDI . . . . . . . . . . . . . . . . . . . . . .

Example Waveform Showing Handling of Level Transition . . . . . .

Data Transfer from Adapter to Physical Layer . . . . . . . . . . . . . .

RDI Interface State Machine . . . . . . . . . . . . . . . . . . . . . . . . . .

Example flow of Link bring up on RDI . . . . . . . . . . . . . . . . . . . .

Successful PM entry flow . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PM Abort flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PM Exit flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Example configurations using FDI . . . . . . . . . . . . . . . . . . . . . .

Example Waveform Showing Handling of Level Transition . . . . . .

Data Transfer from Protocol Layer to Adapter . . . . . . . . . . . . . .

FDI Interface State Machine . . . . . . . . . . . . . . . . . . . . . . . . . .

FDI Bring up flow. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PM Entry example for CXL or PCIe protocols . . . . . . . . . . . . . . .

PM Entry example for symmetric protocol . . . . . . . . . . . . . . . . .

PM Abort Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PM Exit Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

LinkReset Example. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

LinkError example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Example of a test package for Advanced Package configuration. .

PCie Registers for UCIe devices . . . . . . . . . . . . . . . . . . . . . . . .

AIB interoperability . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

UCIe Specification Revision 1.0

February 24, 2022

Property of Universal Chiplet Interconnect Express (UCIe) 2022

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

....

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

137

137

137

138

143

144

145

153

166

167

168

170

216

222

223

224

225

227

228

228

229

239

240

241

243

246

246

247

248

255

256

257

260

286

8

Universal Chiplet Interconnect express (UCIe)

Specification

Tables

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

1.

2.

3.

4.

5.

6.

7.

8.

9.

10.

11.

12.

13.

14.

15.

16.

17.

18.

19.

20.

21.

22.

23.

24.

25.

26.

27.

28.

29.

30.

31.

32.

33.

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

34.

35.

36.

37.

38.

39.

40.

41.

42.

43.

44.

45.

46.

Terms and Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Reference Documents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Revision History. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Characteristics of UCIe on Standard Package . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Characteristics of UCIe on Advanced Package . . . . . . . . . . . . . . . . . . . . . . . . . . 17

UCIe Key Performance Targets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Groups for different bump pitches . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Specification to protocol mode requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

End Point vs Root Port Interoperability Matrix . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Modes of operation for supported protocols. . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Flit Header for Format 2 without Retry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Flit Header for Format 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Flit Header for Format 3 or Format 4 without Retry . . . . . . . . . . . . . . . . . . . . . . 43

Flit Header for Format 3 or Format 4 with Retry . . . . . . . . . . . . . . . . . . . . . . . . 44

Truth Table for determining Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Truth Table for determining Flit Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Valid framing for Retimers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Lane ID: Advanced Package module. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Lane ID: Standard Package Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

LFSR seed values. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Data to Clock Training Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

State Definitions for Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Per Lane ID pattern pattern . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Per Lane ID pattern pattern examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Standard Package Logical Lane map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Link Test Status Register based Retrain encoding . . . . . . . . . . . . . . . . . . . . . . 105

Retrain encoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

Retrain exit state resolution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

Electrical summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

Transmitter Electrical Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

Transmitter de-emphasis values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

Receiver Electrical parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

Maximum channel reach for unterminated Receiver (minimally compliant Transmitter)

119

Maximum Channel reach for unterminated Receiver (TX swing = 0.85V). . . . . . . 120

Forwarded clock frequency and phase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

IO Noise and Clock Skew . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

Eye requirements. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

Channel Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

Advanced Package module signal list . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

IL and xtalk for Standard Package: With Rx termination . . . . . . . . . . . . . . . . . . 130

IL and xtalk for Standard Package: No Rx termination . . . . . . . . . . . . . . . . . . . 130

Standard Package module signal list . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

Tightly coupled mode: Eye mask . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

Tightly coupled mode channel for Advanced package . . . . . . . . . . . . . . . . . . . . 135

Raw BER requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

Sideband Parameters summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

UCIe Specification Revision 1.0

February 24, 2022

Property of Universal Chiplet Interconnect Express (UCIe) 2022

9

Universal Chiplet Interconnect express (UCIe)

Specification

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

47.

48.

49.

50.

51.

52.

53.

54.

55.

56.

57.

58.

59.

60.

61.

62.

63.

64.

65.

66.

67.

68.

69.

70.

71.

72.

73.

74.

75.

76.

77.

78.

79.

80.

81.

82.

83.

84.

85.

86.

87.

88.

89.

90.

91.

92.

93.

94.

95.

96.

Opcode encodings mapped to Packet Types . . . . . . . . . . . . . . . . . . . . . . .

FDI sideband: srcid and dstid encodings on FDI. . . . . . . . . . . . . . . . . . . . .

RDI sideband: srcid and dstid encodings on RDI . . . . . . . . . . . . . . . . . . . .

Field descriptions for Register Access Requests . . . . . . . . . . . . . . . . . . . . .

Mapping of Addr[23:0] for different requests . . . . . . . . . . . . . . . . . . . . . .

Field Descriptions for a Completion . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Message Encodings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Link Training State Machine related Message encodings . . . . . . . . . . . . . . .

Message encodings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Link Training State Machine related encodings . . . . . . . . . . . . . . . . . . . . .

Software view of Upstream and Downstream Device at UCIe interface . . . . .

SW discovery of UCIe Links. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Summary of location of various UCIe Link related registers. . . . . . . . . . . . .

Register Attributes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

CXL Link DVSEC - PCI Express Extended Capability Header. . . . . . . . . . . . .

UCIe Link DVSEC - Designated Vendor Specific Header 1, 2 . . . . . . . . . . . .

UCIe Link DVSEC - Capability Descriptor. . . . . . . . . . . . . . . . . . . . . . . . . .

UCIe Link DVSEC - UCIe Link Capability . . . . . . . . . . . . . . . . . . . . . . . . . .

UCIe Link DVSEC - UCIe Link Control . . . . . . . . . . . . . . . . . . . . . . . . . . . .

UCIe Link DVSEC - UCIe Link Status . . . . . . . . . . . . . . . . . . . . . . . . . . . .

UCIe Link DVSEC - Link Event Notification Control . . . . . . . . . . . . . . . . . . .

UCIe Link DVSEC - Error Notification Control. . . . . . . . . . . . . . . . . . . . . . .

UCIe Link DVSEC - Register Locator 0, 1, 2. . . . . . . . . . . . . . . . . . . . . . . .

UCIe Link DVSEC - Sideband Mailbox Index . . . . . . . . . . . . . . . . . . . . . . .

UCIe Link DVSEC - Sideband Mailbox Data . . . . . . . . . . . . . . . . . . . . . . . .

UCIe Link DVSEC - Sideband Mailbox Control . . . . . . . . . . . . . . . . . . . . . .

UCIe Link DVSEC - Sideband Mailbox Status . . . . . . . . . . . . . . . . . . . . . . .

UCIe Link DVSEC - Requester ID . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

UCIe Link DVSEC - Associated Port Numbers. . . . . . . . . . . . . . . . . . . . . . .

CiSRB DVSEC - PCI Express Extended Capability Header . . . . . . . . . . . . . .

CiSRB DVSEC - Designated Vendor Specific Header 1, 2 . . . . . . . . . . . . . . .

CiSRB DVSEC - CiSRB Base Address. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

D2D/PHY Register Block - UCIe Register Block Header (Offset 0x0) . . . . . . .

Uncorrectable Error Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Uncorrectable Error Mask Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Uncorrectable Error Severity Register. . . . . . . . . . . . . . . . . . . . . . . . . . . .

Correctable Error Status Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Correctable Error Mask Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Header Log 1 Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Header Log 2 Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Error and Link Testing Control Register . . . . . . . . . . . . . . . . . . . . . . . . . .

Runtime Link Testing Parity Log 0 Register . . . . . . . . . . . . . . . . . . . . . . . .

Runtime Link Testing Parity Log 1 Register . . . . . . . . . . . . . . . . . . . . . . . .

Runtime Link Testing Parity Log 2 Register . . . . . . . . . . . . . . . . . . . . . . . .

Runtime Link Testing Parity Log 3 Register . . . . . . . . . . . . . . . . . . . . . . . .

Advertised Adapter Capability Log Register . . . . . . . . . . . . . . . . . . . . . . . .

Finalized Adapter Capability Log Register . . . . . . . . . . . . . . . . . . . . . . . . .

Advertised CXL Capability Log Register. . . . . . . . . . . . . . . . . . . . . . . . . . .

Finalized CXL Capability Log Register . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Physical Layer Capability Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

UCIe Specification Revision 1.0

February 24, 2022

Property of Universal Chiplet Interconnect Express (UCIe) 2022

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

140

140

141

142

143

144

145

148

153

155

162

163

165

168

171

172

172

173

174

176

177

179

183

184

184

185

185

185

186

186

187

187

188

189

190

190

191

192

192

193

195

196

197

198

198

198

198

199

199

200

10

Universal Chiplet Interconnect express (UCIe)

Specification

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

Table

97.

Physical Layer Control Register . . . . . . . . . . . . . . . . . . .

98.

Physical Layer Status Register . . . . . . . . . . . . . . . . . . . .

99.

Phy Init and Debug Register . . . . . . . . . . . . . . . . . . . . .

100. Training Setup 1 Register . . . . . . . . . . . . . . . . . . . . . . .

101. Training Setup 2 Register . . . . . . . . . . . . . . . . . . . . . . .

102. Training Setup 3 Register . . . . . . . . . . . . . . . . . . . . . . .

103. Training Setup 4 Register . . . . . . . . . . . . . . . . . . . . . . .

104. Current Lane Map Module 0 Register . . . . . . . . . . . . . . .

105. Current Lane Map Module 1 Register . . . . . . . . . . . . . . .

106. Current Lane Map Module 2 Register . . . . . . . . . . . . . . .

107. Current Lane Map Module 3 Register . . . . . . . . . . . . . . .

108. Error Log 0 Register . . . . . . . . . . . . . . . . . . . . . . . . . . .

109. Error Log 1 Register . . . . . . . . . . . . . . . . . . . . . . . . . . .

110. Runtime Link Test Control. . . . . . . . . . . . . . . . . . . . . . .

111. Runtime Link Test Status Register . . . . . . . . . . . . . . . . .

112. Mainband Data Repair Register . . . . . . . . . . . . . . . . . . .

113. Clock, Track, Valid and Sideband Repair Register. . . . . . .

114. RDI signal list . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

115. FDI signal list . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

116. Requests Considered in Each LPIF State by Physical Layer

117. CXL Registers for UCIe devices . . . . . . . . . . . . . . . . . . .

118. AIB 2.0 Datapath mapping for Advanced Package . . . . . .

119. AIB 1.0 Datapath mapping for Advanced Package . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

UCIe Specification Revision 1.0

February 24, 2022

Property of Universal Chiplet Interconnect Express (UCIe) 2022

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

201

202

203

203

204

204

205

205

205

205

206

207

208

209

211

212

214

217

230

250

259

287

287

11

Universal Chiplet Interconnect express (UCIe)

Specification

Terminology

Table 1.

Terms and Definitions

Term

Definition

UCIe

Universal Chiplet Interconnect express

PCIe

Peripheral Component Interconnect Express

CXL

Compute eXpress Link

SoC

System on a Chip

USB

Universal Serial Bus

NVMe

Non-Volatile Memory express

SERDES

Serializer/Deserializer

PHY

Physical Layer

CPU

Central Processing Unit

I/O

Input/Output

DDR

Double Data Rate Memory

BER

Bit Error Ratio

EMIB

Embedded Multi-die Interconnect Bridge

CoWoS

Chip on Wafer on Substrate

CRC

Cyclic Redundancy Check

D2D

Die-to-Die

MHz

Mega Hertz

Ack

Acknowledge

AFE

Analog Front End

Endpoint

As defined in the PCI Express Base Specification.

LSB

Least Significant Bit

MSB

Most Significant Bit

NAck

Negatively acknowledge

PCIe

Peripheral Component Interconnect Express

Root

Complex

As defined in the PCI Express Base Specification.

Root Port

As defined in the PCI Express Base Specification.

UI

Unit Interval

Vref

Reference voltage for receivers

UCIe Link

A UCIe connection between two chiplets. These chiplets are Link partners in the

context of UCIe since they communicate with each other using a common UCIe

Link.

UCIe die

This term is used throughout this specification to denote the logic associated

with the UCIe Link on any given chiplet with a UCIe Link connection. It is used

as a common noun to denote actions or messages sent or received by an

implementation of UCIe.

UCIe Specification Revision 1.0

Februrary 24, 2022

Property of Universal Chiplet Interconnect Express (UCIe) 2022

12

Universal Chiplet Interconnect express (UCIe)

Specification

Table 1.

Terms and Definitions

Term

Definition

remote Link

partner

This term is used throughout this specification to denote the logic associated

with the far side of the UCIe Link; to denote actions or messages sent or

received by the Link partner of a UCIe die.

Lane

A pair of signals mapped to physical bumps, one for Transmission, and one for

Reception. A xN UCIe Link is composed of N Lanes.

Module

UCIe’s main data path on the physical bumps is organized as a group of Lanes

called a Module. For Standard Package, 16 Lanes constitute a single Module. For

Advanced Package, 64 Lanes constitute a single Module.

UCIe Flit

Mode

Operating Mode where CRC bytes are inserted and checked by the D2D Adapter.

If applicable, Retry is also performed by the D2D Adapter.

UCIe Raw

Mode

Operating Mode where all the bytes of a Flit are populated by the Protocol Layer.

{<SBMSG>}

Sideband message requests or responses are referred to by their names

enclosed in curly brackets. Refer to Chapter 6.0 to see the mapping of sideband

message names to relevant encodings. An asterisk in the <SBMSG> name is

used to denote a group of messages with the same prefix or suffix in their

name.

Reference Documents

Table 2.

Reference Documents

Document

PCI Express® Base Specification

Compute Express Link

Specification

Document Location

https://pcisig.com

https://computeexpresslink.org

Revision History

Table 3 lists the significant changes in different revisions.

UCIe Specification Revision 1.0

Februrary 24, 2022

Property of Universal Chiplet Interconnect Express (UCIe) 2022

13

Universal Chiplet Interconnect express (UCIe)

Specification

Table 3. Revision History

Revision

0.7

Date

January 4, 2022

Description

First release

The following changes were included:

1) Details and support for Retimers

2) Protocol Layer interoperability rules

3) Replaced Optimized mode utilizing Spare Lanes with new

Latency Optimized formats common for Advanced and

Standard packages

0.9

February 6, 2022

4) Support for runtime Link Testing through Parity