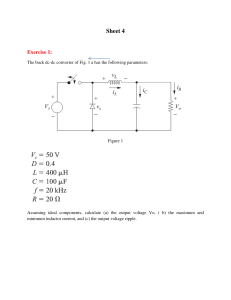

Switch Mode Power Supply (SMPS) Topologies (Part I) - Microchip AN01114a

advertisement