ALU Design with Multiplexers, Latches, and Flip-Flops Lab Report

advertisement

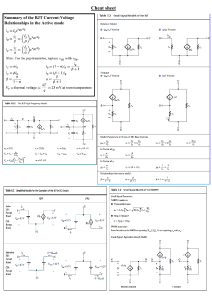

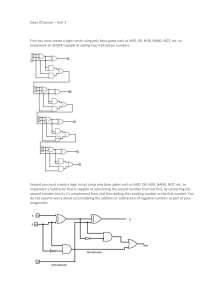

Lab 5 Designing an ALU using Multiplexers. and Latches and Flip-Flops using Digital Gates Lucas Baker 101257583 Introduction In this lab, we designed and implemented an Arithmetic Logic Unit (ALU) using multiplexers. We built latches using digital gates and a 4-bit register using FFs. Gained practical experience in combinational and sequential logic design. Screenshot of the circuit design on Logisim Ex 1: Logging file that shows the inputs and outputs for the circuit Ex 1: Screenshot of the circuit design on Logisim Ex 2.1: Logging file that shows the inputs and outputs for the circuit Ex 2.1: Screenshot of the circuit design on Logisim Ex 2.2: Logging file that shows the inputs and outputs for the circuit Ex 2.2: Questions: 1. Flip-flops change their output when a specific condition on the input is met. Latches, on the other hand, change their output whenever there is a change in the input signal. 2. The D flip-flop captures the value of the D-input at a portion of the clock cycle. That captured value becomes the Q output. At other times, the output Q does not change. The D flip-flop can be viewed as a memory cell, a zero-order hold, or a delay. 3. A Flip Flop that tends to change its state at either a positive edge (rising edge) or negative edge (falling edge) of the clock applied. 4. The output can only be changed at the clock edge, and if the input changes at other times, the output will be unaffected. Hence, the delay. 5. If I were to pick a FF to use for circuit design I would pick the SR FF. It is the most common FF since it is simple and practical. It has set and reset functions that can be implemented in many circuits to be very useful. Conclusion In this lab, we used the logisim software to design and test an ALU using multiplexers, and latches and Flip-Flops using digital gates to further our understanding of the topic. We first designed an ALU with 8 operators and a multiplexer, then an SR latch with nand gates, and then a 4-bit register using d FF with a clock input. Finally, with the input and output values logging files were created that displayed all the values.